# Università degli studi di Udine

# Digital and analog TFET circuits: Design and benchmark

| Original                                                                                                                                                                  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                                                                                                                           |  |  |  |  |  |  |

|                                                                                                                                                                           |  |  |  |  |  |  |

|                                                                                                                                                                           |  |  |  |  |  |  |

| Availability: This version is available http://hdl.handle.net/11390/1145937 since 2019-02-20T18:44:11Z                                                                    |  |  |  |  |  |  |

| Publisher:                                                                                                                                                                |  |  |  |  |  |  |

|                                                                                                                                                                           |  |  |  |  |  |  |

| Published                                                                                                                                                                 |  |  |  |  |  |  |

| DOI:10.1016/j.sse.2018.05.003                                                                                                                                             |  |  |  |  |  |  |

| erms of use: he institutional repository of the University of Udine (http://air.uniud.it) is provided by ARIC services. The im is to enable open access to all the world. |  |  |  |  |  |  |

|                                                                                                                                                                           |  |  |  |  |  |  |

|                                                                                                                                                                           |  |  |  |  |  |  |

| Publisher copyright                                                                                                                                                       |  |  |  |  |  |  |

|                                                                                                                                                                           |  |  |  |  |  |  |

|                                                                                                                                                                           |  |  |  |  |  |  |

|                                                                                                                                                                           |  |  |  |  |  |  |

|                                                                                                                                                                           |  |  |  |  |  |  |

(Article begins on next page)

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: https://doi.org/10.1016/j.sse.2018.05.003

Digital and analog TFET circuits: design and benchmark

S. Strangio<sup>1,2</sup>, F. Settino<sup>1,2</sup>, P. Palestri<sup>1,\*</sup>, M. Lanuzza<sup>2</sup>, F. Crupi<sup>2</sup>, D. Esseni<sup>1</sup>, L. Selmi<sup>1,3</sup>

\* E-mail: pierpaolo.palestri@uniud.it

<sup>1</sup>DPIA, Università degli Studi di Udine, Via delle Scienze 206, I-33100 Udine (UD), Italy.

<sup>2</sup>DIMES, Università della Calabria, Via P. Bucci, 41C, I-87036 Arcavacata di Rende (CS), Italy.

<sup>3</sup>Dipartimento di Ingegneria "Enzo Ferrari", Università degli Studi di Modena e Reggio Emilia, I-41100 Modena, Italy

Abstract

In this work, we investigate by means of simulations the performance of basic digital, analog, and mixed-signal circuits

employing tunnel-FETs (TFETs). The analysis reviews and complements our previous papers on these topics. By

considering the same devices for all the analysis, we are able to draw consistent conclusions for a wide variety of

circuits. A virtual complementary TFET technology consisting of III-V heterojunction nanowires is considered.

Technology Computer Aided Design (TCAD) models are calibrated against the results of advanced full-quantum

simulation tools and then used to generate look-up-tables suited for circuit simulations. The virtual complementary

TFET technology is benchmarked against predictive technology models (PTM) of complementary silicon FinFETs for

the 10 nm node over a wide range of supply voltages  $(V_{DD})$  in the sub-threshold voltage domain considering the same

footprint between the vertical TFETs and the lateral finFETs and the same static power. In spite of the asymmetry

between p- and n-type transistors, the results show clear advantages of TFET technology over FinFET for  $V_{DD}$  lower

than 0.4V. Moreover, we highlight how differences in the I-V characteristics of FinFETs and TFETs suggest to adapt

the circuit topologies used to implement basic digital and analog blocks with respect to the most common CMOS

solutions.

Keywords: Tunnel-FET, TCAD, simulation, digital circuits, analog circuits.

1. Introduction

After the initial report in [1], complementary-metal-oxide-semiconductor (CMOS) transistors based on band-to-band-

tunneling (BtBT), usually referred to as Tunnel-FETs (TFETs), have been extensively explored as possible replacements of, or

complements to, conventional MOSFETs for low-power/low-energy electronic circuits targeting a supply voltage V<sub>DD</sub> below 0.5

V [2][3][4][5]. TFETs embody a promising small slope FET concept able to achieve a subthreshold swing (SS) below the 60

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: <a href="https://doi.org/10.1016/j.sse.2018.05.003">https://doi.org/10.1016/j.sse.2018.05.003</a>

mV/dec room temperature limit of conventional MOSFETs, as demonstrated by many theoretical works based on simulations (see [5] and references therein), and by some recent encouraging experimental results [6][7]. The lower SS compared to a conventional MOSFET can be exploited in two ways: if the threshold voltage is the same as in the MOSFET, the TFET will have a lower off-current (and thus lower static energy dissipation); if instead the same off-current is set in both devices, the TFET will be able to deliver a similar on-current as the MOSFET at a lower supply voltage V<sub>DD</sub>, thus reducing both static and dynamic energy dissipations (which are proportional to  $V_{DD}$  and  $V_{DD}^2$ , respectively). In this respect, circuit simulations have attributed to TFETs the potential to outperform conventional MOSFETs in the ultra-low voltage domain ( $V_{DD} < 0.4 \text{ V}$ ) in both analog [8][9][10] and digital [11][12][13][14][15][16][17] applications. At higher supply voltages, however, the drive current of TFETs is significantly lower than the one of conventional MOSFETs. It is thus clear that TFETs can outperform MOSFETs only if they can deliver an SS significantly smaller than 60 mV/dec over a large current range in the subthreshold region. In many experiments this target has not been achieved, which may be due to fundamental as well as to material and device design issues [18][19][20][21][22][23][24]. As a result, the performance of the fabricated TFETs lags behind the optimistic figures reported in simulation studies, but experimental results have been steadily improving along the years. Another intrinsic advantage of TFETs over conventional MOSFETs stems from the lower temperature dependence of BtBT compared to thermionic emission [56], which may directly translate in less temperature sensitivity of TFET circuits. This has not been observed in early experimental reports about TFETs mainly because the conduction at very low current levels was often dominated by Trap-Assisted-Tunneling (TAT) and Shockley-Read-Hall (SRH) recombination processes [25]. Nevertheless, the fabrication process for TFETs is also getting more and more controlled and encouraging variability analysis are being reported both for statistically meaningful experimental samples [26], and for simulation based studies [27][28].

Among the possible technological platforms, silicon/silicon-germanium TFETs have the advantage of easy integration with mainstream CMOS [25][26][29][30]. However, the achieved performance is not very rewarding, especially for *n*-type TFETs, due to fundamental limit set by the indirect band-gap. As opposite to Si-based devices, TFETs based on heterojunction III-V structures are more promising [6][7][31][32] since they take advantage on their direct (and smaller) energy gap, and in fact they have shown higher on-current as well as SS below 60 mV/dec in the low current range. In addition, III-Vs provide more degrees of freedom for creating hetero-junctions and reduce ambipolar behavior.

The on-current and SS value are not the only important parameters to assess the possible advantages of TFETs against MOSFETs. TFETs are known to have a higher gate-drain capacitance [33], which can result in a switching time penalty compared to MOSFETs due to the Miller effect. On the other hand, the output conductance is lower due to the different electrostatics compared to MOSFETs [8]. Consequently, it is very important and timely to analyze the possible employment of TFETs in relevant benchmarking circuits. The fabrication processes for TFETs are however not as mature as for conventional CMOS transistors, and there exist very few reports about fabrication of TFET circuits (inverters in [25][34], current mirrors in

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: https://doi.org/10.1016/j.sse.2018.05.003

[35], half-SRAM cell in [36]), in many cases employing transistors that are not at the state-of-the-art of TFETs and are based on silicon platforms.

To assess the possible advantages of TFETs versus advanced CMOS transistors in realistic circuits, many simulation works have been presented. Most of such efforts have been devoted to digital circuits. SRAMs, for example, have been analyzed by various authors using different models for the TFETs either calibrated against experimental silicon devices [37] or obtained from full-quantum simulations [38]. Various SRAM topologies to circumvent the unidirectional conduction and/or to improve the cell stability have been also proposed [39][40][41][42][43][44][45][46]. Full-adders have been analyzed in [47][48][49] using look-up-tables (LUTs) obtained from TCAD simulations and calibrated against full-quantum results for hetero-junction

complementary TFETs [50]. Level shifters have been also recently addressed in [50][51].

As for analog circuits, an operational transconductance amplifier (OTA) has been studied in [52], while a 6-bit successive approximation register (SAR) ADC has been simulated in [53] considering complementary double-gate GaSb-InAs heterojunction TFETs. A thorough investigation in [54] analyzed mm-wave low noise amplifiers, oscillators, mixers, rectifiers and detectors using Verilog-A models for the hetero-junction GaSb-InAs TFETs presented in [55]. OTAs, current mirrors and track-and-old circuits based on InAs and GaSb/InAs TFETs have been analyzed in [8] using LUTs built from TCAD simulations calibrated on the device characteristics of [28][32]. Basic analog building blocks (current mirrors, differential pairs, diode-connected transistors) have been simulated in [56] using compact models calibrated on experimental strained silicon TFETs, proposing the deployment of TFETs in niche applications exploiting the lower temperature sensitivity. The performance of track and hold and comparators based on complementary heterojunction TFETs has been assessed in [9]. Different topologies of TFET-based power management circuits for energy harvesting applications have been proposed in [10][57]. Low-dropout linear voltage regulators with III-V TFETs have been analyzed in [58]. In most of these works, the characteristics of the *p*-TFETs are obtained by mirroring the ones of the *n*-TFETs.

In this paper, we present a comparison between aggressively scaled template heterojunction TFETs and FinFETs considering a wide variety of digital and analog/mixed-signal building blocks. The characteristics of the TFETs have been derived from full-quantum simulations [59], where *n*-TFETs and *p*-TFETs have been separately designed and have their own individual characteristics. This work reviews and extends previous publications from our group [9][37][47][48][51] by using the same set of devices for a large variety of circuits and supply voltages, and drawing more general conclusions. Furthermore, differently from the previous papers, the comparison with silicon FinFETs is carried-out at fixed occupied area and absolute off-current, hence essentially at the same static power.

The paper proceeds as follows. The devices and the simulation methodology are described in *Section* 2. Simulation results for digital building blocks such as inverters, full-adders, SRAM cells and level shifters are reported in *Section* 3. Analog/mixed-

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: https://doi.org/10.1016/j.sse.2018.05.003

signal building blocks (op-amps, current mirrors and comparators) are analyzed in Section 4. Conclusions are drawn in Section

5.

# 2. Virtual technology platforms and methodology for simulation and benchmarking

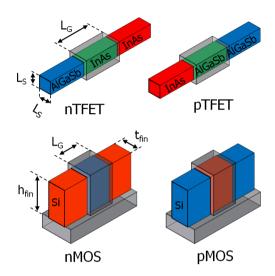

The geometric structures of the p/n-type nanowire (NW) TFETs and silicon FinFETs considered in the following of this work are shown in Figure 1. The considered TFETs belong to a complementary virtual technology in [59], designed and characterized by means of full-quantum simulations. In particular, the AlGaSb/InAs NWs TFETs have a square cross section with a side  $L_S$ =7 nm, a gate length  $L_G$ =20 nm, and an equivalent oxide thickness EOT=1 nm (with a physical oxide thickness of 2.3 nm by considering Al<sub>2</sub>O<sub>3</sub> gate oxide [59]). The FinFET technology used as a benchmark was obtained via the PTM for 10 nm node FinFETs, available at [60]. There are two flavors of such a 10 nm node PTM-FinFETs targeting two different application domains: high-performance (HP) and low-standby-power (LSTP), the latter being the one selected for our analysis. FinFETs have fin height  $h_{fin}$ =21 nm, fin width  $t_{fin}$ =8 nm,  $t_{G}$ =14 nm and EOT= 0.88 nm (physical oxide thickness of 1.2 nm [60]). As for the electrical characteristics, at the nominal  $V_{DD}$  of 750 mV, the n- and the p-FinFET feature a threshold voltage  $V_{th}$  of 425 mV and -428 mV, a saturation on-current  $t_{ON}$  of 44  $\mu$ A and -39.5  $\mu$ A, and an off-current  $t_{OFF}$  of 5.13 pA and -5.08 pA, respectively. Despite the different geometry, the benchmark is fair since the two architectures occupy almost the same area on the wafer under the assumption of having vertical TFET NWs (see for example [7]) and conventional lateral FinFETs. In fact, the physical footprint of a vertical TFET is a square with a total side of 11.6 nm (area ~ 135 nm<sup>2</sup>), considering the semiconductor wire and the surrounding Al<sub>2</sub>O<sub>3</sub> gate oxide. As for a FinFET, the resulting footprint area is ~145 nm<sup>2</sup>, by considering the fin cross section side of 10.4 nm (represented by the channel thickness and the wrapped gate oxide) and  $t_{G}$ =14 nm.

As extensively described in [47][48], the TFETs have been simulated using the TCAD tool Sdevice [61], where the model parameters have been adjusted to reproduce the full-quantum results in [59], which were performed at room temperature. In fact, due to over-simplified models available in commercial TCAD to account for the effects of quantum confinement, the default model parameters are not adequate. Thus, the band-gap parameters for the InAs/AlGaSb heterostructure, i.e. the energy-gap ( $E_G$ ) and the electron affinity ( $\chi$ ), have been chosen so as to reproduce the same band alignment as in [59]. Then, the dynamic nonlocal-path BtBT model parameters for the direct tunneling process ( $A_{path,dir}$  and  $B_{path,dir}$ , see [61]) were recalculated by using the effective masses from bulk GaSb and InAs. Finally, the effective valence and conduction band density of states ( $N_V$  and  $N_C$ ) have been increased compared to the default value for bulk crystals to improve the matching of the I-V curves between TCAD and full-quantum results. The calibrated parameters are summarized in Table I; one should note that these parameters may be interpreted as a fitting deck allowing to reproduce room temperature full-quantum results, while the TCAD predictivity at different temperatures has not been proved due to lack of high temperature simulations in [59]. Our analysis is thus limited to room temperature and does not explore possible advantages of TFETs due to better temperature stability.

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: https://doi.org/10.1016/j.sse.2018.05.003

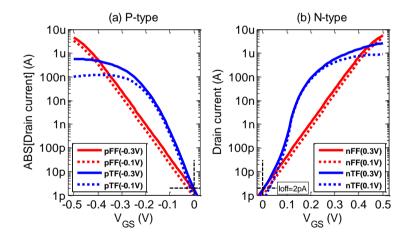

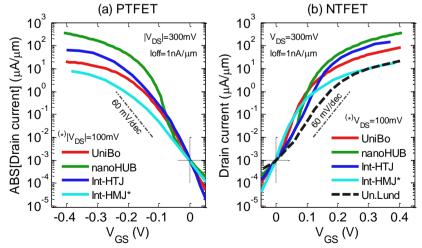

Figure 2 shows the device  $I_D$ - $V_{GS}$  characteristics. The comparison has been performed by aligning both n- and p-type TFETs transfer-characteristics at the same off-current ( $I_{OFF} \sim 2$  pA) as for the FinFETs at  $|V_{DS}| = 0.3$  V (note that all the forthcoming figures will be consistent with this shift, if not otherwise stated). This threshold-voltage alignment is possible by assuming a metal gate work-function of 4.86 eV and 5.03 eV for the p- and n-TFET, respectively. In real devices, both work-functions might be achieved by using a TiN metal gate. This would be possible thanks to the tunability of the TiN work-function [62][63], and considering that the tunable range is between 4.85 and 5.2 eV for a TiN/ $Al_2O_3$  gate stack [64]. Note that we considered the same absolute  $I_{OFF}$  without normalization because the two architectures have very similar footprint. This ensures similar static power for TFETs and FinFETs, although likely different cell layouts when considering lateral and vertical devices may result in different circuit areas.

While the I<sub>D</sub>-V<sub>GS</sub> characteristics of *p*- and *n*-type FinFET in Figure 2 are essentially symmetric at low voltage levels due to similar electrostatics (and SS) and matched I<sub>OFF</sub> (the electron/hole mobility difference does not imply a mismatch between the n-/p-type I<sub>D</sub> in the subthreshold region), the I<sub>D</sub>-V<sub>GS</sub> curves of TFETs are strongly asymmetric. In fact, the design of both p- and n-type TFETs encounters significant criticalities. Due to low density of states (DOS) in the conduction band of III-V materials leading to a degeneracy at relatively low doping levels, the source of the p-TFET cannot be heavily doped in order to preserve a steep SS, but this tends to limit the corresponding maximum on-current [65]: as a result, the *p*-type TFET has four times smaller on-current compared to the *n*-type device. As regards to the *n*-TFET, it suffers from a larger ambipolarity compared to the *p*-TFET. This is due to smaller band-gap of the channel/drain material of the n-TFET (InAs) than the one of the p-TFET (AlGaSb), see Table I, which is more prone to unwanted BtBT at the drain side. Furthermore, this also favors the kink at low V<sub>GS</sub> in the n-TFET that is due to a direct tunneling path between the source and the drain. This tunneling path is weakly controlled by the gate and dominates the current until the source-to-channel tunneling starts to dominate.

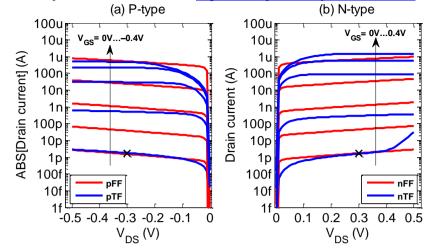

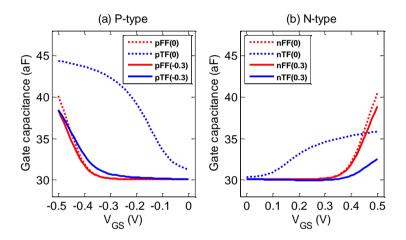

Figure 3 compares the  $I_D$ - $V_{DS}$  characteristics of the devices (with the same threshold-voltage), showing that both p/n-type TFETs have a better saturation compared to FinFETs. This conduction is shown only for  $V_{DS}>0$  ( $V_{DS}<0$ ), while for the opposite polarization a forward biased p-i-n diode-like behaviour takes place (see [36][37] for further details). Figure 4 reports the total gate capacitance ( $C_{GG}$ ), which is the sum of the gate-to-source ( $C_{GS}$ ) and gate-to-drain ( $C_{GD}$ ) capacitances. Note that the PTM-FinFET models include an extrinsic capacitance of about 30 aF equally split between the  $C_{GS}$  and  $C_{GD}$  contributions. For a fair comparison, the same absolute extrinsic  $C_{GS}$  and  $C_{GD}$  capacitances have been added to the  $C_{GD}$  and  $C_{GS}$  extracted from TCAD simulations of the TFETs. It should be noted that the real parasitic capacitance – which can be estimated only after assuming a circuit layout – might be much larger. However, this estimation is beyond the scope of this work since it would require technology parameters and design-rules to be predicted (some effort in this sense has been done in [66][67]). Rather, our main aim is to consider intrinsic devices to focus on more fundamental aspects. In any case, we believe that including at least the contribution already present in the PTM is needed to get not excessively optimistic results.

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: <a href="https://doi.org/10.1016/j.sse.2018.05.003">https://doi.org/10.1016/j.sse.2018.05.003</a>

The I-V and C-V curves for the TFETs simulated with the calibrated TCAD simulation deck are then used to generate dense

LUTs for I<sub>D</sub>, C<sub>GS</sub>, and C<sub>GD</sub> as a function of V<sub>GS</sub> and V<sub>DS</sub>. These LUTs are then imported in the Cadence Virtuoso environment by

means of the Verilog-A description language thus enabling circuit simulations. For the FinFETs instead, we used directly the

spice models in [60].

As a general remark, we want to point out that the device models used in this work do not include traps and other defects

related to immature fabrication processes, and this means that we are considering a "virtual" technology where small SS can be

achieved. On the other hand, NEGF simulations in [59] are quite accurate to describe the tunneling mechanisms at the base of

the TFET behavior. This means that the virtual technology considered here is representative of something that is not available

today, but that is not unrealistic because it requires an evolutionary improvement to devices which can be fabricated today. Thus,

we would like to stress that the results reported in the following of this paper are not restricted to the specific template devices

employed here. In this regard, Figure 5 compares the IV characteristics of the template TFETs used in this work (taken from

[59]) and the ones used for other benchmarking activities based on simulations [14][65][68]. We see that all nTFETs feature

quite similar characteristics. The same applies to the pTFETs, except for the one in [68] that appears to be the mirrored version

of the nTFET. One should also note that the small differences among the reported devices depend on how the normalization of

the current is performed (e.g. the I<sub>D</sub> of our devices has been normalized by the nanowire perimeter, while the current of the other

devices is already normalized since they are obtained by 2D simulations). Furthermore, the I<sub>D</sub>-V<sub>GS</sub> for the InAs homojunction

device in [65] is reported for a lower V<sub>DS</sub> than the others (|V<sub>DS</sub>|=100 mV against 300 mV).

In addition, Figure 5 reports also the experimental IV of the nTFET presented in [7]: the SS and on-current are worse than in the

idealized TFETs used in this work and in [14][68]. However, a detailed TCAD-based analysis of these experimental results has

shown that there is still room for material and device optimization [69], which may improve SS and enable a ten times

improvement of the on-current, that would make it close to the current of our template devices. This is an indication that TFETs

with performance similar to the simulated devices of this work may be manufacturable within a reasonable time frame.

3. Analysis of digital circuits

The circuit-level benchmarking analysis reported in this section focuses on basic digital building blocks implemented with

TFETs. Starting from simple inverter logic-gates, we delve into the details of the design of TFET digital circuits, with emphasis

on how the TFET specific characteristics influence the operation and performance of some relevant building blocks. These

include complementary arithmetic circuits such as the standard 28T full-adder in Section 3.A, access-transistor based memory

cells, such as the Static-RAM (SRAM) in Section 3.B, and hybrid (i.e. comprising both FinFET and TFET devices) digital

voltage conversion blocks such as the level shifters in Section 3.C.

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: <a href="https://doi.org/10.1016/j.sse.2018.05.003">https://doi.org/10.1016/j.sse.2018.05.003</a>

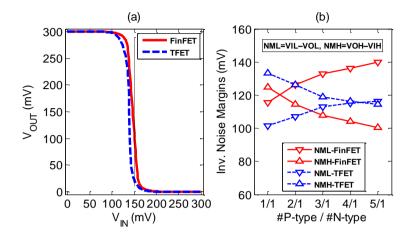

Independent *inverter* gates, together with *fan-out* 4 (FO4) inverters and *5-stage ring oscillators* (RO5), are conventionally representative benchmarks to assess the static and dynamic performance of emerging device technologies for digital applications. In Figure 6a, the voltage transfer characteristics have been reported for both minimum size TFET and FinFET inverters at  $V_{DD} = 300$  mV. As suggested by the drain current characteristics of n/p-type devices in Figure 2 and Figure 3, the asymmetry is more pronounced for the TFETs, whose inverter logic threshold is below  $V_{DD}/2$  (i.e. 150 mV in this case), because the p-TFET is weaker than the n-TFET. This fact is further illustrated by Figure 6b that reports the inverter static noise margins as a function of the p-type to n-type device ratio, considering that a ratio close to 4/1 is needed to compensate for the resulting asymmetry between the NML and NMH (Noise Margins at the Low and High digital levels, respectively) of the TFET inverter, in agreement with the factor of 4 in on-current between n-TFETs and p-TFETs (Figure 2). In any case, the unbalance between the on-current in n- and p-type TFETs leads to a much reduced effect in the NML and NMH than in our previous report [47] since we consider here  $V_{DD} = 300$  mV instead of 400 mV. At this bias, the current of the p-TFET is closer to the one of the n-TFET than at 400 mV. In Figure 5a we see that the voltage gain at the logic threshold is larger in TFET inverters thanks to the higher output resistance (Figure 3).

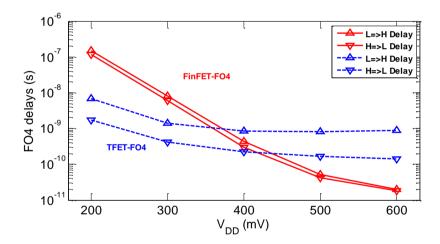

Low-to-high (L $\rightarrow$ H) and high-to-low (H $\rightarrow$ L) FO4 delays are plotted as a function of  $V_{DD}$  in Figure 7. Unlike FinFETs, which have essentially symmetric I-V electrical characteristics for n- and p-type devices and thus symmetric voltage-transfer-characteristics (VTC), asymmetric electrical characteristics of TFETs result in asymmetric rise and fall transitions. Despite such asymmetry, the TFET FO4 delay is shorter than for the FinFET case for  $V_{DD}$  below ~370 mV (~410 mV) if we consider the rise (fall) edge. Furthermore, one should consider that TFET FO4 suffers from miller effect due to large  $C_{GD}$ , but this does not impede the TFETs to become faster than FinFETs at reduced  $V_{DDS}$ , in accordance with their larger on-current and to the fact that the average gain of a logic gate is ~2. Note that  $C_{GD}$  also produces significant overshoots in the voltage waveforms [48].

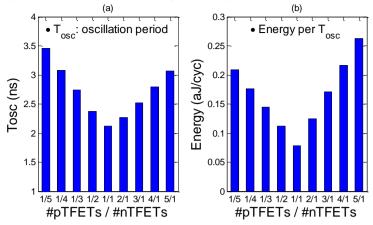

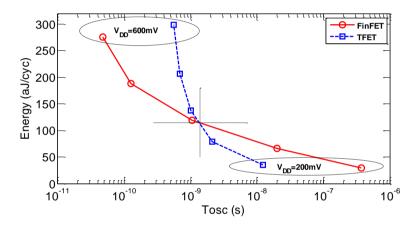

As for the ring-oscillator, we have extracted and examined the oscillation frequency ( $T_{osc}^{-1}$ ) and the energy per cycle.  $T_{osc}$  is correlated with the critical path delay of a generic logic circuit, representing a limit for its maximum operating frequency, whereas the energy per cycle is in turn correlated with the energy per operation ( $E_{op}$ ) when the same digital circuit is operated at the maximum frequency. In Figure 8, we show in (a) the oscillation period ( $T_{osc}$ ) and in (b) the energy per cycle, as a function of the inverter p-type/n-type device ratio. From this plot it is clear that, although symmetric TFET drive-currents improve noise margins, having a small total capacitance (hence a 1/1 ratio) is preferable from a performance and energy consumption perspective. In Figure 9, energy versus  $T_{osc}$  points, as extracted for various  $V_{DD}$  in the range 200~600 mV (step 100 mV), are plotted for both TFET and FinFET ring-oscillators, showing that for time-relaxed applications, the TFETs offer an energy budget saving, which in this case occurs for  $T_{osc} > 1.5$  ns and for energy below 100 aJ/cycle. If we focus on the ultra-low  $V_{DD}$  (e.g. close to 200 mV), there is a very large gain in  $T_{osc}$  for a fixed energy (with a factor > 20 at 30 aJ/cycle energy), while the advantage in terms on energy per cycle for a given  $T_{osc}$  is less relevant (with a factor of  $\sim 2$  for a  $T_{osc} = 1$  ns). The larger current

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: https://doi.org/10.1016/j.sse.2018.05.003

of TFET at low  $V_{DD}$  explains the much smaller propagation delay. On the other hand, the capacitances are quite similar in TFETs and FinFETs (slightly larger for TFETs). As a result, the dynamic energy is almost the same for a given  $V_{DD}$ , with

second order differences due to different capacitance and static energy (the same static power gets integrated over different  $T_{\text{osc}}$ ).

When considering the maximum clock frequency at which a logic-chip can operate, it should be noted that this could be up to 100 times slower than the one extracted for the RO ( $f_{osc} = T_{osc}^{-1}$ ). This means that the frequency range where it would be convenient to use TFETs in place of FinFETs is limited to ~MHz levels and below, as it will be discussed in the next sections. In conclusion, considering that the low SS of TFETs makes them advantageous in the sub-threshold regime, the target applications are the ultra-low-voltage circuits, typical in Internet-of-Things end-nodes [70], which indeed trade the very low power

dissipation with low speed.

A. Full-Adder circuits

Full-adders are fundamental building blocks of many digital systems. To analyze such circuits, transient simulations were performed with a dedicated test-bench on both TFET and FinFET single-bit full adder solutions. To provide a simulation environment with realistic driving signal and loads, the full-adder under test has been placed in a framework including other full-adders and inverters as circuital periphery, as extensively discussed in our previous paper [48]. The extracted delays and energy characteristics are post-processed and translated into figures-of-merit for multi-bit ripple-carry-adders. Trends related to the FinFET and TFET designs are presented and discussed in this section.

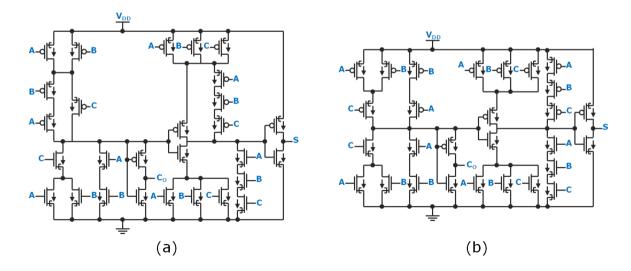

The transistor level schematic of the standard and mirror 28T full-adder topologies are reported in Figure 10 (TFET implementations only). In the mirror topology, the pull-up and pull-down networks are identical rather than complementary [71]. This reduces the current path from 3 to 2 p-type transistors in the carry, and from 4 to 3 p-type transistors in the sum circuit. In particular, due to the asymmetric current conduction of the TFETs, in complementary logic circuits the TFETs are connected so that n-type and p-type devices have respectively a positive and negative  $V_{DS}$ . This configuration prevents the forward biasing of the p-i-n junctions for both n- and p-TFETs.

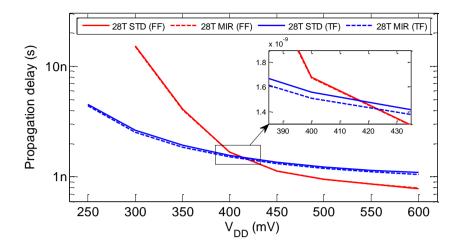

Figure 11 reports the propagation delays of the TFET and FinFET full-adders. The TFET adder shows less speed degradation when  $V_{DD}$  is reduced compared to the FinFET design; this allows the TFET solutions to become faster than its FinFET counterparts for  $V_{DD}$  below ~400 mV. Furthermore, by comparing the results for the mirror topology against the standard one, we see more advantage in terms of propagation delay for the TFET implementation (around 3.5% improvement), while for FinFETs the improvement is around 0.6%. This can be explained considering that the dominant delay is associated to the pull-up chain generating  $\overline{Co}$ , with a higher performance benefit for the TFET adder due to p-/n-device asymmetry.

Besides the obvious consequence that TFET circuits can operate at a higher clock frequency for such reduced  $V_{DD}$ , the smaller speed degradation with  $V_{DD}$  scaling with respect to FinFETs has also implications from the energy point of view. In fact,

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: https://doi.org/10.1016/j.sse.2018.05.003

in the energy balance of a circuit, both static and dynamic energy components can be relevant. In particular, at high  $V_{DD}$  values, the dynamic energy per cycle ( $E_{dynamic} = \alpha \cdot C_{L,eq} \cdot V_{DD}^2$ , where  $\alpha$  is the activity and  $C_{L,eq}$  is the equivalent capacitive load of the circuit) is dominant. On the other hand, when the  $V_{DD}$  is scaled down, a longer  $T_{CLK}$  is needed to accommodate the larger delays, so that the static energy component ( $E_{Static}$  per cycle =  $T_{CLK} \cdot V_{DD} \cdot I_{leak}$ ) can become dominant at lower switching activity. In this regard, it appears clear that having a reduced delay degradation with  $V_{DD}$  scaling would result in reduced static energy consumed

per each operation, for the same static power.

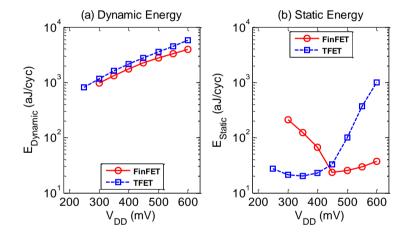

Figure 12 reports the estimated (a) dynamic and (b) static energy per cycle for 32-bit RCAs (each corresponding to 32 blocks of the 28T standard topology in Figure 10a, with either TFETs or FinFETs). The total energy per cycle for TFET and FinFET 32-bit RCAs is reported in Figure 13, by considering various conditions for the activity factor, which is defined as the ratio between the effective input/output switching events and the total clock cycles. When a switching activity close to 1 is considered, the dynamic energy dominates over the static one. Thus, irrespective of the operating voltage, the energy consumption of the FinFET circuit is slightly lower than the one needed for the TFET one. This is due to larger gate capacitance of TFET devices (see Figure 4): in fact, although the same extrinsic capacitance has been assumed in this study and the TFET has a lower  $C_{ox}$  (due to slightly larger EOT), the TFETs have to cope with the intrinsic increase due to Miller effect [33]. On the other hand, when we move toward applications requiring a lower activity (i.e. 50% or below), the static energy contribution becomes more and more relevant in the balance against the dynamic energy. This means that the reduced static energy at lower  $V_{DD}$  for the TFET topology, as reported in Figure 12b, directly translates into a better energy efficiency of the TFETs when low activity applications are considered.

B. 6T SRAM cells

The SRAM cell is widely deployed as on-chip cache in processors, due to its better read and write access times compared to other memory types. As a result, a SRAM array can occupy more than 50% of the processor area. From a topology point of view, the 6T SRAM cell contains two cross-coupled inverters to store the data, and two access-transistors (ATs), to access the data. Thus, the importance of investigating the TFET SRAM cell is twofold: (1) it allows us to benchmark the possible TFET deployment in advanced digital circuits; (2) it is an important case-study to investigate the possible shortcoming of TFET due to their unidirectional conduction.

In recent years, many groups have investigated the impact of the TFET drain current unidirectionality, by assuming conventional 6-transistor (6T) cells with either inward-faced or outward-faced ATs (the outward configuration is sketched in Figure 14), as well as possible alternative topologies. One of the first proposal has been the asymmetric 6T cell based on one inward-AT and one outward-AT [39], which uses a kind of write-assist technique to improve the write stability. Various conditions for read and write assist protocols have been investigated in [40], with emphasis on a symmetric 6T cell with p-type

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: <a href="https://doi.org/10.1016/j.sse.2018.05.003">https://doi.org/10.1016/j.sse.2018.05.003</a>

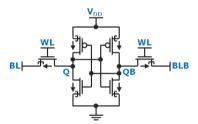

inward-ATs and read-assist. Afterwards, a 7T cell based on a conventional outward-AT 6T cell and one additional transistor for the read has been proposed in [41] (the same topology has been recently re-considered in [46] by simulating a different set of TFET templates). Robust topologies with more than 6 transistors have been proposed to improve the cell stability against device variations, such as the 10T Schmitt-Trigger cells in [42][43], the 7T driverless cell in [44] and the 8T hybrid TFET/CMOS cell in [45]. The most recent proposal is the 7T cell based on unconventional connections of the ATs to the bit-lines (BLs) and word-line (WL) in [38] (source and drain of the AT connected to the WL and BL, respectively), with the purpose to improve the cell stability and reduce the minimum operating  $V_{DD}$ . In our previous report [37], we have demonstrated that the simple 6T SRAM cell can work without severe performance penalty with respect to more complex cells (e.g. the 8T cell), provided that (1) outward-ATs are used and (2) the bit-lines (BLs) are pre-charged to  $V_{DD}/2$  for the read operation.

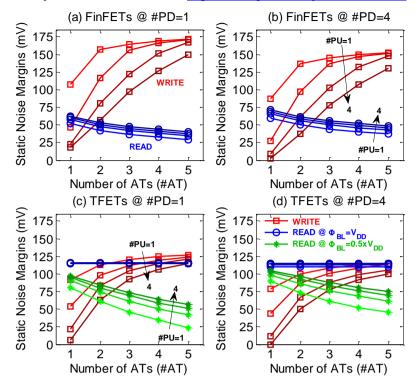

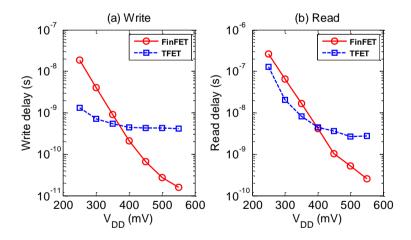

The static performance of the 6T SRAM cell is analyzed in Figure 15, which reports the static noise margins in both read (RSNM) and write (WSNM) operations, for (a and b) FinFET and (c and d) outward-AT TFET 6T SRAM cells. These static noise margins are plotted as a function of the effective width of the AT (x-axis), of the pull-up transistor (different curves in the same plot) and of the pull-down transistor (plots on the left against the ones on the right), obtained by assuming multiple parallel transistors. When considering symmetric transistors as the FinFETs (Figure 15, a and b), the write-ability of a cell mainly improves by decreasing the pull-up ratio, defined as the ratio between the effective width of pull-up transistors and the width of the ATs. As for the read-ability, this can be mainly improved by increasing the cell ratio, which is defined as the ratio between the effective width of pull-down transistors and the width of the ATs. In a few words, a trade-off between read and write operations is required to achieve a correct sizing of an SRAM cell: the larger the ATs, the lower is the RSNM and the larger is the WSNM (see for example Figure 15a). On the other hand, when considering unidirectional transistors as the TFETs (Figure 15, c and d), RSNM results to be independent on the overall AT size. This fact has been already discussed in [37], with the conclusion that the read is in fact forbidden due to unidirectional conduction of outward-faced ATs, which prevents the access to the cell in read-mode (i.e. despite quite large RSNM, the corresponding read operation is too slow). For this reason, we report also the case when read is performed with a pre-charge of the BLs to V<sub>DD</sub>/2, while keeping the standard write protocol with differential voltage levels to 0V and V<sub>DD</sub> at the two BLs. In this case, at the beginning of the read operation, the BL voltage levels are between 0 and  $V_{DD}$ , and thus at least one of the AT is operated at positive  $V_{DS}$  (i.e. the one at the side where the '1' logic value is stored), so that the BL capacitance is charged toward V<sub>DD</sub> in a reasonable time. In Figure 16, we report the (a) write and (b) read delays for both FinFET and TFET SRAM cells as a function of V<sub>DD</sub>. As regards the write delay, the TFET SRAM cell becomes faster than the corresponding FinFET cell at V<sub>DD</sub> below ~360 mV. A similar trend is also obtained for the read delay, where the TFET SRAM cell becomes faster at  $V_{DD}$  below ~400 mV. It is important to remark that the read of the TFET cell has been performed by pre-charging the BLs to half  $V_{DD}$ , and this makes the TFETs competitive with FinFETs at such ultra-scaled V<sub>DD</sub> values, despite the unidirectionality of TFETs. As for the FinFET cell, this pre-charge scheme does not

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: https://doi.org/10.1016/j.sse.2018.05.003

bring any significant improvement to the read delay because FinFETs are bidirectional. Read and write delay transient simulations have been performed by assuming a BL parasitic capacitance of 20 fF, to account for interconnect parasitic capacitance as well as for input capacitances of ATs belonging to other cells in the same array.

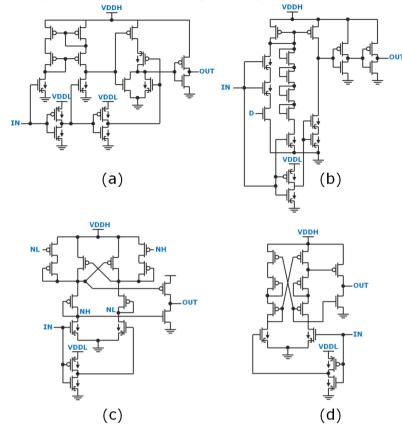

### C. Level shifters

Level shifter (LS) circuits are required in multi-supply voltage designs to up-convert digital signals from the lower (V<sub>DDL</sub>) to the higher (V<sub>DDH</sub>) power supply domain. A key requirement of this class of circuits is to perform fast and energy efficient conversion for a wide range of input voltages. In this context, a hybrid MOSFET/TFET approach has been proposed in [51] showing significant improvement over pure MOSFET and TFET designs. The same hybrid MOSFET/TFET LS application has been investigated in [50], with more focus on the layout density reduction (e.g. by using single non complementary input data signal, i.e. with a single input-stage inverter). Although the co-integration of such two technologies in the same chip would be challenging, due to different device concepts (TFET and CMOS) and different material schemes (III-V materials and silicon), some encouraging result has been already shown in the literature, such as the TFET and CMOS devices co-integrated with the same process flow in [30], as well as the hybrid integration of III-V and Si(Ge) CMOS devices in [72]. In this context, a lot of effort is being devoted to enable heterogeneous integration of very different technologies [73][74], and we may consider the further challenge to integrate vertical and lateral device architectures.

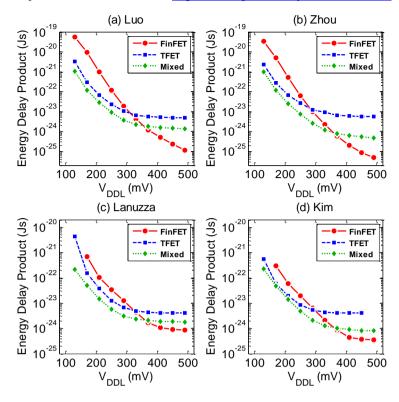

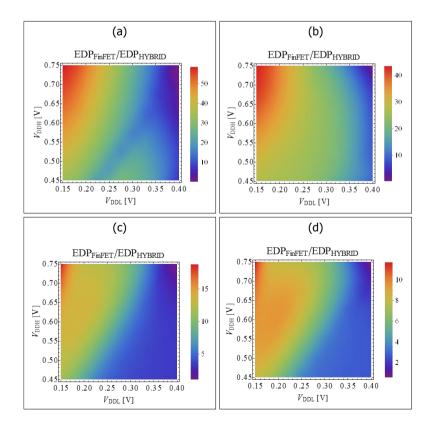

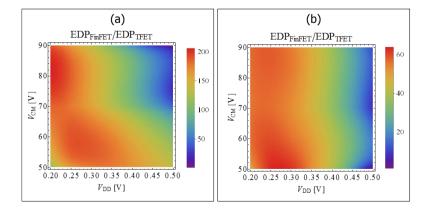

The four LS topologies depicted in Figure 17 (only hybrid FinFET/TFET designs), as proposed in [75][76][77][78], are analyzed in terms of energy delay product (EDP) considering different  $V_{DDL} \rightarrow V_{DDH}$  signal up-conversions. In particular, the pure FinFET LS designs have been sized in order to achieve the minimum EDP for the target conversion 0.25 V  $\rightarrow$  0.75 V (note that 0.75 V is the nominal operating voltage of the considered FinFET technology), for 1 MHz input waveform. As regards the pure TFET and hybrid designs, similar leakage currents per circuit block are ensured by employing the same number of devices. The simulated EDP results as a function of  $V_{DDL}$ , for up-conversion to  $V_{DDH} = 0.75$  V, are reported in Figure 18 showing that for  $V_{DDL}$  below 0.4 V the hybrid FinFET/TFET approach outperforms both pure FinFET and TFET implementations, regardless of the considered circuit configuration. Thus, by employing TFETs as the transistors operating at  $V_{DDL}$  while keeping the FinFETs for the  $V_{DDH}$  operation, one can guarantee a sufficient pull-down network strength even at relatively low voltage input signals. This allows reduced current contention among pull-up (p-FinFETs) and pull-down (n-TFETs) devices in critical up-conversion operations (i.e. when  $V_{DDL}$  is extremely low) with a positive impact on the low-to-high delay, on the corresponding short circuit current and thus on the energy consumption. This twofold advantage in terms of delay and energy is well highlighted in Figure 19, which shows the EDP ratio between FinFET and hybrid implementations for  $V_{DDL}$  ranging from 0.15 to 0.4 V and  $V_{DDH}$  in the range from 0.45 to 0.75 V. Similar trends are observed for all the hybrid designs, pointing out that the larger is the voltage up-conversion ratio the larger is the EDP improvement compared to the corresponding FinFET counterparts.

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: <a href="https://doi.org/10.1016/j.sse.2018.05.003">https://doi.org/10.1016/j.sse.2018.05.003</a>

### 4. Analog/mixed-signal applications

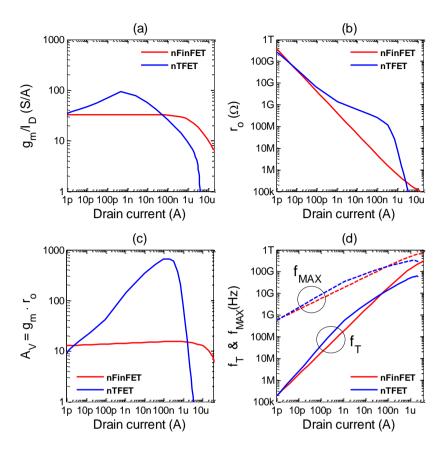

This section focuses on benchmarking the same TFET and FinFET technology platforms described above, by moving to analog and mixed-signal domains. In fact it is the most common situation in system-on-chips (SoCs) that the dominant digital part dictates the device specs and the analog circuit design simply adopts them and tries to use the existing devices at best. The circuit-level performances are dictated by the device-level figures-of-merit (FOM), such as the transconductance efficiency  $(g_m/I_D)$ , output resistance  $(r_0)$ , intrinsic gain  $(A_v)$  and cut-off frequency and maximum oscillation frequency  $(f_T \text{ and } f_{MAX})$ . The comparison for n-type devices is reported in Figure 20, the one for p-type devices in Figure 21. TFETs exhibit significant advantages over FinFETs for low current level (below ~1 µA) in terms of g<sub>m</sub>/I<sub>D</sub> with a peak value around I<sub>D</sub> = 1 nA for n-TFET and around 10 pA for p-TFET. The better saturation behavior of TFET devices (Figure 3) results in a significantly higher r<sub>0</sub> compared to FinFETs in the current range  $1n\sim1\mu$ A for *n*-TFET and  $10p\sim100$  nA for *p*-TFET. The output resistance affects also the intrinsic gain, which is 100 times or 10 times larger for respectively the n-TFET or p-TFET compared to the corresponding FinFET at I<sub>D</sub> of about 100 nA. TFETs outperform FinFETs also in terms of f<sub>T</sub> with an improvement of approximately a factor 2 occurring around 1 nA for n-TFET and around 10 pA for p-TFET. On the other hand, for current levels larger than 80 nA (20 nA) for the n-type (p-type) devices, the FinFETs reach larger f<sub>T</sub> peaks, e.g. 100 GHz in the 1μA range. One should however consider that these values have been computed for intrinsic devices, while the inclusion of layout parasitics would likely result in lower  $f_T$  peaks. In the same figure, the maximum oscillation frequency  $f_{MAX}$  is also reported, with similar trends as for the  $f_T$  (but different absolute values).

Overall, because of the asymmetric characteristics of TFETs, the n-type device exhibits larger improvements in terms of  $r_0$  and  $A_v$  (about a factor 10) with respect to the p-type one when compared to FinFET counterpart, with the peak values of the  $g_m/I_D$  and  $f_T$  (and  $f_{MAX}$ ) curves being shifted at lower current levels for p-type TFET. Based on these key FOMs, the potential of conventional topologies for TFET design is investigated and discussed in comparison to more complex CMOS low-voltage design topologies, considering some relevant analog/mixed signal building blocks such as *Current Mirror* in *Section 4.A*, *Operational Amplifier* in *Section 4.B* and *Comparator* in *Section 4.C*.

A similar benchmarking study for the main analog FOMs of several building blocks (such as operational transconductance amplifier, track-and-hold, current mirror, differential pair, diode connected transistor) has been presented in two recent works [8][56]. In [8] two 14-nm node III–V TFETs (homo-junction InAs and hetero-junction GaSb-InAs) with a gate-length of 20 nm are compared with a Si MOSFET, while in [56] the 28-nm homo-junction strained-silicon (sSi) double-gate (DG) TFET is systematically benchmarked against the 28-nm low-power Fully Depleted Silicon on Insulator (FD-SOI) CMOS node. Significant advantages have been shown for low-to-moderate current densities both at device and circuit levels, highlighting the potential of conventional topology for TFET design compared to CMOS design which instead requires more complex topologies to achieve similar performance in low-voltage design.

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: https://doi.org/10.1016/j.sse.2018.05.003

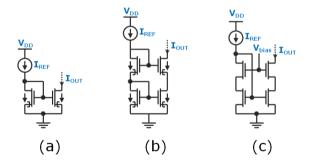

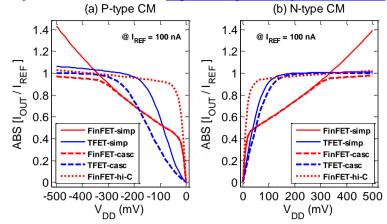

#### A. Current Mirror

In the context of analog design, current mirrors are required to generate a replica of a given current reference, that corresponds to the implementation of a current controlled current source. Their most important figure-of-merit is the output resistance, which is required to be sufficiently high to deliver an almost constant output current over a wide range of output voltages. Several topologies of current mirrors have been proposed and the selection of the most appropriate topology depends on the adopted technology [79]. An experimental comparison of TFET and FinFET current mirrors is reported in [35] in which the ability of the simple topology in mirroring the reference current is analyzed, showing a reduced sensitivity of TFET design to channel length variation compared to FinFET implementation. In the following, we have analysed the simple, the cascode and the high-compliance mirror topologies sketched in Figure 22, by considering a reference current (I<sub>REF</sub>) of 100 nA where the TFET r<sub>0</sub> is close to highest compared to the FinFET one. Figure 23 reports the ratio between the output current (I<sub>OUT</sub>) and I<sub>REF</sub> as a function of the output voltage (V<sub>OUT</sub>). As for the FinFET designs, it can be seen that: (i) the simple circuit has a strong sensitivity to V<sub>OUT</sub>, which practically impedes the proper operation of the mirror; (ii) the cascode solution shows the drawback of a high minimum output voltage (V<sub>OUTmin</sub>); the FinFET high-compliance topology allows to achieve a good performance in terms of low sensitivity to V<sub>OUT</sub> and low V<sub>OUTmin</sub>, but it requires additional biasing circuitry, resulting in a significant area penalty. As for the TFET designs, the significantly higher output resistance makes the simple current mirror have similar mirroring performance compared to the FinFET high-compliance architecture. The TFET cascode implementation allows for a slight improvement in keeping the  $I_{OUT}/I_{REF}$  ratio close to one, but at the expenses of higher  $V_{OUT_{min}}$  because of the delayed onset of the saturation region in TFETs compared to FinFETs. The important conclusion is thus that the TFET-based design has the potential to significantly reduce the circuit complexity of a low-voltage current mirror, without significantly affecting the performance.

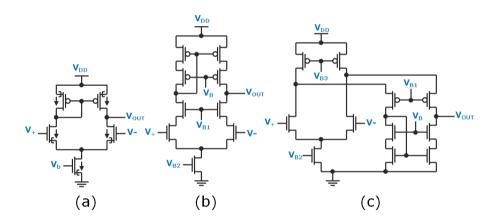

## B. Operational Amplifier

The design of operational amplifier with sub-1V operation poses several challenges, mainly due to the speed-limiting factor associated to the reduced current level in sub-threshold operation [80][81]. The circuit performance can be predicted by applying the  $g_m/I_D$  design methodology [82] which has been extensively reviewed in [83] for TFET designs. The results obtained from current mirrors hint to the potential of TFET implementation for low voltage operational amplifiers. The simple, the telescopic cascode and the folded cascode operational amplifier topologies (see Figure 24), implemented with TFETs and FinFETs, are compared in terms of DC gain and of the figure-of-merit FOM<sub>GBW</sub> (defined as  $\frac{GBW \times C_{load}}{I_{BIAS}}$ ) [80], which provides a fair comparative evaluation of the bandwidth-power consumption trade-off. The circuits are designed for the target unity gain frequency of 50 MHz at  $V_{DD} = 0.5$  V and under the same load condition,  $C_{load} = 1$  fF. Table II reports the DC gain as well as the FOM<sub>GBW</sub> values, which are basically a measure of the power consumption because the circuits are compared for the same GBW

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: <a href="https://doi.org/10.1016/j.sse.2018.05.003">https://doi.org/10.1016/j.sse.2018.05.003</a>

and  $C_{load}$ . As a consequence of the combined effect of higher output resistance of the active load and higher  $g_m/I_d$  at lower current level, for the simplest topology the TFETs implementation allows to achieve significantly higher performance compared to its FinFET counterpart in terms of DC gain and at a lower power consumption. The cascode solutions (folded or telescopic cascode) are required for FinFET design in order to compete with the gain of the TFET simple circuit, but at the expense of reduced output swing, higher power consumption and increased silicon area. For the same circuit topology, TFETs show

improvements over FinFETs in the order of a factor of 2 in terms of both performance and power.

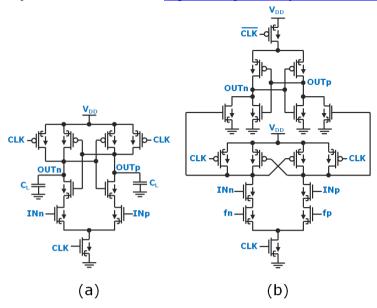

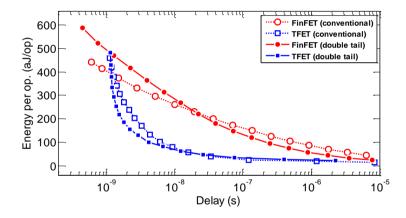

C. Comparators

In the context of analog-to-digital conversion, dynamic regenerative comparators are required for fast and energy efficient operation. Thanks to the higher transconductance efficiency at lower current level, TFET designs could enable significant power saving compared to FinFET ones. The conventional and double tail [84] architectures sketched in Figure 25 are compared in terms of energy and delay. The FinFET designs have been sized according to a progressive sizing methodology for stacked transistors, while TFET designs have been sized in order to keep approximately the same static current consumption as their FinFET counterparts. The simulation setup consists of 5 mV differential input (V<sub>d</sub>) with an input common mode (V<sub>CM</sub>) of 70% V<sub>DD</sub> and a load capacitance (C<sub>L</sub>) of 1 fF, which corresponds approximately to the effective input capacitance of 10 parallel minimum-size FinFET inverters. The FinFET-based double tail topology enables a significant boost of the speed in comparison to the conventional design at the expense of higher energy per operation (obtained considering the minimum clock period at each V<sub>DD</sub>), as depicted in Figure 26. As for the TFET designs, the conventional architecture has comparable performance to the double tail in terms of speed while keeping lower energy per operation  $(E_{op})$ , because of the asymmetric characteristic of p- and n-type TFETs. Thus, the TFET-based conventional structure appears to be the best option compared to both the FinFET-based designs, also due to the reduced number of devices compared to the more complex double tail structure. Furthermore, considering a TFET-base design, a reduced V<sub>CM</sub> value allows for an extended range of V<sub>DD</sub> where TFET-based comparators outperform their FinFET counterparts as reported in Figure 27, in which the EDP is plotted as a function of V<sub>DD</sub> for different values of V<sub>CM</sub> ranging from 50% to 90% of V<sub>DD</sub>.

5. Conclusions

This work has provided an overview of TFET circuit applications, along with a detailed benchmark against aggressively scaled FinFETs, carried out by touching a large variety of circuit domains including digital, analog and mixed-signal building blocks. The virtual TFET technology platform consists of III-V heterojunction NWs, designed through advanced full-quantum simulators in [59], while the predictive technology model (PTM) platform of 10 nm node FinFETs was used as representative of the CMOS counterpart [60]. For a fair comparison, TFET and FinFET blocks have been operated at approximately the same

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: https://doi.org/10.1016/j.sse.2018.05.003

static power density consumption that is at fixed area occupation and off-current. Unlike FinFETs, the considered TFETs feature

asymmetric p- versus n-type transistors drain current characteristics, as actually the case in several experimental reports.

Highlights related to the **digital domain**:

• Basic blocks (inverters, FO4 and ring-oscillators). Symmetric VTC can be achieved with TFETs at the cost of

using ~4 p-type parallel devices for each n-type, to implement the pull-up and pull-down network, respectively.

This is not the case for FinFET inverters, whose VTC is almost symmetric even considering a 1/1 p/n ratio. The

large capacitance and area occupation compared to FinFETs due to the number of pull-up TFET devices, leads to

larger energy consumption without providing a real performance advantage. Thus, by considering minimum size

inverters, 5-stages ring-oscillator benchmark-vehicle demonstrated a better energy efficiency of TFETs only in

applications with time constants below ~1 ns, e.g.: if FinFETs are replaced by TFETs, the energy per cycle is

approximately halved for a Tosc of ~10 ns.

Arithmetic circuits (full-adders). The standard 28 transistors implementation of 1-bit full-adder has been used as a

benchmark for the logic/arithmetic domain. The carry-in to carry-out propagation delay has been selected as the

main performance figure-of-merit: TFET full-adder turned out to be faster than the corresponding FinFET

implementation for  $V_{DD}$  below ~400 mV. When considering multi-bit adders such as the 32-bit ripple carry adder

implemented with a chain of 32 1-bit full-adder blocks, similar energy consumption is found when TFET and

FinFET solutions are operated at the same  $V_{\text{DD}}$ , if a 100% switching activity is assumed. However, when moving

toward applications featuring a limited switching activity (e.g. <10%), the TFET circuits allow energy saving at low

V<sub>DD</sub> (i.e. below 400 mV), which corresponds to the regime where the static energy becomes relevant, and moreover

they can be operated at a lower minimum energy point. In fact, irrespective of similar active power, in that regime

the same operation can be performed in a reduced time if TFETs are employed.

Memory cells (SRAM). We have considered a standard 6T Static-RAM memory block as a test vehicle for

memory cells based on TFETs. Due to unidirectional conduction, the TFET access-transistors have been oriented in

the outward configuration by connecting the source to the BLs. The sizing of the cell transistors has been optimized

for each V<sub>DD</sub> in order to enable functional hold, read and write operation for both TFET and FinFET SRAMs.

Irrespective of the unidirectional limit, the outward-faced access-transistors TFET SRAM leads to competitive read

and write delays at scaled supply voltage (<400 mV)., when it is operated with a BL pre-charge at  $V_{DD}/2$  during the

read phase.

• Voltage up-converters (level-shifter). The potentialities of TFET devices have been exploited in the

implementation of hybrid TFET/FinFET level-shifters, where TFET devices are introduced in the low supply circuit

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: <a href="https://doi.org/10.1016/j.sse.2018.05.003">https://doi.org/10.1016/j.sse.2018.05.003</a>

sections for efficient voltage up-conversion from the ultralow-voltage regime. The mixed solution exhibits superior dynamic performance at the same static power consumption than both pure MOSFET and pure TFET solutions. The same behaviour has been found on four different topologies, thus confirming that the mixed TFET–MOSFET approach is intrinsically suitable for such application.

## Highlights related to the analog/mixed-signal domain:

- Basic analog device level figures-of-merit. TFETs exhibit significantly higher maximum values for the transconductance efficiency  $g_m/I_D$  and intrinsic voltage gain  $A_{Vi} = g_m \cdot r_o$  (up to almost two decades for n-type and one decade for p-type) than FinFETs, mainly due to their higher output resistance at low current levels. The  $f_T$  of TFETs is slightly higher than that of FinFETs at low current levels (a higher advantage is observed for the n-type device), while it is significantly lower at high current levels, mainly due to the corresponding transconductance behaviour. As regards the TFET output resistance,  $r_o$  is larger than the one of FinFETs for currents in the  $\mu A$  range, while they tend to be similar for very low current levels.

- Current mirrors. The large output resistance of TFETs can be conveniently exploited in the design of current mirrors, considering that they require a high output resistance to deliver an almost constant output current against output voltage variations. When compared to a FinFET implementation, TFET-based design has the potential to significantly reduce the circuit complexity of a low-voltage current mirror, without any significant performance loss.

- Operation Amplifier. The capability of simple TFET design to perform with comparable performance of more

complicated FinFET implementations has been demonstrated also for the operational amplifiers, where the simple

TFET operation amplifier shows both DC and AC figures-of-merit comparable with the folded and telescopic

cascode FinFET operation amplifiers, while featuring a reduced power consumption.

- Comparators. TFET-based comparators (both conventional and double tail architectures) allow for better energy-delay-product in the ultra-low voltage regime for a large swing of the common-mode input voltage and V<sub>DD</sub>, up to an EDP better than 200 and 60 times for the conventional and double tail implementations, respectively. Furthermore, the TFET-based conventional topology offers similar EDP performance compared to the more complex double tail topology, basically because of the lower sensitivity to the asymmetric characteristic of *p/n*-type TFETs, enabling potential area saving.

From a general perspective, the key messages of this study are:

• the pros (i.e. low subthreshold swing and high output resistance) and cons (i.e. ambipolarity, unidirectionality, p-versus n-type asymmetry, large gate-to-drain intrinsic capacitance, higher sensitivity to variability sources) of

## $\ensuremath{\mathbb{C}}$ 2018. This manuscript version is made available under the CC-BY-NC-ND 4.0 license

http://creativecommons.org/licenses/by-nc-nd/4.0/

The final publication is available at: https://doi.org/10.1016/j.sse.2018.05.003

TFETs with respect to MOSFETs can be balanced at best by adopting new circuit topologies with respect to standard CMOS solutions;

- while research on TFETs focuses mostly on switches for digital circuits, TFETs exhibit potential interesting

advantages also for analog and mixed-signal applications; these advantages might be emphasized in niche

applications, by exploiting the low-temperature dependence of TFET operation.

- the introduction of TFET in mainstream CMOS technologies will likely be limited to electronic systems operating at extremely reduced voltage (lower than 400 mV) and by preferentially adopting an hybrid TFET/MOSFET implementation, which takes advantage of both transistor options. At such small voltages, (time dependent) variability may end up being the most stringent requirement dictating the application window of such technology.

## Acknowledgment

The research leading to these results has received funding from the European Community's Seventh Framework Programme under grant agreement No. 619509 (project E2SWITCH).

#### References

- [1] William M. Reddick and Gehan A. J. Amaratunga, "Silicon surface tunnel transistor", Appl. Phys. Lett. 67, 494, 1995.

- [2] A. Seabaugh and Q. Zhang, "Low-Voltage Tunnel Transistors for Beyond CMOS Logic", Proceedings of the IEEE, vol. 98, no. 12, pp. 2095 –2110, Dec. 2010.

- [3] A. Ionescu and H. Riel, "Tunnel field-effect transistors as energy efficient electronic switches", Nature, vol. 479, no. 73, pp. 329–337, 2011.

- [4] H. Lu and A. Seabaugh, "Tunnel Field-Effect Transistors: State-of-the-Art", IEEE Journal of Electron Devices Society, vol. 2, no. 4, pp. 44–49, 2014.

- [5] D.Esseni, M.Pala, P.Palestri, C.Alper, T.Rollo, "A review of selected topics in physics based modeling for tunnel field-effect transistors", Semiconductor Science and Technology, Volume 32, Number, p. 083005, 2017.

- [6] R. Pandey, H. Madan, H. Liu, V. Chobpattana, M. Barth, B. Rajamohanan, M. J. Hollander, T. Clark, K. Wang, J- H. Kim, D. Gundlach, K. P. Cheung, J. Suehle, R. Engel-Herbert, S. Stemmer, S. Datta, "Demonstration of p-type In0.7Ga0.3As/GaAs0.35Sb0.65 and n-type GaAs0.4Sb0.6/In0.65Ga0.35As complimentary Heterojunction Vertical Tunnel FETs for ultra-low power logic", 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, 2015, pp. T206-T207.

- [7] E. Memisevic, J. Svensson, M. Hellenbrand, E. Lind and L. E. Wernersson, "Vertical InAs/GaAsSb/GaSb tunneling field-effect transistor on Si with S = 48 mV/decade and Ion = 10  $\mu$ A/ $\mu$ m for Ioff = 1 nA/ $\mu$ m at Vds = 0.3 V", 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 2016, pp. 19.1.1-19.1.4.

- [8] B. Sedighi, X. S. Hu, H. Liu, J. J. Nahas and M. Niemier, "Analog Circuit Design Using Tunnel-FETs", IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 62, no. 1, pp. 39-48, Jan. 2015.

- [9] F. Settino, M. Lanuzza, S. Strangio, F. Crupi, P. Palestri, D. Esseni, L. Selmi, "Understanding the Potential and Limitations of Tunnel FETs for Low-Voltage Analog/Mixed-Signal Circuits", IEEE Transactions on Electron Devices, vol. 64, no. 6, pp. 2736-2743, June 2017.

- [10] D. Cavalheiro, F. Moll and S. Valtchev, "TFET-Based Power Management Circuit for RF Energy Harvesting", IEEE Journal of the Electron Devices Society, vol. 5, no. 1, pp. 7-17, Jan. 2017.

http://creativecommons.org/licenses/by-nc-nd/4.0/

- [11] D. Esseni, M. Guglielmini, B. Kapidani, T. Rollo and M. Alioto, "Tunnel FETs for Ultralow Voltage Digital VLSI Circuits: Part I—Device-Circuit Interaction and Evaluation at Device Level", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 22, no. 12, pp. 2488-2498, Dec. 2014.

- [12] M. Alioto and D. Esseni, "Tunnel FETs for Ultra-Low Voltage Digital VLSI Circuits: Part II–Evaluation at Circuit Level and Design Perspectives", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 22, no. 12, pp. 2499-2512, Dec. 2014.

- [13] D. H. Morris, U. E. Avci, R. Rios and I. A. Young, "Design of Low Voltage Tunneling-FET Logic Circuits Considering Asymmetric Conduction Characteristics", IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 4, no. 4, pp. 380-388, Dec. 2014.

- [14] U. E. Avci, D. H. Morris and I. A. Young, "Tunnel Field-Effect Transistors: Prospects and Challenges", IEEE Journal of the Electron Devices Society, vol. 3, no. 3, pp. 88-95, May 2015.

- [15] J. Núñez and M. J. Avedillo, "Comparative Analysis of Projected Tunnel and CMOS Transistors for Different Logic Application Areas", IEEE Transactions on Electron Devices, vol. 63, no. 12, pp. 5012-5020, Dec. 2016.

- [16] J. Núñez and M. J. Avedillo, "Comparison of TFETs and CMOS Using Optimal Design Points for Power–Speed Tradeoffs", IEEE Transactions on Nanotechnology, vol. 16, no. 1, pp. 83-89, Jan. 2017.

- [17] L. Guo et al., "Benchmarking TFET from a circuit level perspective: Applications and guideline", 2017 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-4, Baltimore, MD, USA, 2017.

- [18] S. Sant, K. Moselund, D. Cutaia, H. Schmid, M. Borg, H. Riel, and A. Schenk, "Lateral InAs/Si p-Type Tunnel FETs Integrated on Si -Part 2: Simulation Study of the Impact of Interface Traps", IEEE Trans. on Electron Devices, vol. 63, no. 11, pp. 4240–4247, Nov 2016.

- [19] A. Walke, A. Vandooren, B. Kaczer, A. Verhulst, R. Rooyackers, E. Simoen, M. M. Heyns, V. R. Rao, G. Groeseneken, N. Collaert, and A. V.-Y. Thean, "Part II: Investigation of Subthreshold Swing in Line Tunnel FETs Using Bias Stress Measurements", IEEE Trans. on Electron Devices, vol. 60, no. 12, pp. 4065–4072, 2013.

- [20] S. Agarwal and E. Yablonovitch, "Band-Edge Steepness Obtained From Esaki/Backward Diode Current-Voltage Characteristics", IEEE Transactions on Electron Devices, vol. 61, no. 5, pp. 1488-1493, May 2014.

- [21] D. Esseni, M. G. Pala and T. Rollo, "Essential Physics of the OFF-State Current in Nanoscale MOSFETs and Tunnel FETs", IEEE Transactions on Electron Devices, vol. 62, no. 9, pp. 3084-3091, Sept. 2015.

- [22] U. E. Avci, B. Chu-Kung, A. Agrawal, G. Dewey, V. Le, R. Rios, D. H. Morris, S. Hasan, R. Kotlyar, J. Kavalieros, I. A. Young, "Study of TFET non-ideality effects for determination of geometry and defect density requirements for sub-60mV/dec Ge TFET", 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, 2015, pp. 34.5.1-34.5.4.

- [23] M. G. Pala and D. Esseni, "Interface Traps in InAs Nanowire Tunnel-FETs and MOSFETs—Part I: Model Description and Single Trap Analysis in Tunnel-FETs", IEEE Transactions on Electron Devices, vol. 60, no. 9, pp. 2795-2801, Sept. 2013.

- [24] D. Esseni and M. G. Pala, "Interface Traps in InAs Nanowire Tunnel FETs and MOSFETs—Part II: Comparative Analysis and Trap-Induced Variability", IEEE Transactions on Electron Devices, vol. 60, no. 9, pp. 2802-2807, Sept. 2013.

- [25] L. Knoll, Q.-T. Zhao, A. Nichau, S. Trellenkamp, S. Richter, A. Schäfer, D. Esseni, L. Selmi, K. K. Bourdelle, S. Mantl, "Inverters With Strained Si Nanowire Complementary Tunnel Field-Effect Transistors", IEEE Electron Device Letters, vol. 34, no. 6, pp. 813-815, June 2013.

- [26] Q. Huang, R. Jia, C. Chen, H. Zhu, L. Guo, J. Wang, J. Wang, C. Wu, R. Wang, W. Bu, J. Kang, W. Wang, H. Wu, S.-W. Lee, Y. Wang, R. Huang, "First foundry platform of complementary tunnel-FETs in CMOS baseline technology for ultralow-power IoT applications: Manufacturability, variability and technology roadmap", Proc. IEEE Int. Electron Devices Meeting (IEDM), Washington, DC, USA, Dec. 2015, pp. 22.2.1–22.2.45.

- [27] K. M. Choi and W. Y. Choi, "Work-function variation effects of tunneling field-effect transistors (TFETs)", IEEE Electron Device Lett., vol. 34, no. 8, pp. 942–944, Aug. 2013.

- [28] U. E. Avci, R. Rios, K. Kuhn and I. A. Young, "Comparison of performance, switching energy and process variations for the TFET and MOSFET in logic", 2011 Symposium on VLSI Technology Digest of Technical Papers, Honolulu, HI, 2011, pp. 124-125.

- [29] D. Leonelli, A. Vandooren, R. Rooyackers, S. De Gendt, M.M. Heyns, G. Groeseneken, "Drive current enhancement in ptunnel FETs by optimization of the process conditions", Solid-State Electronics, Volume 65, 2011, Pages 28-32, ISSN 0038-1101.

# $\ensuremath{\mathbb{C}}$ 2018. This manuscript version is made available under the CC-BY-NC-ND 4.0 license

http://creativecommons.org/licenses/by-nc-nd/4.0/

- [30] F. Mayer, C. L. Royer, J. F. Damlencourt, K. Romanjek, F. Andrieu, C. Tabone, B. Previtali, and S. Deleonibus, "Impact of SOI, Si1xGexOI and GeOI substrates on CMOS compatible Tunnel FET performance", 2008 IEEE International Electron Devices Meeting, Dec 2008, pp. 1–5.

- [31] G. Dewey, B. Chu-Kung, J. Boardman, J. M. Fastenau, J. Kavalieros, R. Kotlyar, W. K. Liu, D. Lubyshev, M. Metz, N. Mukherjee, P. Oakey, R. Pillarisetty, M. Radosavljevic, H. W. Then, and R. Chau, "Fabrication, characterization, and physics of III-V heterojunction tunneling Field Effect Transistors (H-TFET) for steep sub-threshold swing", IEEE IEDM Technical Digest, 2011, pp. 33.6.1–33.6.4

- [32] G.Zhou, R.Li, T.Vasen, M.Qi, S.Chae, Y.Lu, Q.Zhang, H.Zhu, J.-M.Kuo, T.Kosel, M.Wistey, P.Fay, A. Seabaugh, and H.(Grace) Xing, "Novel gate-recessed vertical InAs/GaSb TFETs with record high ION of 180μA/μm at VDS=0.5V", IEEE IEDM Technical Digest, 2012, pp. 777–780.

- [33] S. Mookerjea, R. Krishnan, S. Datta, and V. Narayanan, "On enhanced miller capacitance effect in Interband tunnel transistors", IEEE Electron Device Lett., vol. 30, no. 10, pp. 1102–1104, Oct. 2009.

- [34] G.V. Luong, S. Strangio, A. Tiedemannn, S. Lenk, S. Trellenkamp, K.K. Bourdelle, Q.T. Zhao, S. Mantl, "Experimental demonstration of strained Si nanowire GAA n-TFETs and inverter operation with complementary TFET logic at low supply voltages", Solid-State Electronics, Volume 115, 2016, Pages 152-159, ISSN 0038-1101.

- [35] M.D.V. Martino, J.A. Martino, P.G.D. Agopian, A. Vandooren, R. Rooyackers, E. Simoen, A. Thean, C. Claeys, "Performance of TFET and FinFET devices applied to current mirrors for different dimensions and temperatures", Semiconductor Science and Technology, vol. 31, n. 5, 055001, 2016.

- [36] G.V. Luong, S. Strangio, A. Tiedemann, P. Bernardy, S. Trellenkamp, P. Palestri, S. Mantl, Q.T. Zhao, "Experimental Characterization of the Static Noise Margins of Strained Silicon Complementary Tunnel-FET SRAM", 47th European Solid-State Device Research Conference (ESSDERC), Leuven, 2017, pp. 42-45. DOI: 10.1109/ESSDERC.2017.8066587

- [37] S. Strangio, P. Palestri, D. Esseni, L. Selmi, F. Crupi, S. Richter, Q.-T. Zhao, S. Mantl, "Impact of TFET Unidirectionality and Ambipolarity on the Performance of 6T SRAM Cells", IEEE Journal of the Electron Devices Society, vol. 3, no. 3, pp. 223-232, May 2015.

- [38] D. H. Morris, U. E. Avci and I. A. Young, "Variation-tolerant dense TFET memory with low VMIN matching low-voltage TFET logic", 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, 2015, pp. T24-T25.

- [39] J. Singh, K. Ramakrishnan, S. Mookerjea, S. Datta, V. Narayanan and D. Pradhan, "A novel Si-Tunnel FET based SRAM design for ultra low-power 0.3V VDD applications", 2010 15th Asia and South Pacific Design Automation Conference (ASP-DAC), Taipei, 2010, pp. 181-186.

- [40] X. Yang and K. Mohanram, "Robust 6T Si tunneling transistor SRAM design", 2011 Design, Automation & Test in Europe, Grenoble, 2011, pp. 1-6.

- [41] Y. Lee, D. Kim, J. Cai, I. Lauer, L. Chang, S. J. Koester, D. Blaauw, D. Sylvester, "Low-Power Circuit Analysis and Design Based on Heterojunction Tunneling Transistors (HETTs)", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 21, no. 9, pp. 1632-1643, Sept. 2013.

- [42] V. Saripalli, S. Datta, V. Narayanan and J. P. Kulkarni, "Variation-tolerant ultra low-power heterojunction tunnel FET SRAM design", 2011 IEEE/ACM International Symposium on Nanoscale Architectures, San Diego, CA, 2011, pp. 45-52.

- [43] S. Datta, H. Liu, V. Narayanan, "Tunnel FET technology: A reliability perspective", Microelectronics Reliability, Volume 54, Issue 5, 2014, Pages 861-874, ISSN 0026-2714.

- [44] Y. N. Chen, M. L. Fan, V. P. H. Hu, P. Su and C. T. Chuang, "Design and Analysis of Robust Tunneling FET SRAM", IEEE Transactions on Electron Devices, vol. 60, no. 3, pp. 1092-1098, March 2013.

- [45] Y. N. Chen, M. L. Fan, V. P. H. Hu, P. Su and C. T. Chuang, "Evaluation of Stability, Performance of Ultra-Low Voltage MOSFET, TFET, and Mixed TFET-MOSFET SRAM Cell With Write-Assist Circuits", IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 4, no. 4, pp. 389-399, Dec. 2014.

- [46] J. S. Liu, M. B. Clavel and M. K. Hudait, "An Energy-Efficient Tensile-Strained Ge/InGaAs TFET 7T SRAM Cell Architecture for Ultralow-Voltage Applications", IEEE Transactions on Electron Devices, vol. 64, no. 5, pp. 2193-2200, May 2017.

- [47] S. Strangio, P. Palestri, M. Lanuzza, F. Crupi, D. Esseni and L. Selmi, "Assessment of InAs/AlGaSb Tunnel-FET Virtual Technology Platform for Low-Power Digital Circuits", IEEE Transactions on Electron Devices, vol. 63, no. 7, pp. 2749-2756, July 2016.

- [48] S. Strangio, P. Palestri, M. Lanuzza, D. Esseni, F. Crupi, L. Selmi, "Benchmarks of a III-V TFET technology platform against the 10-nm CMOS FinFET technology node considering basic arithmetic circuits", Solid-State Electronics, Volume 128, 2017, Pages 37-42, ISSN 0038-1101.

# $\ensuremath{\mathbb{C}}$ 2018. This manuscript version is made available under the CC-BY-NC-ND 4.0 license

http://creativecommons.org/licenses/by-nc-nd/4.0/

- [49] A. Kamal and B. Bindu, "Design of tunnel FET based low power digital circuits", 18th International Symposium on VLSI Design and Test, Coimbatore, 2014, pp. 1-2.

- [50] D. H. Morris, K. Vaidyanathan, U. E. Avci, H. Liu, T. Karnik and I. A. Young, "Enabling high-performance heterogeneous TFET/CMOS logic with novel circuits using TFET unidirectionality and low-VDD operation", 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, 2016, pp. 1-2.

- [51] M. Lanuzza, S. Strangio, F. Crupi, P. Palestri, and D. Esseni, "Mixed Tunnel-FET/MOSFET Level Shifters: A New Proposal to Extend the Tunnel-FET Application Domain", IEEE Trans. Electron Devices, vol. 62, no. 12, pp. 3973–3979, 2015.

- [52] A. R. Trivedi, S. Carlo, and S. Mukhopadhyay, "Exploring tunnel-FET for ultra low power analog applications: A case study on operational transconductance amplifier", Proc. Design Autom. Conf. (DAC), 2013, Art. no. 109.

- [53] M. S. Kim, H. Liu, X. Li, S. Datta and V. Narayanan, "A Steep-Slope Tunnel FET Based SAR Analog-to-Digital Converter", IEEE Transactions on Electron Devices, vol. 61, no. 11, pp. 3661-3667, Nov. 2014

- [54] P. M. Asbeck, K. Lee and J. Min, "Projected Performance of Heterostructure Tunneling FETs in Low Power Microwave and mm-Wave Applications", IEEE Journal of the Electron Devices Society, vol. 3, no. 3, pp. 122-134, May 2015.

- [55] H. Liu, M. Cotter, S. Datta, and V. Narayanan, "Technology assessment of Si and III-V FinFET and III-V tunnel FETs from soft error rate perspective", Proc. IEEE Int. Electron Devices Meeting, 2013, pp. 25.5.1–25.5.4

- [56] A. Biswas, G. V. Luong, M. F. Chowdhury, C. Alper, Q.-T. Zhao, F. Udrea, S. Mantl, A. M. Ionescu, "Benchmarking of Homojunction Strained-Si NW Tunnel FETs for Basic Analog Functions", IEEE Transactions on Electron Devices, vol. 64, no. 4, pp. 1441-1448, April 2017.

- [57] D. Cavalheiro, F. Moll and S. Valtchev, "Insights Into Tunnel FET-Based Charge Pumps and Rectifiers for Energy Harvesting Applications", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 3, pp. 988-997, March 2017.