# **University of Udine**

DEPARTMENT OF ELECTRICAL MANAGEMENT AND MECHANICAL ENGINEERING Ph.D. Programme in Industrial and Information Engineering, XXVI Cycle

Ph.D. Dissertation

# Analysis and Design of High Speed Serial Interfaces for Automotive Applications

Candidate

Andrea Cristofoli

Advisors

Prof. Pierpaolo Palestri Dr. Nicola Da Dalt Prof. Luca Selmi

External Reviewers

Dr. Franz Dielacher Prof. Andrea Mazzanti

# **Abstract**

The demand for an enriched end-user experience and increased performance in next generation electronic applications is never ending, and it is a common trend for a wide spectrum of applications owing to different markets, like computing, mobile communication and automotive. For this reason High Speed Serial Interface have become widespread components for nowadays electronics with a constant demand for power reduction and data rate increase.

In the frame of gigabit serial systems, the work discussed in this thesis develops in two directions: on one hand, the aim is to support the continuous data rate increase with the development of novel link modeling approaches that will be employed for system level evaluation and as support in the design and characterization phases. On the other hand, the design considerations and challenges in the implementation of the transmitter, one of the most delicate blocks for the signal integrity performance of the link, are central.

The first part of the activity regarding link performance predictions lead to the development of an enhanced statistical simulation approach, capable to account for the transmitter waveform shape in the ISI analysis, a characteristic that is missed by the available state-of-the-art simulation approaches. The proposed approach has been extensively tested by comparison with traditional simulation approaches (Spice-like simulators) and validated against experimental characterization of a test system, with satisfactory results.

The second part of the activity consists in the design of a high speed transmitter in a deeply scaled CMOS technology, spanning from the concept of the circuit, its implementation and characterization. Targets of the design are to achieve a data rate of 5 Gb/s with a minimum voltage swing of 800 mV, thus doubling the data rate of the current transmitter implementation, and reduce the power dissipation adopting a voltage mode architecture. The experimental characterization of the fabricated lot draws a twofold picture, with some of the performance figures showing a very good qualitative and quantitative agreement with pre-silicon simulations, and others revealing a poor performance level, especially for the eye diagram. Investigation of the root causes by the analysis of the physical silicon design, of the bonding scheme of the prototypes and of the pre-silicon simulations is reported. Guidelines for the redesign of the circuit are also given.

# **Sommario**

Nel panorama delle applicazioni elettroniche il miglioramento delle performance di un prodotto da una generazione alla successiva ha lo scopo di offrire all'utilizzatore finale nuove funzioni e migliorare quelle esistenti. Negli ultimi anni grazie al costante avanzamento della tecnologia integrata, si è assistito ad un enorme sviluppo della capacità computazionale dei dispositivi in tutti i segmenti di mercato, quali ad esempio l'information technology, la comunicazione mobile e l'automotive. La conseguente necessità di mettere in comunicazione dispostivi diversi all'interno della stessa applicazione e di traferire grosse quantità di dati ha provocato una capillare diffusione delle interfacce seriali ad alta velocità, o High Speed Serial Interfaces (HSSIs). La necessità di ridurre il consumo di potenza e aumentare il bit rate per questo tipo di applicazioni è diventata dunque un ambito di ricerca di estremo interesse.

Il lavoro discusso in questa tesi si colloca nell'ambito della trasmissione di dati seriali a bit rate superiori ad 1Gb/s e si sviluppa in due direzioni: da un lato, a sostegno del continuo aumento del bit rate nelle nuove generazioni di interfacce, è stato affrontato lo sviluppo di nuovi approcci di modellazione del sistema, che possano essere impiegati nella valutazione delle prestazioni dell'interfaccia e a supporto delle fasi di progettazione e di caratterizzazione. Dall'altro lato, si è focalizzata l'attenzione sulle sfide e sulle problematiche inerenti il progetto di uno dei blocchi più delicati per le prestazioni del sistema, il trasmettitore.

La prima parte della tesi ha come oggetto lo sviluppo di un approccio di simulazione statistico innovativo, in grado di includere nell'analisi degli effetti dell'interferenza di intersimbolo anche la forma d'onda prodotta all'uscita del trasmettitore, una caratteristica che non è presente in altri approcci di simulazione proposti in letteratura. La tecnica proposta è ampiamente testata mediante il confronto con approcci di simulazione tradizionali (di tipo Spice) e mediante il confronto con la caratterizzazione sperimentale di un sistema di test, con risultati pienamente soddisfacenti.

La seconda parte dell'attività riguarda il progetto di un trasmettitore integrato high speed in tecnologia CMOS a 40 nm e si estende dallo studio di fattibilità del circuito fino alla sua realizzazione e caratterizzazione. Gli obiettivi riguardano il raggiungimento di un bit rate pari a 5 Gb/s, raddoppiando così il bit rate dell'attuale implementazione, e di una tensione differenziale di uscita minima di 800 mV (picco-picco) riducendo allo stesso tempo la potenza dissipata mediante l'adozione di una architettura Voltage Mode. I risultati sperimentali ottenuti dal primo lotto fabbricato non delineano un quadro univoco: alcune performance mostrano un ottimo accordo qualitativo e quantitativo con le simulazioni pre-fabbricazione, mentre prestazioni non soddisfacenti sono state ottenute in particolare per il diagramma ad occhio. Grazie all'analisi del layout del prototipo, del bonding tra silicio e package e delle simulazioni pre-fabbricazione è stato possibile risalire ai fattori responsabili del degrado delle prestazioni rispetto alla previsioni pre-fabbricazione, permettendo inoltre di delineare le linee guida da seguire nella futura progettazione di un nuovo prototipo.

# **Contents**

| A  | Abstract |                                                                  |     |  |  |  |

|----|----------|------------------------------------------------------------------|-----|--|--|--|

| So | omma     | rio                                                              | v   |  |  |  |

| C  | onten    | ts                                                               | vii |  |  |  |

| 1  | Intr     | oduction                                                         | 1   |  |  |  |

|    | 1.1      | High Speed Serial Interfaces                                     | 1   |  |  |  |

|    | 1.2      | Building Blocks of a Serial Link                                 | 2   |  |  |  |

|    | 1.3      | Interference Sources in Serial Links                             | 3   |  |  |  |

|    |          | 1.3.1 Interferences due to transmission medium                   | 3   |  |  |  |

|    |          | 1.3.2 Noise Disturbances                                         | 4   |  |  |  |

|    | 1.4      | Equalization                                                     | 4   |  |  |  |

|    |          | 1.4.1 Transmit Equalization                                      | 5   |  |  |  |

|    |          | 1.4.2 Receiver Equalization                                      | 6   |  |  |  |

|    | 1.5      | High Speed Links in the Automotive Environment                   | 9   |  |  |  |

|    | 1.6      | Motivation of the work and thesis organization                   | 11  |  |  |  |

| 2  | Mod      | deling of ISI and Jitter in High Speed Links                     | 13  |  |  |  |

|    | 2.1      | Intersymbol Interference Modeling                                | 13  |  |  |  |

|    |          | 2.1.1 Peak Distortion Analysis                                   | 13  |  |  |  |

|    |          | 2.1.2 Statistical Analysis based on the Single Bit Response      | 15  |  |  |  |

|    |          | 2.1.3 Transitions-based Analysis                                 | 18  |  |  |  |

|    | 2.2      | Jitter                                                           | 20  |  |  |  |

|    |          | 2.2.1 Clock Jitter                                               | 21  |  |  |  |

|    |          | 2.2.2 Jitter in Serial Data                                      | 21  |  |  |  |

|    |          | 2.2.3 Jitter Modeling                                            | 23  |  |  |  |

|    | 2.3      | Intersymbol Interference vs. Data-Dependent Jitter               | 26  |  |  |  |

| 3  | Imp      | roved ISI and Jitter Modeling                                    | 29  |  |  |  |

|    | 3.1      | Transmitter Waveform and Validity of the LTI Assumption          | 29  |  |  |  |

|    | 3.2      | Edge Responses                                                   | 30  |  |  |  |

|    | 3.3      | Channel Response                                                 | 31  |  |  |  |

|    |          | 3.3.1 Considerations about Impedance Discontinuities in the Link | 35  |  |  |  |

|    | 3.4      | Computing the ISI Probability Distribution Function              | 38  |  |  |  |

|    |          | 3.4.1 Validation                                                 | 40  |  |  |  |

|    |          | 3.4.2 Effect of the Edge Steepness                               | 41  |  |  |  |

|    | 3.5      | Introducing litter in the Model                                  | 42  |  |  |  |

|    | 3.6   | Validation of the Jitter Model                      | 44  |

|----|-------|-----------------------------------------------------|-----|

| 4  | Exp   | erimental Verification                              | 51  |

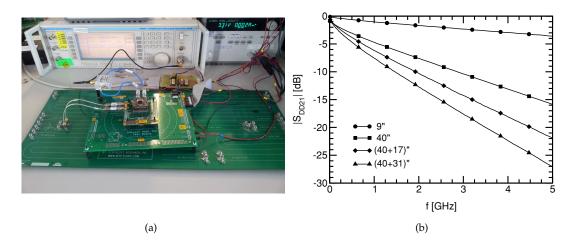

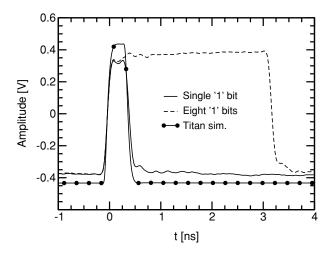

|    | 4.1   | Test System                                         | 51  |

|    | 4.2   | Transmitter Characterization                        | 51  |

|    | 4.3   | Comparison with Simulations                         | 54  |

|    |       | 4.3.1 Data Transmission with De-Emphasis            | 55  |

| 5  | Trar  | nsmitter Architectures for High Speed Links         | 59  |

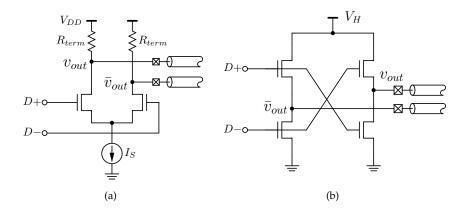

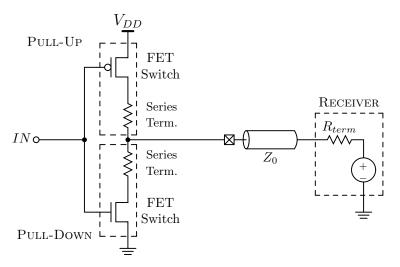

| _  | 5.1   | Current Mode vs. Voltage Mode Differential Drivers  | 60  |

|    | 5.2   | Termination                                         | 62  |

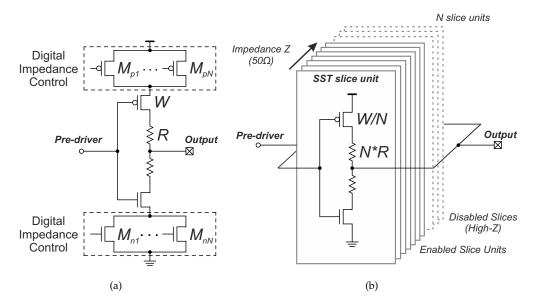

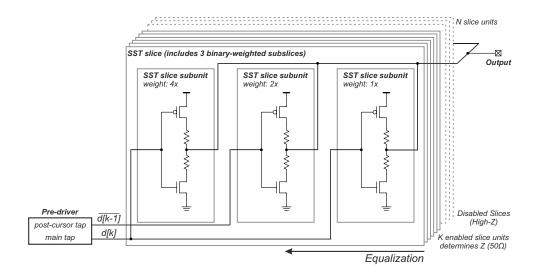

|    | 5.3   | Source-Series Terminated Transmitter Architecture   | 63  |

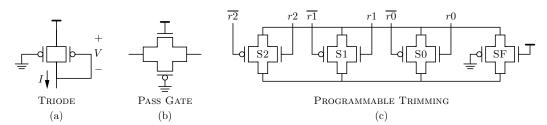

|    | 3.5   | 5.3.1 Impedance Tuning                              | 64  |

|    |       |                                                     | 65  |

|    |       | 5.3.2 Equalization                                  |     |

|    |       | 5.3.3 Performance comparison of recent publications | 66  |

| 6  |       | ign of a High Speed CMOS Transmitter                | 69  |

|    | 6.1   | Design Requirements                                 | 70  |

|    | 6.2   | Choice of the Transmitter Topology                  | 71  |

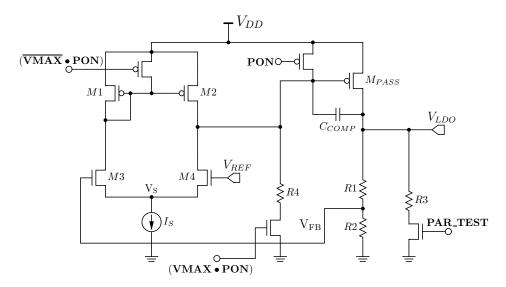

|    | 6.3   | Transmitter Design                                  | 74  |

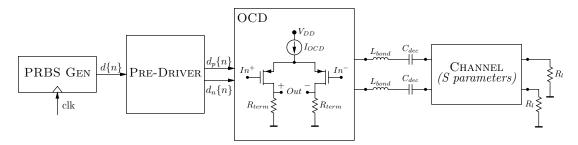

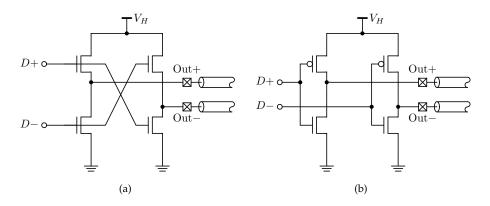

|    |       | 6.3.1 Off-Chip Driver                               | 75  |

|    |       | 6.3.2 Pre-Driver                                    | 76  |

|    |       | 6.3.3 Buffer                                        | 77  |

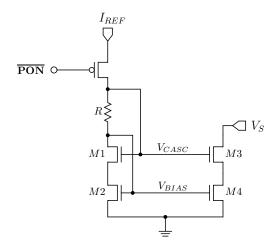

|    |       | 6.3.4 Voltage Regulator                             | 78  |

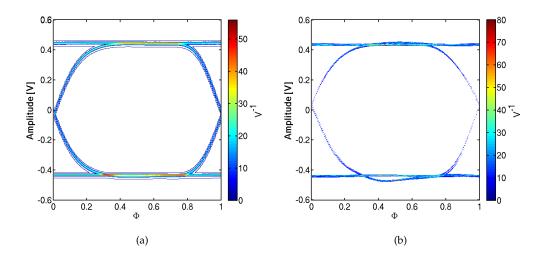

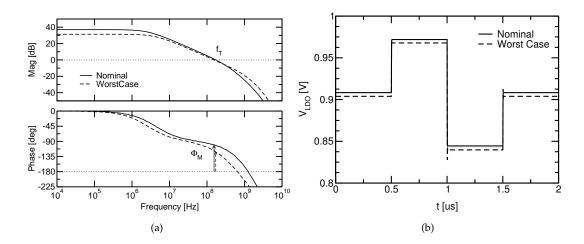

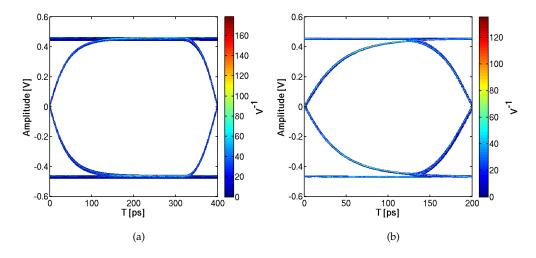

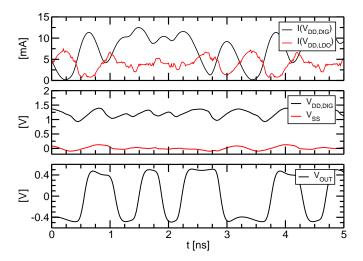

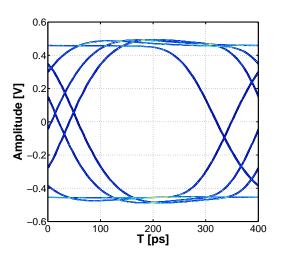

|    |       | 6.3.5 Eye Diagram                                   | 81  |

|    | 6.4   | Comparison with Literature                          | 82  |

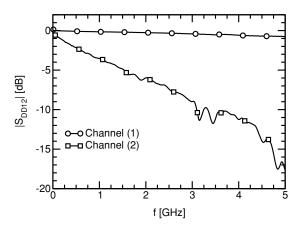

|    | 6.5   | Signal Integrity Study                              | 82  |

|    | 6.6   | Experimental Results                                | 86  |

|    |       | 6.6.1 Voltage Regulator Output                      | 86  |

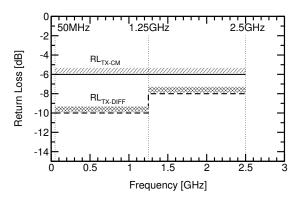

|    |       | 6.6.2 Transmitter Output Impedance                  | 86  |

|    |       | 6.6.3 Transmitter Return Loss                       | 87  |

|    |       | 6.6.4 Current Consumption                           | 88  |

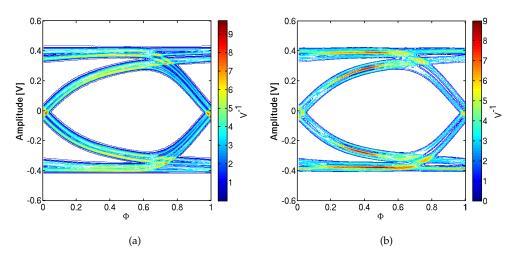

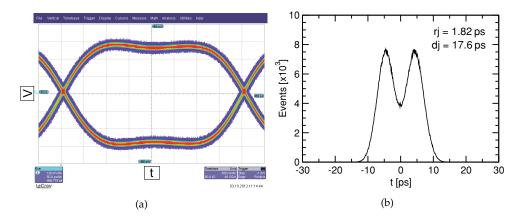

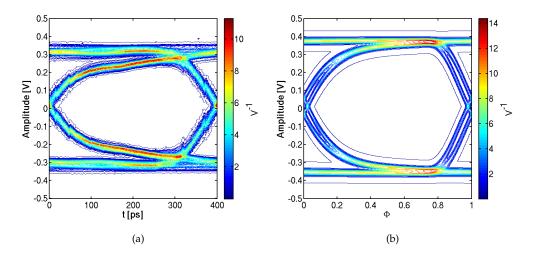

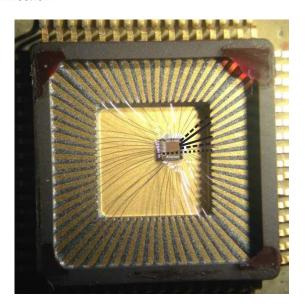

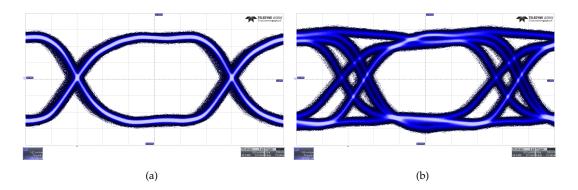

|    |       | 6.6.5 Eye Diagram                                   | 89  |

|    |       | 6.6.6 Improved Chip Bonding                         | 94  |

|    | 6.7   | Final Remarks                                       | 96  |

| 7  | Con   | clusions                                            | 97  |

| Δ  | Mat   | lab Implementation                                  | 99  |

| 11 |       | Scripts                                             | 99  |

|    | 71.1  | •                                                   | 100 |

|    |       | •                                                   | 100 |

|    | ۸.2   |                                                     |     |

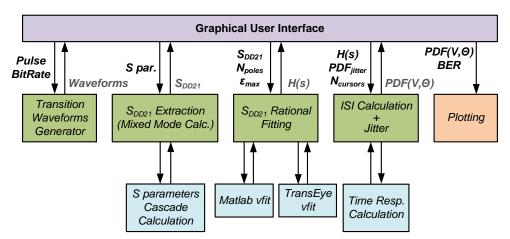

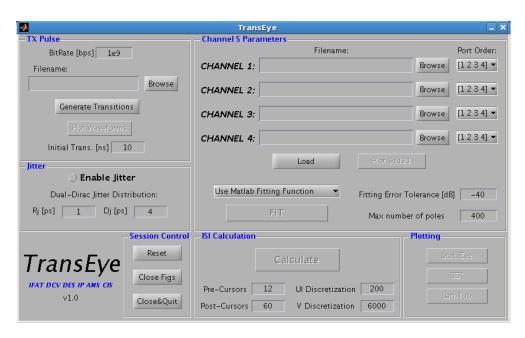

|    | A.Z   | ISI and Jitter Modeling Tool                        | 104 |

| Bi | bliog | raphy                                               | 107 |

| A  | crony | ms                                                  | 113 |

| Ca | ndid  | ate's Bio and Publications                          | 115 |

| ( ) | വ | NΤ | $\Gamma \mathbf{E}$ | NΤΠ | ГС |

|-----|---|----|---------------------|-----|----|

Acknowledgments 117

# Chapter 1

# Introduction

# 1.1 High Speed Serial Interfaces

Technology advancement of the semiconductor industry over the last decades has repeatedly shown to follow Moore's Law in that the number of transistors in an integrated circuit doubles roughly every two years. This continuous shrinkage of the feature size enabled higher operation speed, logic density, integration, and lower power consumption per logic function. As a direct consequence of this scaling process, the number of functionalities crammed into processing units has became enormous and has generated a corresponding increase in the amount of data exchanged between chips to guarantee the increase in the overall system performance.

The two conventional methods to increase chip communication bandwidth consists in increasing the number of I/O channels or in raising the data rate per channel. However, cost containment imposes an upper limit to the I/O pin count and to the number of board traces and board material, preventing a significant increase in the I/O channel number. As a consequence, the increasing bandwidth demands must be satisfied pushing the data rate towards higher limits. But this presents a remarkable challenge, considering that, while usually high-performance I/O circuitry can leverage the technology improvements that enable increased core performance, unfortunately the bandwidth of the electrical channels used for the communication does not scale in the same manner. To further raise the bar, pushing to higher power consumption to overcome channel limited bandwidth is not an option, as containing the power budget is becoming an urgent need throughout the whole electronics panorama.

If in addition to the elements thus mentioned, we also consider how in our everyday life we are experiencing the pervasive presence of communication and multimedia equipment, it appears clear why high-speed serial connectivity has risen to the rank of critical enabling technology in so many markets. High Speed Serial Interfaces (HSSIs), in fact, find their place in a large number of electronic applications, used for [1]:

- Chip-to-chip, board-to-board, and system-to-system links;

- Data communication and telecommunication networks, e.g. Gigabit Ethernet;

- Component interfaces internal to optical network equipment, e.g. Optical Internetworking Forum (OIF) standards like Interlaken [2];

- Computing I/Os, e.g. Peripheral Component Interconnect Express (PCIe), Hypertransport [3,4];

- Storage area networking, e.g. Serial Advanced Technology Attachment (SATA), Fibre Channel;

- Wireless networking, linking the radio equipment control and the radio equipment in wireless base stations, e.g. Common Public Radio Interface (CPRI) [5];

- High-performance embedded processing, e.g. Serial Rapid IO (SRIO) [6].

To give an idea of the typical data rates we can distinguish today's high-speed link standards minding the maturity of the market they address [7,8]. Therefore, considering relatively established markets, typical data rates range from 5 to 6 Gb/s, as in the case of PCIe Gen2 (5 Gb/s), HyperTransport and SATA III/SAS II (6 Gb/s). The leading-edge and next-generation standards push data rates to the 8-11Gb/s range, as in the case of IEEE 10G Ethernet, IEEE 40G/100G Ethernet (802.3ba,  $4\times/10\times$  10.3125 Gb/s), PCIe Gen3 (8 Gb/s), and Fibre Channel  $8\times$  (8.5 Gb/s). Finally, new standards for emerging market segments go even beyond these figures, as in the case of 16G Fibre Channel (14.1 Gb/s) and SATA IV/SAS III (12 Gb/s).

# 1.2 Building Blocks of a Serial Link

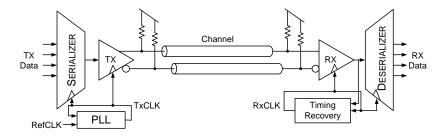

Figure 1.1 shows the main components of a typical HSSI [9,10]. One of the main purposes of the HSSIs is to limit the number of high-speed I/O pins in chip packages and relax the Printed Circuit Board (PCB) wiring constraints in terms of copper traces, connector pin count, and so on. For this reason, the first building block we encounter at the transmitter side is a *serializer* which, as the name suggests, serializes an input bus of parallel data into a unique stream. The transmitter task is to generate an accurate voltage swing on the channel while also maintaining proper output impedance in order to attenuate any channel-induced reflections. Either current- or voltage-mode drivers are employed as output stages [11,12]. The generation of the timing reference for the serializer and transmitter circuits is performed by means of a frequency synthesis Phase Locked Loop (PLL): it generates the high-frequency clock, usually at a frequency equal to the desired data rate, by multiplying the low frequency reference clock of the elaboration digital core.

At the receiver side, the incoming signal is sampled and compared to a threshold to properly discriminate bits '0' and '1', regenerated to CMOS values, and finally deserialized. At the receiver, the clock providing the sampling instants is aligned to the incoming data stream by a timing recovery system which usually incorporates a PLL and some additional circuits needed to synchronize the receiver with the incoming data stream.

Figure 1.1: Block diagram of a typical high speed serial link [9].

The timing blocks of the link, at both the transmitter and receiver side, are critical for highspeed operation of the link since they provide accurate spacing of transmitted data symbols and sampling of the signal waveforms at the receiver.

## 1.3 Interference Sources in Serial Links

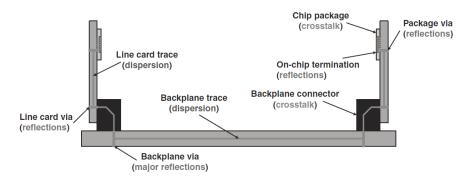

The typical structure of a serial link is represented in Figure 1.2, which shows the cross section of a backplane link. In such a system, a number of components constitute the transmission medium: as can be seen in the figure, in addition to the backplane channel, vias, connectors, and board traces are present. As each element has non-ideal characteristics, it is not transparent to the signal propagation thus interferes with the transmitted data.

Figure 1.2: The cross section of a backplane link as an example of electrical channel [9].

A first rough classification of the interference sources in a link can be made distinguishing among interferences due to the transmission medium and noise.

#### 1.3.1 Interferences due to transmission medium

This subset of interferences is determined by the non-ideal electrical properties of the medium. They are:

Channel insertion loss. When traveling through a transmission medium, electrical signals experience an attenuation that increases at high-frequency. Main causes are the *skin effect* and the *dielectric loss*. In the first case, the effective cross section of the wire, or trace, decreases at high frequencies because the majority of the current tends to flow near the conductor surface. This results in a resistive loss term that is proportional to the square root of the frequency [9,13]. In the second case, at high frequencies, energy is absorbed from the signal trace and transferred into heat due to the rotation of the dielectric atoms in an alternating electric field. This results in the dielectric loss term increasing proportional to the signal frequency [9,13].

**Return Loss.** Return loss is a measure of signal energy loss due to reflection. When impedance discontinuity exists, part of the signal is reflected back at the impedance discontinuity point, thus reducing the signal energy being transmitted.

Other Loss Factors. Other causes of losses are *mode conversion* and *radiation*. The first effect takes place when in a differential signaling system the balance between the two conductors is not perfect and part of the differential signal is converted to common mode,

resulting in an energy loss of the desired differential signal [14]. The second effect is due to electromagnetic waves radiating energy into the air, e.g. in the case of the formation of standing waves in the line [13].

Regardless of the mechanism, loss in the channel is typically measured in terms of decibel at the Nyquist frequency of the data stream, i.e.  $F_s/2$ , where  $F_s$  is the nominal data rate.

## 1.3.2 Noise Disturbances

They consist in *crosstalk* from other channels and noise due to random signal fluctuations.

Crosstalk occurs due to both capacitive and mutual inductive coupling [15] between neighboring signal lines. It takes place especially at connectors and chip packages, where spacing between signal lines is smaller, and shielding is less effective. Crosstalk is classified either as Near-End Crosstalk (NEXT), where aggressor and victim are on the same chip, or Far-End Crosstalk (FEXT), where the aggressor energy couples and propagates along the channel to a victim on another chip. NEXT is commonly the most detrimental crosstalk, as energy from a strong transmitter can couple onto a weak received signal on the same chip, which has been attenuated by the band-limited channel.

Random signal fluctuations are due to the inherent thermal and shot noise of the passive and active system components. Random fluctuation are particularly important when dealing with timing of signals, as they can cause deviation of the signal characteristics, usually the edge crossings, with respect their ideal value. We speak in this case of *jitter*, that will be extensively treated in Section 2.2.

# 1.4 Equalization

Frequency dependent channel loss can reach magnitudes sufficient to make simple Non-Return to Zero (NRZ) binary signaling undetectable. Thus, in order to continue scaling electrical link data rates, systems that compensate for frequency-dependent loss, i.e. that *equalize* the channel response have been developed [16].

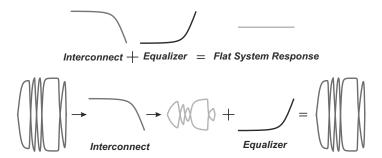

As reported by the simplified plot in Figure 1.3(top), the idea behind equalization is to insert into the serial link an "equalizer" such that its transfer function compensates the dispersion of the channel. By multiplying the low-pass transfer function of the transmission medium with that of the equalizer, as the whole system is linear, the goal is to have a resultant transfer function that is relatively "flat" up to the required frequency.

Figure 1.3(bottom) shows how equalization acts on the signal: the signal launched by the transmitter (left) is attenuated by the transmission medium (center). When passing through the equalizer, the original signal is restored (right).

Since linearity is assumed, it is important to note that signal conditioning can be applied before or after the interconnect. In this example, the equalizer is placed at the far end, at the receiver. Similarly, operating at the transmitter side the signal is pre-distorted so that after it goes through the interconnect, the resulting signal is much easier to be recover at the receiver.

Equalization can be implemented with digital techniques, e.g. with Finite Impulse Response (FIR) or Infinite Impulse Response (IIR) filters, or analog techniques, such as Continuous Time Linear Equalization (CTLE). Furthermore, equalization techniques could be either linear or adaptive (non-linear), such as Decision Feedback Equalization (DFE). In the

**Figure 1.3:** Simplified scheme showing the idea behind equalization (top), and effects of equalization at signal level (bottom) [1,7].

following a brief summary of nowadays most diffused transmitter and receiver equalization techniques will be given.

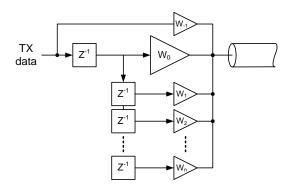

## 1.4.1 Transmit Equalization

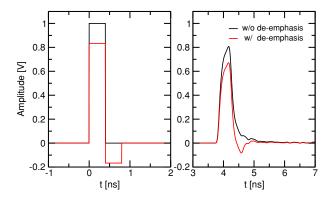

Transmit equalization is implemented by preconditioning the signal before being applied to the channel: this type of signal conditioning is called *emphasis*. It can operate in two ways: the signal can be distorted such that its high frequency contents are amplified or, at the opposite, the signal low-frequency contents are reduced [1,7,17]. In the former case we denote it as *pre-emphasis*, in the latter as *de-emphasis*.

**Figure 1.4:** Conceptual scheme of transmitter equalization implementation based on registers holding prior and upcoming bits [9].

Emphasis is relatively simple to implement and does not require large additional power: for this reason it is the most common technique used in HSSI [18]. The common implementation is based on the FIR filter approach: as all serial data is available at the transmitter side, 1-bit spaced versions of the transmitted data can be easily created by means of registers that hold prior and upcoming serial data bits (see Figure 1.4), and then summed with proper weights to generate the appropriate voltage level of the current bit.

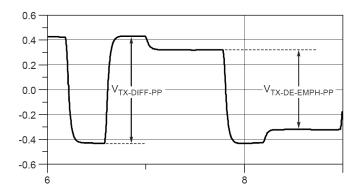

Figure 1.5 shows an example of de-emphasized waveform [3], obtained with a simple FIR filter with only one bit delay (so called one tap). Each logic value output by the transmitter can be represented with two different voltage levels: all transition bits corresponding to a change in the logical output state (from '0' to '1' or '1' to '0') are driven to the full swing amplitude ( $V_{TX-DIFF-PP}$  in Figure 1.5). On the contrary, when multiple bits of the same logic value ('1' or '0') are output in succession, they are driven to the de-emphasized amplitude ( $V_{TX-DE-EMPH-PP}$  in Figure 1.5). The de-emphasis ratio (DE-RATIO) is thus defined

Figure 1.5: Transmitter waveform in presence of de-emphasis.

as [3]:

$$DE - RATIO = -20\log_{10}\left(\frac{V_{TX-DIFF-PP}}{V_{TX-DE-EMPH-PP}}\right)$$

(1.1)

In serial link designs, equalization is most often located at the transmitter side: the main reason is that here the input of the equalizer circuit is a binary data pattern instead of an analog voltage. Therefore the equalizer is simple to implement using simple digital and analog techniques, e.g. as Direct FIR [19] or Segmented DAC [20] transmitters.

## 1.4.2 Receiver Equalization

Common equalization techniques at the receiver side fall under three categories: CTLE, RX FIR and DFE [17].

#### **CTLE**

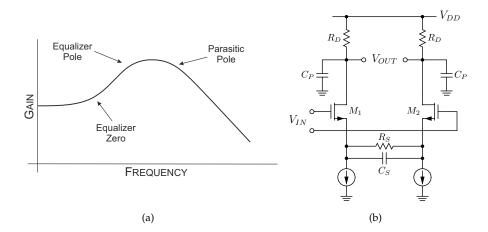

As the name implies, Continuous Time Linear Equalization is a linear technique and operates continuously in time. Therefore can be considered an analog technique in nature [21]. Similar to transmit pre-emphasis, CTLE addresses pre-cursor and post-cursor ISI, but in continuous time instead of being limited to a pre-defined number of transmitter taps. Figure 1.6(a) shows an example of a first-order CTLE transfer function: this technique aims to compensate the poles in the low-pass channel transfer function by inserting a zero value in correspondence of the frequencies close to the link data rate.

An implementation example of CTLE with a continuous-time amplifier is shown in Figure 1.6(b) [22,23]. The RC-degeneration in the source-couple pair creates a high-pass filter transfer function if the zero frequency is designed to be much lower of the dominant pole [16]. While this implementation is a simple and low-area solution, one issue is that the amplifier has to supply gain at frequencies close to the full signal data rate. This gain-bandwidth requirement potentially limits the maximum data rate. Multiple equalizer stages implementations can be devised to increase the order of the equalizer and thus increase the maximum boost achieved in a given frequency interval. However, tuning the parasitic poles and their locations of such multiple stage design across PVT variations can be hard [21]. For this reason CTLE compensation is usually limited to the 1<sup>st</sup> order.

**Figure 1.6:** (a) CTLE high-pass transfer function [8]. (b) Continuous-time amplifier as an active implementation of CTLE [23].

#### RX FIR

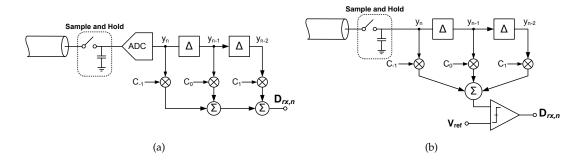

Analogously to transmit pre-emphasis, the RX FIR equalization scheme employs a FIR filter to compensate for channel losses. RX FIR equalization can be implemented as either discrete or analog [16,17].

The discrete RX FIR conceptual block diagram is shown in Figure 1.7(a). It adopts a linear digital filter similar to the one used for transmit pre-emphasis. Anyway, as the input of the filter is the analog output of the channel, in this case a Sample and Hold Amplifier (SHA) and an Analog to Digital Converter (ADC) are required to interface the channel output to the filter. The analog to digital conversion is particularly critical, as achieving a high resolution of the taps (e.g. in the order of 10 bits [21]) and at the same time operate at the full data rate of the interface requires large power and area overhead [16]. The high-speed ADC implementation thus poses serious limitations to the adoption of discrete RX FIR.

An analog RX FIR equalizer obviates the need for a high-speed ADC. It is therefore attractive for high-speed operation with potentially lower power consumption as just the relatively simple sample and hold circuit is required. A conceptual block diagram of an analog FIR equalizer is shown in Figure 1.7(b). As opposed to the digital delays used in the discrete FIR, an analog delay chain is required. As the overall structure is analog, non-idealities limiting the overall performance of the circuit come from errors in the sampled voltage due to sampling jitter and charge leakage, non-linearity of the equalizer taps and summing circuits, and offset currents due by device mismatch. If not handled properly, all these issues can negate the benefits versus the digital implementation [21].

A common problem faced by linear receiver-side equalization, thus both CTLE and RX FIR, is that high-frequency noise content and crosstalk are amplified along with the incoming signal. Nonetheless, one of the major advantage of receiver-side equalization is that the filter tap coefficients can be adaptively tuned to the specific channel, which is not possible with transmit-side equalization unless a back-channel is implemented [9].

#### **DFE**

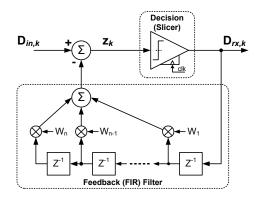

The third equalization topology commonly implemented at receiver side is Decision Feedback Equalization (DFE). The block diagram of the DFE is shown in Figure 1.8. The idea behind

Figure 1.7: RX FIR implementations: digital (a) and analog (b) [16].

it is to cancel Intersymbol Interference (ISI) directly from the incoming signal using the last resolved data to control the polarity of the equalization taps: thus it is a non-linear technique. Working on quantized input values, this technique does not operates a high frequency boost on the analog signal and therefore has the advantage of not amplifying noise and crosstalk, on the contrary of what happens with linear equalizers. Due to the feedback structure, DFE addresses only post-cursor ISI, i.e. ISI caused by the previous bits, and leaves the pre-cursor ISI uncompensated. As a consequence, a separated feed-forward equalizer, e.g. CTLE as in [24], is still required to accommodate the pre-cursor ISI [1,16].

Figure 1.8: Receiver equalization with DFE [9].

In addition to this, the issue of error propagation arises. The error propagation phenomenon happens if the noise is large enough to determine a wrong decision of the current data. At this point, the bit is fed back through the ISI cancellation filter and determines an erroneous coefficient computation for the present data sample. Therefore, the error on a single bit capture affects few consecutive bits until it propagates out of the filter and thus correct samples are obtained again [16].

Another major challenge in DFE implementation arises from the need for the first tap feedback to be ready before the next bit comes. In other words, the computation of the first tap coefficient must be done in one bit period. Therefore this critical timing path needs to be highly optimized [9] or different filter architectures are needed, i.e. decision look-ahead schemes [16], when the first tap loop delay can not be reduced below 1 Unit Interval (UI) due to the very high data rate.

# 1.5 High Speed Links in the Automotive Environment

In the last decade, the massive introduction of electronic devices and products in every aspect of our life has been driven by advancements in the integrated electronics. Three principles can be cited to understand this impressive development: transparency, i.e. the user can be helped unobtrusively with electronics, pervasiveness, i.e. any common object can host electronics thanks to integration, and intelligent environments, i.e. environments that are sensitive and responsive to the presence of people thanks to embedded sensors and systems.

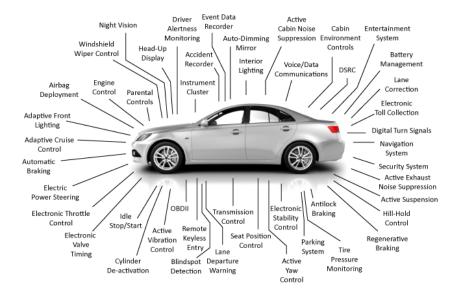

Vehicles have not been immune to this trend: in fact, automotive innovation today is almost entirely driven by semiconductor actuation, control, or monitoring, and it involves every different domain inside a vehicle (Powertrain, Driver Comfort, Safety, Infotainment, Chassis, Driver Assistance). The list of electronically assisted functions and systems that may be found on a today's upscale automobile is very long. Figure 1.9 tries to mention some of them and gives an idea of the deep penetration of electronics into the automotive environment.

Figure 1.9: Some of the functions and systems assisted by electronics available in nowadays vehicles.

This picture is not likely to change in the future [25–27]. In fact, rising fuel prices and environmental concerns aiming at the reduction of carbon dioxide emission are pushing the adoption of more and more sophisticated engine and powertrain control schemes. The same applies to electric vehicles too, as power and battery management is a key aspect to make them suitable for modern human mobility needs. Secondly, improving the passive and active safety is a constant target as the available technologies make advancements possible (e.g. the so-called Advanced Driver Assistance Systems (ADAS)). Thirdly, automobile producers will try to enhance the on-board user experience increasing the connectivity solutions (GPS, Mobile Internet Connectivity) and body comfort systems. The need to handle all these various functions demands solid computations capabilities in a number of different locations in the vehicle, thus asking for an increase of the number of Microcontroller Units (MCUs) used on-board. In fact it is estimated that today's well-equipped upscale automobile generally relies on more than 80 electronic control units [26], and this number is constantly increasing. This is also confirmed by the analysis of the yearly semiconductor revenue referred to the

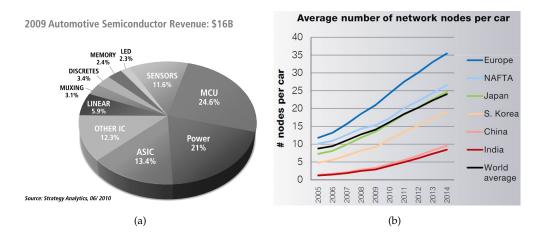

automotive segment [28]. Distinguishing the revenue depending on the type of device, as shown in Figure 1.10(a), it is possible to see that approximately <sup>1</sup>/<sub>4</sub> of the automotive devices sold worldwide are MCUs. The same growth prediction is devised in [29], where the number of nodes constituting the on-board network in new generation of vehicle is analyzed over the last 10 years. As can be seen in Figure 1.10(b), this number is steadily increasing world wide, testifying from one side that the need to include advance computation capability in order to handle the various functions in the vehicle is a strong trend, and on the other side that the connection of all these computational nodes is becoming a challenging problem.

**Figure 1.10:** (a) In 2009, MCUs were the market-share leaders among the various semiconductor device types used in vehicles [28]. (b) Each MCU is at the same time a node of the vehicle network: over the last 10 years the increase in the number of network nodes, thus in the number of MCUs on board, has been a common trend worldwide [29].

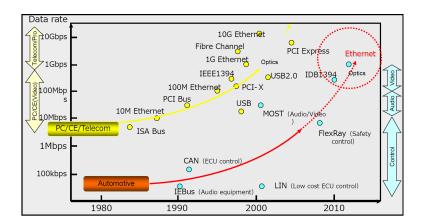

The vehicle on-board networking structure is realized nowadays based on bus standards like Controller Area Network (CAN), Local Interconnect Network (LIN) and FlexRay [30], with data rates spanning from a few tens of kb/s (in the case of LIN) to the 10 Mb/s per lane of FlexRay (see Figure 1.11). The implementation of electronic applications involving the transmission of audio or video streams, either in the field of the active and passive safety (e.g. the already mentioned ADAS) or in that of the entertainment of the passengers, will demand for the transfer of a high quantity of data. It will thus require the use of connectivity solutions capable of reaching higher transfer rates. In fact, in the near future the adoption of Ethernet as a standard for networking in automotive applications [27] goes exactly in the direction of allowing the transfer of high volumes of data. Nevertheless the trend revealed by Figure 1.11 is quite likely not to stop at Ethernet. We see in fact that in terms of data rates, serial application in the automotive are trailing the path opened by the telecommunication and consumer markets, with a delay time frame of approximately 10-15 years [31]. We can therefore say that HSSI implementations in the automotive allowing for data rates of few Gb/s, are state of the art nowadays. We can also expect that vehicle electronic applications hosting HSSIs will become more and more common in the next years.

Nevertheless, a direct technology transfer from the telecommunication and consumer market is not possible, due to the serious challenges that the automotive environment poses to the implementation of electronic applications in general, and of HSSIs in particular. The requirements of automotive electronics are much more stringent and demanding with respect to the consumer segment. In Table 1.1 the principal differences are highlighted. The more im-

**Figure 1.11:** The data rate improvement of connection solutions for the automotive market is following the same trend as in the telecommunication and consumer markets, but 10-15 year later [31]. Serial interfaces allowing data transmission in the order of Gb/s are nowadays the state of the art in the field.

pressive numbers are in the broader temperature range, spanning from  $-40\,^{\circ}\text{C}$  up to  $175\,^{\circ}\text{C}$ , in the expected operation time, which can be as high as 25 years and the ESD tolerance, which can be even double than the value required in consumer applications. It is clear then that implementation of HSSIs to be employed inside vehicles presents additional challenges to the design of such systems.

Table 1.1: Requirements on automotive electronics [32]

| Parameter                    | Consumer                                  | Automotive                                               |

|------------------------------|-------------------------------------------|----------------------------------------------------------|

| Temperature                  | $0^{\circ}\text{C} 	o 40^{\circ}\text{C}$ | $-40^{\circ}\text{C} \rightarrow 85/175^{\circ}\text{C}$ |

| Voltage                      | 3.3 V                                     | $> 80\mathrm{V}$                                         |

| Operation Time               | 1-3 years                                 | up to 25 years                                           |

| Humidity                     | Low                                       | 0% up to 100%                                            |

| Tolerated Field Failure Rate | <1000 ppm                                 | Target: zero failure                                     |

| $\mathrm{ESD}^a$             | 4-8kV                                     | 8-15kV                                                   |

<sup>&</sup>lt;sup>a</sup>Machine Model (MM)

# 1.6 Motivation of the work and thesis organization

From this brief introduction, it clearly appears that efficiently addressing the requirements in system bandwidth of nowadays applications achieving higher data rates and greater integration is becoming a challenge. This challenge includes targeting lower bit error rates and ensuring signal and power integrity while maintaining power efficiency and data rates, and optimizing design productivity. In this framework, the work discussed in this thesis develops in two directions. On one hand, with the aim to support the continuous data rate increase, the activity with major impact (as demonstrated by a publication in a peer-reviewed journal, see Candidate's Bio and Publications at page 115) has been the development of novel link modeling approaches to be employed for system level evaluation, design, and characterization. The major technical impact of this thesis stems from this first part, . On the other side,

the design implementation of a high speed transmitter, one of the most delicate blocks for the signal integrity performance of the link, are carried out, with the aim of improving the current implementation in terms of power dissipation and supported data rate.

After this brief introduction, the thesis is organized in chapters, each presenting one of the activities carried out by the candidate.

- Chapter 2 deepens in the modeling of ISI and jitter in serial gigabit links. The approaches proposed in available literature to evaluate the impact of both effects on the link performance are described. In the case of ISI, the analysis highlights the advantages of the statistical approach over the worst-case one in terms of the insight offered to the designer and computation time. In the case of jitter, the picture is less clear, as the two most recent techniques available address modeling requirements of different link architectures and are quite complex to implement into a statistical approach.

- Chapter 3 describes the statistical approach proposed in this thesis to model ISI and jitter in HSSI and its implementation into a MATLAB program. This approach allows for an accurate modeling of the transmitter pulse shape, a feature that is missing in other statistical techniques due to the non-trivial problem of dealing with transmitter non-linearity. Validation by means of comparison with other simulation approaches follows. Its advantage in dramatically reducing the simulation time over traditional Spice-like techniques is pointed out, whereas a critical discussion of the limitations of the proposed simulation procedure in handling impedance discontinuities in the link is provided.

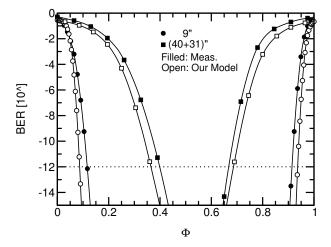

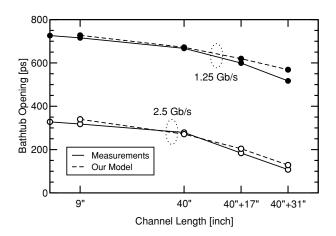

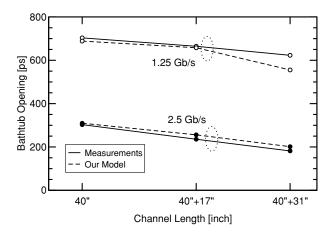

- Chapter 4 focuses on the verification of the proposed technique by comparison with experimental data from a high-speed test system (1.25 and 2.5 Gb/s). The agreement in terms of the eye diagrams and bathtub opening for various channel lengths is discussed, with satisfactory results.

- Chapter 5, by means of the review of recent works on high speed transmitters, discusses the clear improvement in the power efficiency of transmitters when adopting the Voltage-Mode topologies in place of the traditional CML implementations, thanks to their potential for lower power consumption and high swing capability. The details of the Source Series Terminated architecture are described, as it appears to be an attractive topology due to its potential in combining the advantage in power reduction of a Voltage Mode (VM) driver to a design completely based on digital switching techniques that cope well with nowadays deca-nanometer technologies.

- Chapter 6 provides the implementation details of a high speed transmitter. Design choices to face challenging targets in terms of power dissipation reduction, achievable data rate and voltage swing are discussed. Experimental verification on fabricated prototypes is also reported. Measurements draw a two-fold picture. For some of the relevant transmitter design figures the performance observed on the prototypes match very well simulation expectations. However, poor performance are observed in terms of eye diagram aperture. This aspect is object of in-depth investigation with detailed analysis of the physical layout and additional circuit simulations to target the root cause. Explanation of poor eye performance will be finally given in the closing part of the Chapter, with also directions for future improvement of the design.

# Chapter 2

# Modeling of ISI and Jitter in High Speed Links

Modeling of HSSI has become an active field of research in the last fifteen years, in parallel with the capability of modern integrated circuit technology to sustain the demand for continuously increasing data rates. As the performance of the links was ramping up at each technology node and the design margins were becoming more and more difficult to maintain, new modeling techniques and tools to accurately predict link performance have become necessary for successful first silicon. Traditionally the link signaling performance simulation involved time-domain simulations using random data sequences as inputs. Unfortunately, this approach does not assure that the worst case transmission is covered, given the fact that only small subsets of data pattern can be tested within a reasonable simulation time. This picture worsens when increasing the data rate and, as a consequence, also the channel interference: the channel response settling time becomes very long, imposing to simulate longer data patterns. In this way the combinations of bits to be tested increases exponentially, thus making the time domain approach rapidly unfeasible.

In this chapter the HSSI modeling approaches available in literature to model the effects of ISI will be reviewed. The available solutions to the problem of including jitter in the simulations will be reviewed too. This chapter is useful for the reader to fully understand the approach proposed in this thesis to develop a novel model for serial links, that will be object of the next Chapter 3.

# 2.1 Intersymbol Interference Modeling

Many approaches have been proposed for the modeling of ISI. The most relevant are described in the following pages.

## 2.1.1 Peak Distortion Analysis

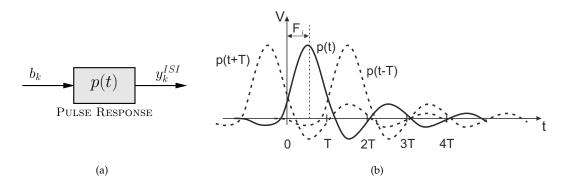

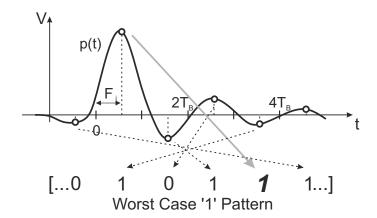

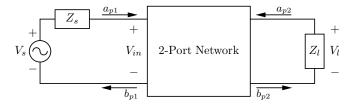

In a serial communication system (Figure 2.1(a)), we can define the pulse response p(t) as the response of the channel to a pulse at its input of duration equal to the bit time T. Assuming that the physical channel is Linear and Time Invariant (LTI), the signal  $y^{ISI}(t)$  at its output

can be represented by the following expression (see Figure 2.1):

$$y^{ISI}((k+\Phi_i)T) = \sum_{j=-\infty}^{\infty} b_{k-j} p((j+\Phi_i)T)$$

(2.1)

where k and j are integers,  $\Phi_i$  a number between 0 and 1 that can be considered as a phase inside T and  $b_k$  are the symbols voltage at the output of the transmitter<sup>1</sup>. The presence of ISI means that p(t) extends outside the symbol period, causing portion of the signal of a bit to disturb the nearby bits.

**Figure 2.1:** (a) Block diagram of the serial link model based on the pulse response p(t) of the channel. (b) ISI is due to p(t) extending outside T and disturbing neighboring bits.

The first approach proposed to efficiently model the effects of ISI was the Peak Distortion Analysis [33,34]: it just observes, based on the principles of communication theory [35], that a worst-case eye diagram for a serial link could be extracted as a sum of all the interference sources. When the only source of interference is ISI, the worst-case for, e.g., a '0' is when the pattern of neighboring bits is such that the respective portion of responses adds over the '0' bit voltage level that one would have in absence of ISI. In this way we can identify a worst-case '0' ( $s_0(\Phi_i T)$ ) and a worst-case '1' ( $s_1(\Phi_i T)$ ) and define the area comprised between them as the worst-case eye  $e(\Phi_i T)$ :

$$s_0(\Phi_i T) < e(\Phi_i T) < s_1(\Phi_i T) \quad \text{for} \quad 0 \le \Phi_i \le 1.$$

(2.2)

In other words,  $s_0(\Phi_i T)$  is the voltage level observed at the receiver side of the channel given that the transmitted bit is a '0' and the data pattern surrounding it is such that each unit portion of the tail of the channel response sums over the '0' bit voltage that one would have in absence of ISI. This concept can be mathematically expressed using the following:

$$s_{1}(\Phi_{i}T) = p(\Phi_{i}T) - \sum_{\substack{k=-\infty\\k\neq 0}}^{\infty} |p((\Phi_{i}-k)T)|$$

$$s_{0}(\Phi_{i}T) = -p(\Phi_{i}T) + \sum_{\substack{k=-\infty\\k\neq 0}}^{\infty} |p((\Phi_{i}-k)T)|$$

(2.3)

Here we use the absolute value because if  $p((\Phi_i - k)T) > 0$  the worst-case ISI contribution is given by a '1' bit, whereas if  $y((\Phi_i - k)T) < 0$  it is given by a '0' bit (thus a -1 symbol). Note

<sup>&</sup>lt;sup>1</sup>In this Chapter and in the following ones we will always refer to NRZ signaling systems with  $b_i = +1$  for bit '1' and  $b_i = -1$  for bit '0', i.e. the channel response to a '1' bit is p(t) and to a '0' bit is -p(t).

that using this principle it is also possible to find out the data pattern which is responsible of the worst-case eye, as shown as an example in Figure 2.2. Once the worst-case diagram has been calculated, an error-free transmission is possible if the data is sampled choosing a threshold voltage  $V_{th}$  and a sampling phase  $\phi$  contained inside  $e(\Phi_i T)$ . This approach is quite

Figure 2.2: Example of how to extract the worst-case '1' pattern for a given  $\Phi_i$  from the channel pulse response [34]. The sign of each sample  $p((\Phi_i - k)T)$  determines the value the  $k^{th}$ -bit must assume for the worst-case. As an example, the sample  $p((\Phi_i - 2)T)$  is positive, thus the worst-case condition occurs when 2 bits before the one of interest is transmitted a '0' bit: in this way the voltage  $p((\Phi_i - 2)T)$  subtracts to  $p(\Phi_i)$ , causing a reduction of the sampling margin of the '1' bit.

simple, of straightforward application and it requires very limited computation time. On the other hand the insight given by the worst-case eye diagram is quite limited and can also lead to an over-design of the link. In fact, the probability to observe the worst-case pattern during data transmission is exponentially decreasing with the increase of the channel length and of the data rate, thus designing for very low probabilities may be highly inefficient in terms of silicon area and power.

## 2.1.2 Statistical Analysis based on the Single Bit Response

The statistical analysis based on the Single Bit Response (SBR) of the channel has been proposed to go beyond the worst-case approach by adding statistical information to the ISI eye diagram [33, 36, 37]. Final target is to calculate all possible eye contours that we can observe in an eye diagram depending on the data pattern, not just one contour representing the worst-case data transmission condition, and assign to each contour its respective probability to appear. To do this, we have to find a way to represent voltage quantities in the statistical domain. In particular, two questions must be answered:

- 1. How can we represent voltage values in the probability domain?

- 2. What are the operators in the probability domain associated to algebraic operations (sum, subtraction) of voltage values?

To answer the first question we note that a voltage  $v_1$  can be represented by means of a Dirac's delta centered at  $v_1$ : in this way a Probability Distribution Function (PDF), function of v, is constructed such that all voltage values except  $v_1$  have probability equal to zero. This representation allows to easily represent situations in which multiple voltage values are

admissible at the same time, e.g. in case we want to represent the voltage values produced by different data patterns. In this case, the PDF consists of multiple Dirac's delta centered at each voltage value, with amplitudes equal to the probability to observe each value.

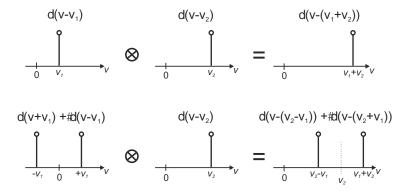

Once assessed a proper representation of voltages through PDFs, the operator that allows to reproduce algebraic operations on voltages is the *convolution*. In fact, if we apply the convolution between two Dirac's delta centered respectively at  $v_1$  and  $v_2$ :

$$pdf_{v_{1}}(v) * pdf_{v_{2}}(v) = \int_{-\infty}^{\infty} pdf_{v_{1}}(v - \mu) \cdot pdf_{v_{2}}(\mu) d\mu$$

$$= \int_{-\infty}^{\infty} \delta(v - v_{1} - \mu) \cdot \delta(\mu - v_{2}) d\mu$$

$$= \delta(v - (v_{1} + v_{2})) = pdf_{v_{1} + v_{2}}(v).$$

(2.4)

So, we obtain a Dirac's delta centered at  $v_1 + v_2$ , as also shown in the top graph of Figure 2.3. Thus the convolution operation is able to represent in the probability domain sum and subtractions between voltages.

**Figure 2.3:** Convolution operation between PDFs representing voltage samples: the convolution of two Dirac's delta centered at  $v_1$  and  $v_2$  gives a Dirac's delta centered at  $v_1 + v_2$  (top). The convolution of a PDF made of two Dirac's delta ad  $\pm v_1$  and a single Dirac's delta at  $v_2$  gives two Dirac's delta at  $v_2 - v_1$  and  $v_2 + v_1$  (bottom).

Let's now assume that we want to consider the data transmission of two bits, and we want to represent the ISI effect of the first transmitted bit, that could be either a '0' or a '1', on the following bit, that we assume to be a '1'. Under the assumption that each bit could be a '0' or a '1' with equal probability, and that the bit value is independent from the other bits in the data stream (i.e. random sequence with no coding), the voltage  $v_2$  we would have for the '1' bit in absence of ISI will be disturbed by the tail of the first transmitted bit, as stated by eq. 2.1 and as shown in Figure 2.1. Assuming  $v_1$  is the voltage given by p(t) at T, if the bit is a 0, we have to subtract  $v_1$  to  $v_2$ , while if the bit is a '1', we have to add  $v_1$  to  $v_2$ . The two resulting voltages,  $v_2 + v_1$  and  $v_2 - v_1$ , have a 1/2 probability to be observed. We can represent this accumulation of ISI in the following way (see bottom graph of Figure 2.3):

- 1. construct a PDF for the '1' bit as a Dirac's delta  $\delta(v-v_2)$ ;

- 2. construct a PDF that accounts for all possible ISI voltages due to the first transmitted bit as:

$$pdf = \frac{1}{2} \left[ \delta(v - v_1) + \delta(v + v_1) \right]$$

(2.5)

3. convolve the two PDFs. The result of the convolution represents the possible voltages assumed by the '1' bit depending on the sign of the first transmitted bit.

This result is very important, because it provides us with all we need to compute ISI in the statistical domain.

The SBR approach [33, 36, 37] exploits the above results and determines the Bit Error Rate (BER) as a function of the data rate through the construction of a distribution plot that relates the BER to the sampling point, intended as the combination of threshold voltage and sampling time. The first step towards determining the BER is the calculation of a PDF of ISI for each time instant *t* of the eye diagram.

The PDF of ISI is calculated by convolving the individual ISI samples, determined from the channel pulse response p(t) as in the worst-case analysis, using the following:

$$pdf_{k+1}(\mu,\Phi_i) = \begin{cases} \frac{\delta(\mu - p((\Phi_i - k)T)) + \delta(\mu + p((\Phi_i - k)T))}{2} \otimes pdf_k(\mu,\Phi_i) & \text{if } k \neq 0\\ pdf_k(\mu,\Phi_i) & \text{if } k = 0 \end{cases}$$

(2.6)

where the calculation must be done from  $k = -\infty$  to  $k = \infty$ . In eq. (2.6) we are:

- 1. associating to each ISI voltage sample  $p((\Phi_i k)T)$  its respective representation in the probability domain in the form of two Dirac delta functions centered at  $\mu = \pm p((\Phi_i k)T)$ . The initial condition for the calculation is  $pdf_{-\infty}(\mu, \Phi_i) = \delta(\mu)$ , which follows from  $p(-\infty) = 0$ .

- 2. accumulating all ISI samples into a unique PDF by means of sequential convolution operations, identified by the symbol  $\otimes$  in eq. (2.6).

Once determined  $pdf_{k=+\infty}$ , we have to couple it to the voltage levels of the '1' and '0' bit:

$$pdf(0)(\mu, \Phi_i) = pdf_{k=+\infty}(\mu + p(t), \Phi_i) pdf(1)(\mu, \Phi_i) = pdf_{k=+\infty}(\mu - p(t), \Phi_i).$$

(2.7)

which is just a shift of  $pdf_{k=+\infty}$  at p(t) (in the case of a '1' bit) or -p(t) (in the case of a '0' bit).

We then combine pdf(0) and pdf(1) as:

$$pdf_{ISI}(\mu, \Phi_i) = \frac{1}{2} \left[ pdf(0)(\mu, \Phi_i) + pdf(1)(\mu, \Phi_i) \right]$$

(2.8)

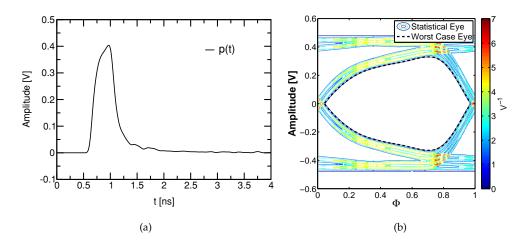

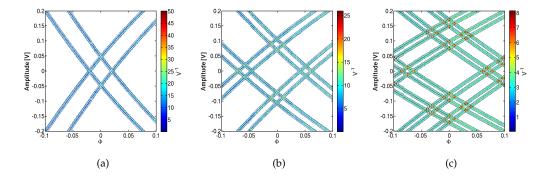

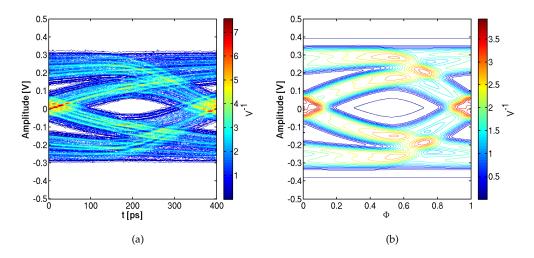

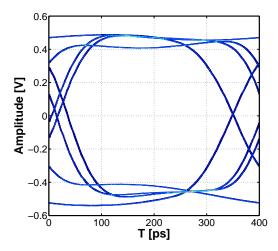

where we have assumed a 50% probability for both bit '0' and '1', and we contour plot it on the  $(\mu, t)$  plane, as shown in Figure 2.4(b), obtaining a statistical eye diagram analogous to the one produced by an oscilloscope.

We can now calculate the BER, defined as the total probability of observing at the end of the channel a bit different from the transmitted one, i.e. in the case of a transmitted '1' we have  $\mu < v$ , where v is the sampling voltage. Using  $pdf(0)(\mu, \Phi_i)$  and  $pdf(1)(\mu, \Phi_i)$  calculated above, the BER is obtained using:

$$BER(v,t) = \int_{-\infty}^{v} \frac{pdf(1)(\mu,\Phi_i)}{2} d\mu + \int_{v}^{\infty} \frac{pdf(0)(\mu,\Phi_i)}{2} d\mu.$$

(2.9)

The first term of the equation determines the error probability of a '1' bit as the Cumulative Distribution Function (CDF) (thus a sum of probabilities) from  $-\infty$  to v of  $pdf(1)(\mu,\Phi_i)$ . Similarly the second term of the equation determines the error probability of a '0' bit as the CDF from v to  $\infty$  of  $pdf(0)(\mu,\Phi_i)$ .

The calculated BER(v,t) can be contour plotted in the (v,t) plane: in this way the points on the (v,t) plane associated to a given BER level, e.g.  $10^{-9}$  or  $10^{-12}$ , can be visualized in

**Figure 2.4:** (a) Simple example of pulse response at 2.5 Gb/s of a channel with  $S_{DD12} = -4.2$  dB at the Nyquist frequency. (b) Contour plot of the  $pdf(v,\Phi)$  extracted with the SBR statistical ISI algorithm compared to the worst-case eye (black).

the same way of an eye obtained with the worst-case approach. This approach gives the designer the flexibility of accounting for reasonable design margins by choosing the target BER required by the application, thus saving in silicon area and power when some errors can be tolerated in the application, as most of the HSSI standards do nowadays.

#### 2.1.3 Transitions-based Analysis

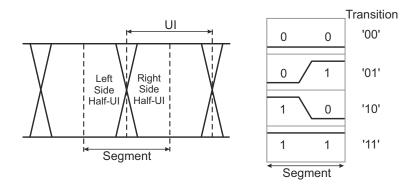

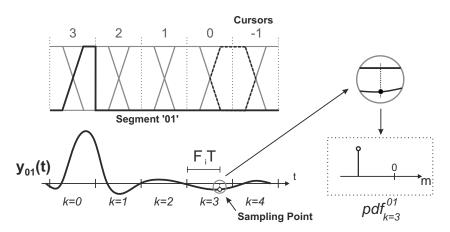

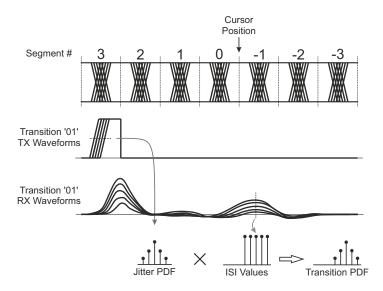

This approach uses as basis for ISI modeling the *transmit* segments, as opposed to transmit pulses employed in the SBR approach described in Section 2.1.2. As shown in Figure 2.5, transmit segments are defined as the transition from the left-side half-UI level to the right-side half-UI level. The transmitted data stream is divided into segments of length equal to one UI centered at the nominal data transition instant. The idea behind this modeling scheme is to compute the ISI contribution of the individual segments and then appropriately combine them to get the total effects of ISI at the channel output, represented by means of a statistical distribution [38,39].

**Figure 2.5:** Segment definition with respect to the UI (left). The four transmit segment in the case of binary NRZ signaling [38] (right).

The first step to implement the transition-based approach is to tabulate all possible seg-

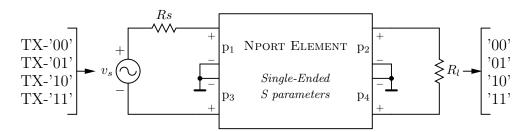

ments as combinations of the initial and final transition voltage values. For instance, in the very simple case of a binary NRZ signaling scheme the possible voltage values are only two, thus the possible combinations are four, as shown in Figure 2.5. In case of a larger number of voltage levels in the TX data stream, i.e. when Pulse Amplitude Modulation (PAM) or transmit equalization are employed, the number of segments to handle is larger. For each segment in this table, a waveform is constructed. The voltage value defined over the UI across the nominal transition instant is equal to the segment itself, while outside this time interval the waveform must not contribute, thus the voltage is equal to zero, as shown in Figure 2.6.

**Figure 2.6:** Construction of the transition PDF for the segment '01' at cursor k = 3. The first step is the construction of the segment waveform (top). After computing the channel response  $y_{01}(t)$ , the sampling process at multiples of UI identifies the voltage samples to be considered to build the transition PDFs for each cursor [39] (bottom).

The computation of the channel response to each segment is the following step in the procedure, and it is done by convolving the segment with the channel impulse response. The resulting waveform is then sampled at multiples of the UI, and a transition PDF is constructed for each voltage sample, in the form:

$$pdf_k^{seg} = \delta(\mu - y_{seg}(t - kT))$$

(2.10)

where  $y_{seg}(t)$  is the channel response to one of the segments. Once the PDFs of all precursors and postcursors<sup>2</sup> have been constructed, they are combined to compute the total ISI contribution. This operation is the most delicate of the whole procedure. In fact, at this step the samples coming from the responses to the different segments must be properly combined in a sequential fashion, taking care that in the cascade of segments the final value of one transition coincides with the initial value of the neighboring one. If this is not verified, we have a bit changing exactly in the middle of a UI, which is not admissible.

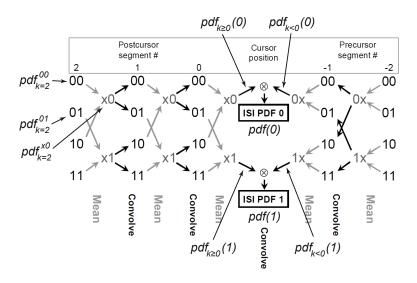

Figure 2.7 shows the sequential operations in the case of two precursors and two postcursors. At each step, starting from the last significant postcursor segment (k = 2 in the figure), the PDFs are averaged and then combined by means of convolution with appropriate transition PDFs of the neighboring segment. To understand this basic operation, let's consider the postcursor segment '2' (see Figure 2.7):

<sup>&</sup>lt;sup>2</sup>In the framework of ISI modeling the word *cursor* is used to identify the voltage samples at k multiples of UI in a generic channel response. These are the samples that must be accumulated to account for the total ISI at t. *Precursors* are the samples with k < 0 and *postcursors* the samples with k > 0, respectively. The cursor corresponding to k = 0 represents the voltage at the output of the channel in absence of ISI.

**Figure 2.7:** Diagram of the sequential accumulation of ISI in the simple case of two postcursors and two precursors only [38].

- 1. we average  $pdf_{k=2}^{00}$  (segment "00") with  $pdf_{k=2}^{10}$  (segment "10"), obtaining a temporary PDF  $pdf_{k=2}^{\times 0}$ ;

- 2. we convolve the latter with  $pdf_{k=1}^{01}$  of segment "01" at cursor '1'. That means we are computing the ISI contribution of all possible data patterns that have a 0-to-1 transition 1UI before cursor '0'.

- 3. we repeat steps 1. and 2. for all possible combinations of segments until coming back to cursor '0'.

By repeating this procedure we can calculate separately two PDFs for bit 0 ( $pdf_{k\geq 0}(0)$ ) and for bit 1 ( $pdf_{k\geq 0}(1)$ ) that take into account ISI effects due to all possible data patterns leading to a 0 bit or to a 1 bit at cursor '0'. To end the ISI calculation having considered all possible data patterns we apply the same procedure also for all the precursors. The last step is the convolution of  $pdf_{k<0}(0)$  and  $pdf_{k<0}(1)$ , see again Figure 2.7, with respectively  $pdf_{k\geq 0}(0)$  and  $pdf_{k\geq 0}(1)$ . Like in the SBR-based statistical algorithm the result of the ISI computation are two separate PDFs, one referred to the bit '0' and one referred to the bit '1'.

The BER calculation is done analogously to eq. (2.7), using:

$$BER(v,t) = \frac{1}{2} \left[ \int_{-\infty}^{v} p df(1)(\mu,t) d\mu + \int_{v}^{+\infty} p df(0)(\mu,t) d\mu \right]$$

(2.11)

where  $pdf(0)(\mu,t)$  and  $pdf(1)(\mu,t)$  are the PDFs for bit 0 and bit 1, respectively, resulting from the sequential algorithm.

# 2.2 Jitter

In the literature, jitter is a concept shared among clock signals and data signals. While intuitively we are referring in both cases to the time deviation of a signal with respect to a reference, the jitter definitions used in the two applications are quite different. In the following of the thesis we will deal mainly with serial data, so we will use mostly the definitions

belonging to this field, like Random Jitter (RJ), Deterministic Jitter (DJ), Duty Cycle Distortion (DCD), and so on. Nevertheless most of the jitter in a serial data stream stems directly from the clock signal driving the transmitter, thus we will encounter definitions as "period jitter" and "absolute jitter". For this reason, we will firstly introduce here the most used definitions of jitter in the field of clocking and, afterward, we will describe the jitter classification adopted when dealing with serial data.

## 2.2.1 Clock Jitter

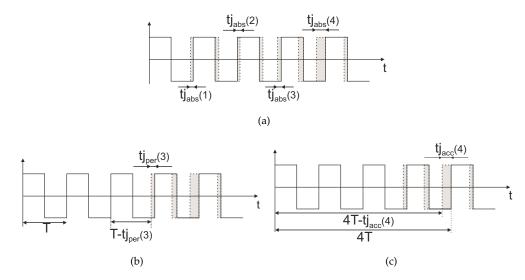

When dealing with clocking applications and their timing non-idealities, a number of definitions are given depending on the way jitter is measured [40,41]:

**Absolute Jitter:** time displacement between the edge of an ideal clock and the real one. It is usually indicated as  $j_{abs}$  (Figure 2.8(a)).

**Period Jitter:** time variation of the clock period, measured as the time between one clock edge and the preceding one. It is indicated as  $j_{per}$  (Figure 2.8(b)).

**Accumulated Jitter:** time displacement of one clock edge relative to a starting edge of the same clock more than one clock cycle away. Accumulated jitter is a function of the number of cycles m and it is indicated as  $j_{acc}(m)$ . If m = 1 we have  $j_{acc}(1) = j_{per}$  (Figure 2.8(c)).

For all these jitter types the value could be provided as rms,  $1\sigma$ ,  $3\sigma$ , peak or peak-to-peak.

**Figure 2.8:** Clock jitter definitions: (a) absolute jitter  $j_{abs}$ , (b) period jitter  $j_{per}$  and (c) accumulated jitter  $j_{acc}$  [40]. The solid line represents the ideal unjittered waveform.

## 2.2.2 Jitter in Serial Data

In serial data communications, jitter is defined as the deviation of the timing properties of a signal with respect to a specified reference time and, historically, it is measured at the nominal switching threshold of the signal [42]. Jitter classification into categories is needed because jitter components accumulate differently in the link depending on their characteristics. Moreover breaking jitter into its various components allows to develop techniques

to support budgeting of jitter in the design phase and leads to an efficient diagnosis of the causes of the jitter.

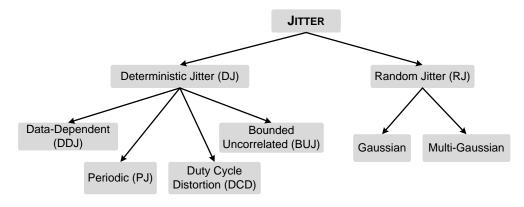

The first main distinction of jitter in serial communications is between *bounded* and *un-bounded* jitter. Bounded jitter has the property that no population exists beyond specific limits regardless of the number of events observed while for unbounded jitter some finite population exists at all values of jitter (assuming an infinite sample size). By definition, all bounded jitter is *deterministic* jitter (DJ) and all unbounded is *random* jitter (RJ) [42].

Deterministic jitter could be further divided into different classes [42–44] (see also Figure 2.9):

**Duty Cycle Distortion (DCD):** is jitter due to different pulse widths for '1' bits compared to '0' bits. It is most easily observed in a clock-like data pattern and has a dual Dirac distribution. DCD does not depend on the data pattern.

**Data Dependent Jitter (DDJ):** is jitter that is correlated with the data pattern. Data Dependent Jitter (DDJ) is the effect in the time domain of the ISI phenomenon as we will see later in Section 2.3.

**Periodic Jitter (PJ):** is jitter that repeats in a cyclic fashion. Since any periodic waveform can be decomposed into a Fourier series of harmonically related sinusoids, this kind of jitter is sometimes called sinusoidal jitter. It is caused by external noise sources coupling into a system, such as switching power supply noise or a strong local RF carrier.

**Bounded Uncorrelated Jitter (BUJ):** it is usually caused by crosstalk coupling from adjacent interconnects. It is bounded in amplitude and uncorrelated to the data pattern and has a random distribution similar to RJ, but with limited spread (no tails).

Random jitter is Gaussian in nature [42]; thus, it can theoretically reach any magnitude (within physical limits). It is expressed as a single Gaussian distribution or a combination of multiple Gaussian distributions.

Deterministic jitter is measured as a peak to peak value for any distribution, random jitter is given as rms.

Figure 2.9: Jitter hierarchy [1].

Jitter budgeting of a link is specified through Total Jitter (TJ). Due to the presence of bounded terms side by side to unbounded terms, total jitter is specified as the time interval where all but a specified fraction of the population falls. Given that a jitter occurrence outside the TJ time interval means a bit error during data transmission, the fraction of population to

specify is equal to the BER we can tolerate. Therefore, giving a TJ number without the respective BER value is meaningless. In modern link standards, e.g. PCIe [3], frequently the specified BER is  $10^{-12}$ . The TJ distribution is assumed to be a dual Dirac:

$$pdf_{tj}(t) = \frac{1}{2\sqrt{2\pi}} \frac{1}{\sigma_{rj}} \left\{ e^{-\left[\frac{(t-dj/2)^2}{2\sigma_{rj}^2}\right]} + e^{-\left[\frac{(t+dj/2)^2}{2\sigma_{rj}^2}\right]} \right\}.$$

(2.12)

where dj is the peak-to-peak DJ value and  $\sigma_{rj}$  is the rms RJ value. To calculate TJ we thus have to calculate the CDF of the dual Dirac distribution. We can also use the approximated relation [3]:

$$tj = dj + 2Q_{BER} \cdot \sigma_{rj}. \tag{2.13}$$

*Q*<sub>BER</sub> is a function of BER, and is calculated using the inverse error function [45]:

$$Q_{BER} = \sqrt{2} \cdot erf^{-1} \left[ 1 - \frac{1}{\rho_T} BER \right]$$

(2.14)

where  $\rho_T$  is the data transition density, which is equal to 1/2 if we assume the same probability for bit '0' and '1'. Some significant  $Q_{BER}$  values are 5.99 for BER=  $10^{-9}$ , 7.04 for BER=  $10^{-12}$  and 7.94 for BER=  $10^{-15}$ .

## 2.2.3 Jitter Modeling

In a high speed serial link design, margins at the receiver are equivalently affected by ISI, due to the band limited nature of the channel, and by timing uncertainty of the clock and data. Accounting for jitter is therefore as important as ISI when focusing on the prediction of the link performance. Numerous papers have been devoted to this topic, proposing different methodologies for handling all the various mechanisms responsible for deterministic and random jitter. In the following the main approaches reported in literature are reviewed.

#### Receiver Sampling Distribution Model

Historically, the receiver sampling distribution model is the first model developed to account for jitter in HSSI [36, 37], and it is also the simplest approach. It is based on the assumption that all jitter sources in a link could be treated as uncertainty in the receiver sampling distribution, no matter whether the jitter comes from the transmitter or from the receiver itself. This means that transmitter jitter and receiver jitter are considered as uncorrelated, thus possible jitter tracking effects of the Clock and Data Recovery (CDR) circuit are neglected [46] with possible overestimation of jitter in the link. Moreover, when considering the transmitter jitter the same way as receiver sampling uncertainty, possible effects of the channel limited bandwidth over jitter are ignored. Therefore, the so-called jitter amplification, reported in [47,48], is not taken into account, causing possible under-estimation of jitter in the link model.

On the other hand, the receiver sampling distribution model has the great advantage of being of straightforward implementation in a ISI statistical simulation framework. In fact, it is possible to calculate a PDF that takes into account the combined effects of ISI and jitter [33,37,49], starting from the PDF of ISI  $pdf_{ISI}(v,t)$  calculated with one of the statistical approaches described in Section 2.1 and the PDF of jitter  $(pdf_{jitter}(t))$ , using:

$$pdf(v,t) = \int_{-\infty}^{\infty} pdf_{ISI}(v,t-\tau) \cdot pdf_{jitter}(\tau)d\tau$$

(2.15)

which is a convolution of the two PDFs in the time domain. Note that when choosing  $pdf_{jitter}(\tau)$  one must not account for DDJ effects of the channel, because they are already included in the ISI analysis, as we will demonstrate in Section 2.3.

#### **Equivalent Voltage Noise Model**

This alternative approach to jitter modeling in the statistical domain stems from the observation [34,36,50,51] that the transmitted pulse train x(t) can be written as:

$$x(t) = \sum_{k=-\infty}^{\infty} (b_k - b_{k-1}) \cdot u(t - kT)$$

(2.16)

where u(t) is the unit step function, defined as u(t) = 1 for t > 0 and u(t) = 0 otherwise. Noting that the output of the channel can be characterized by its impulse response h(t), the channel output can be determined by convolving the input pulse train with the channel impulse response h(t):

$$y^{ISI}(t) = x(t) \otimes h(t) = \sum_{k=-\infty}^{\infty} [(b_k - b_{k-1}) \cdot s(t - kT)]$$

(2.17)

where  $s(t) = u(t) \otimes h(t)$  is the step response of the channel.

The first step to account for jitter is to observe that at transmitter side the time instants of the data edges are not ideal but affected by transmitter jitter  $\epsilon_k^{TX}$ , and rewrite eq. (2.17) as:

$$y(t) = \sum_{k} (b_k - b_{k-1})s(t - \epsilon_k^{TX} - kT).$$

(2.18)

At the receiver side the data output by the channel is sampled at jittered time instants  $t_m = mT + \epsilon_m^{RX}$ . The sampled signal  $y_m$  can be written as:

$$y_m = \sum_{k} (b_k - b_{k-1}) s(\epsilon_m^{RX} - \epsilon_k^{TX} + (m-k)T).$$

(2.19)

Note that to derive this expression no approximation has been introduced, thus completely describes data transmission over a band-limited channel in the presence of jitter. Note also that  $\epsilon_m^{RX}$  is not a function of the index k because it does not alter the transmitted bit as it happens for  $\epsilon_k^{TX}$ . If we now use the Taylor series expansion and we truncate it to the first order we obtain:

$$y_{m} \cong \sum_{k} (b_{k} - b_{k-1})s((m-k)T) +$$

$$+ \sum_{k} (b_{k} - b_{k-1})\epsilon_{k}^{TX}h_{m-k} + \epsilon_{m}^{RX} \sum_{k} (b_{k} - b_{k-1})h_{m-k}$$

$$= \sum_{k} b_{k}p_{m-k} + n^{TX} + n^{RX}$$

(2.20)

where  $h_{m-k}$ , obtained by a time derivation of the step response  $s\left((m-k)T\right)$ , is the data-rate sampled impulse response of the channel, while  $n^{TX}$  and  $n^{RX}$  are defined as the Equivalent Voltage Noise (EVN) terms for transmitter and receiver jitter, i.e. the contribution to the received voltage due to transmitter and receiver jitter, respectively. The term  $\sum_k b_k p_{m-k}$  represents the received signal in absence of jitter. Eq. (2.20) shows that the EVN terms could be determined independently from ISI calculation.

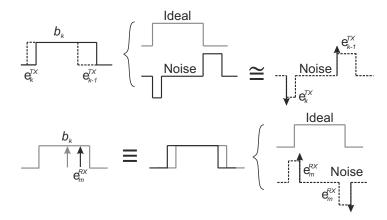

To better understand the model for jitter provided by eq. (2.20), we may refer to Figure 2.10. The top part shows how a data pulse affected by jitter at the transmitter side can be

**Figure 2.10:** Models for transmitter (top) and receiver (bottom) jitter in the framework of the equivalent voltage noise model [50].

represented as the sum of an ideal pulse representing the data without jitter, and two pulses of time amplitude equal to the jitter magnitude placed at the ideal time crossings. If TX jitter affecting the data is small, these pulses can be approximated as impulses (Dirac's delta) whose amplitude is the jitter magnitude. The same approximation is used for the receiver jitter, as shown on the bottom plot of Figure 2.10. The sampling time uncertainty could also be viewed as a rigid time shift of the data pulse due to  $\epsilon_m^{RX}$ , which translate in the sum of an ideal data pulse and two pulses of  $\epsilon_m^{RX}$  width. Again if  $\epsilon_m^{RX}$  is small, the two pulses could be represented as impulses (Dirac's delta). We understand then that the first-order approximation of the Taylor series expansion in the conversion step from timing jitter to voltage impulses is limiting the accuracy of EVN model to small jitter only.

#### Segment-based Model

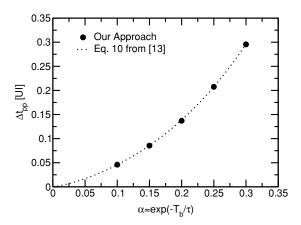

The segment-based approach to jitter modeling is tightly bound to the transition-based ISI analysis described in Section 2.1.3. In fact, the two approaches have been developed together in [38].

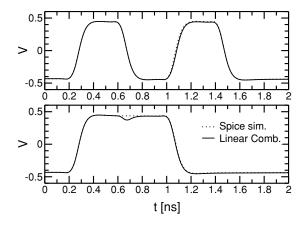

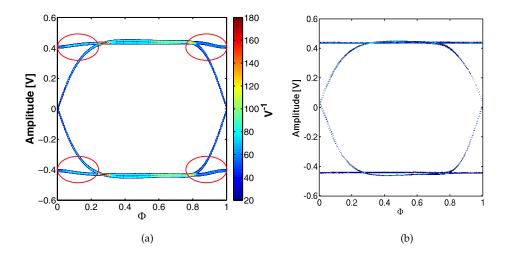

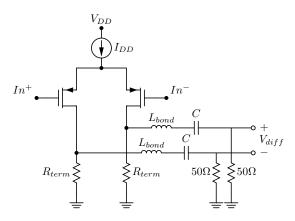

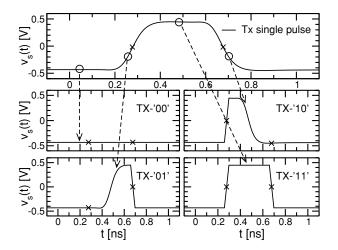

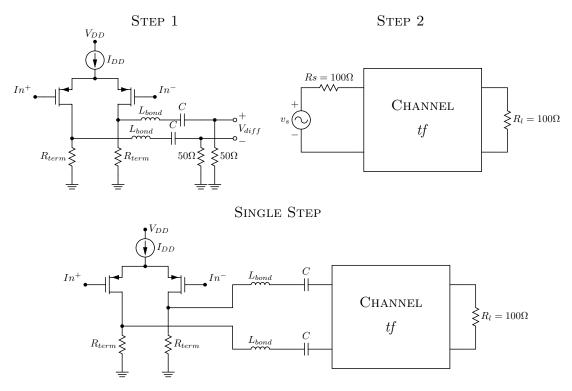

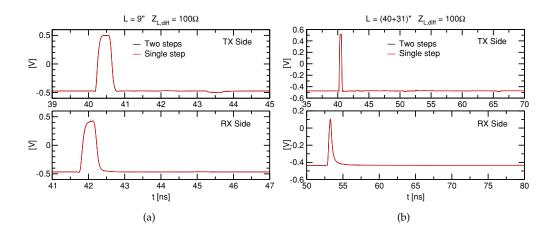

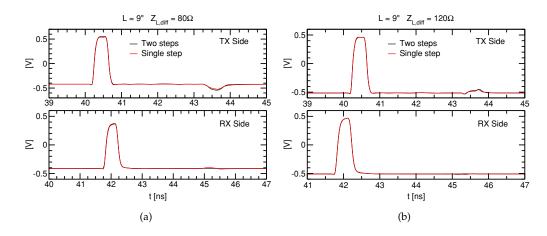

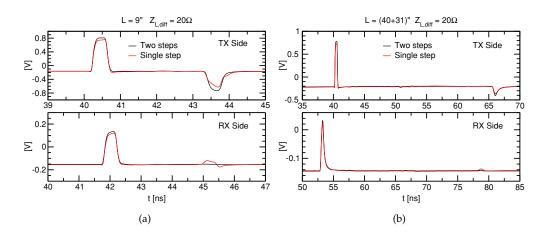

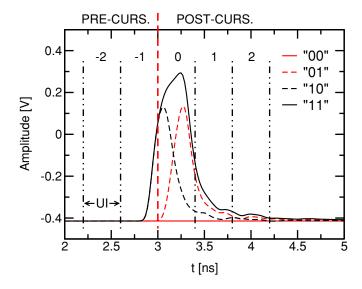

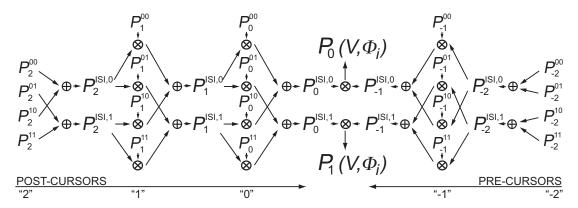

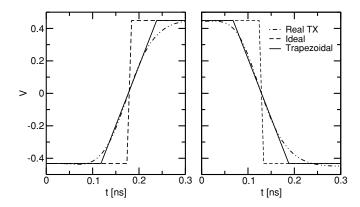

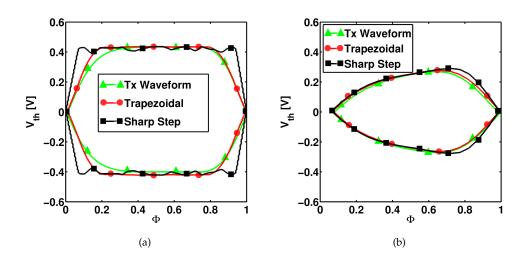

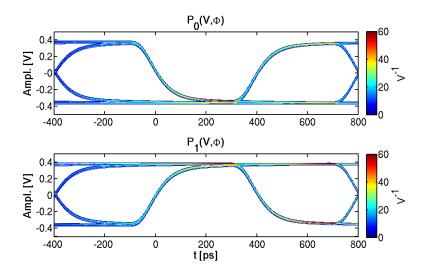

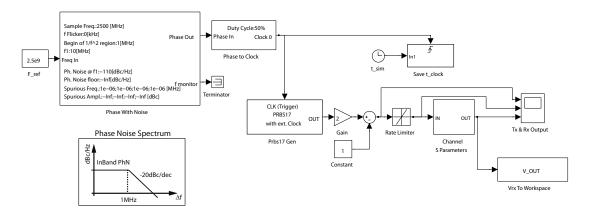

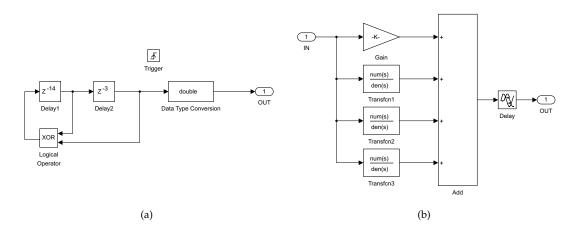

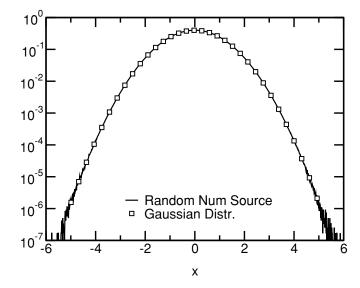

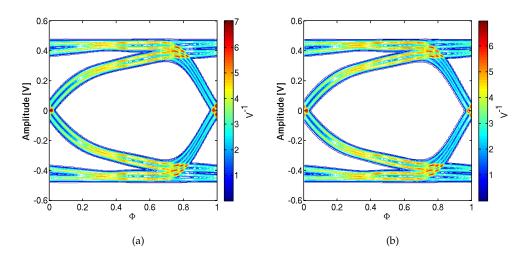

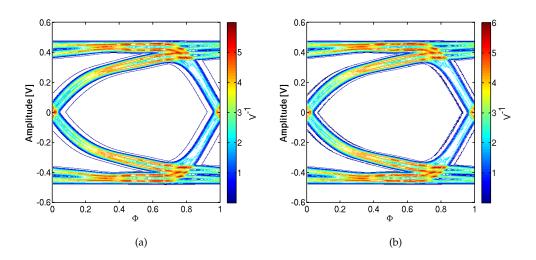

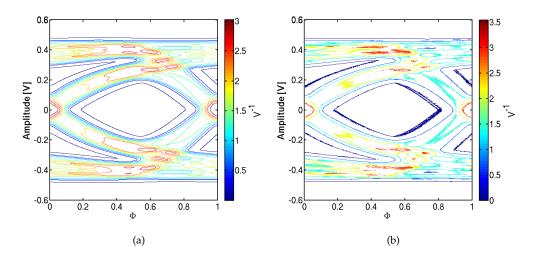

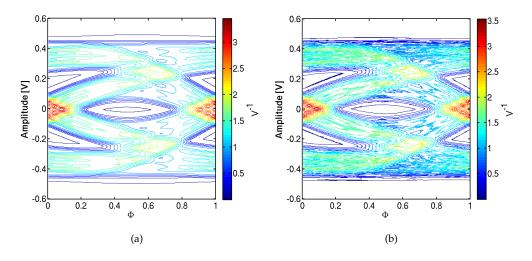

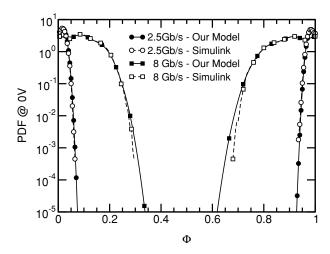

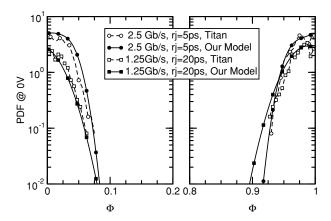

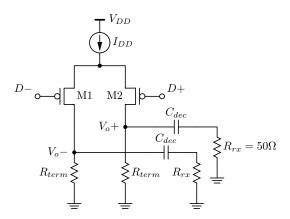

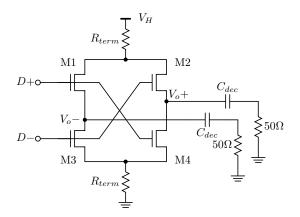

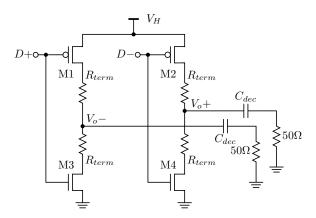

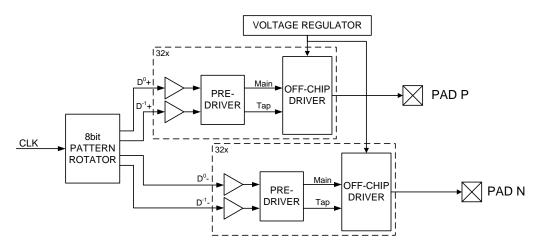

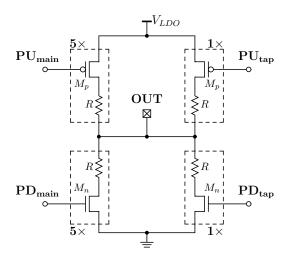

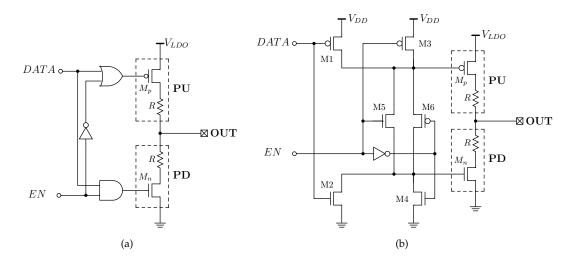

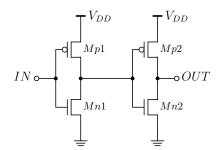

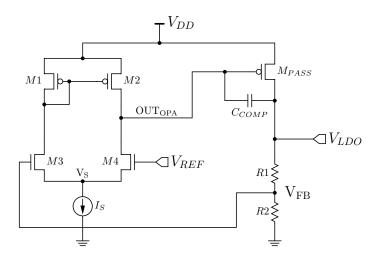

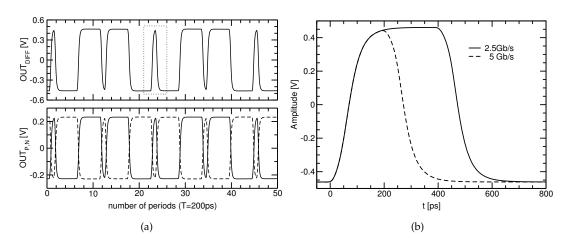

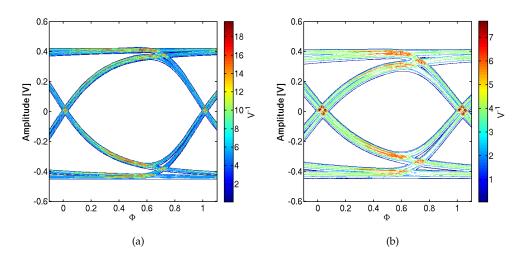

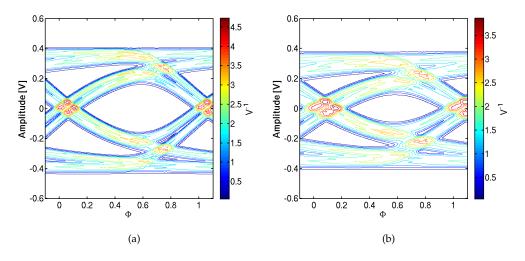

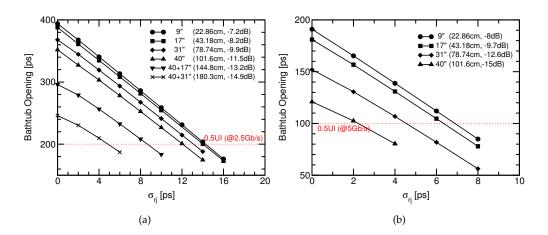

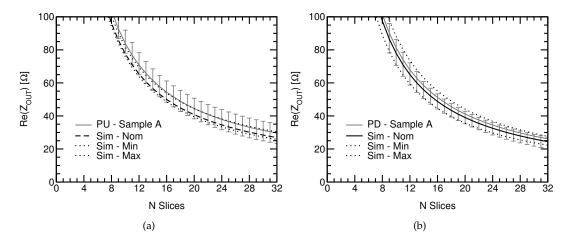

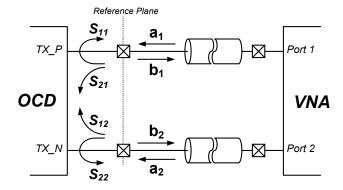

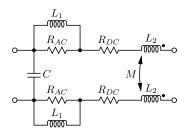

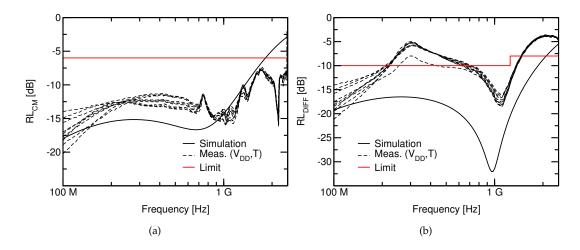

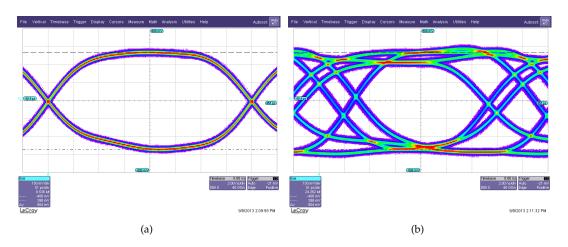

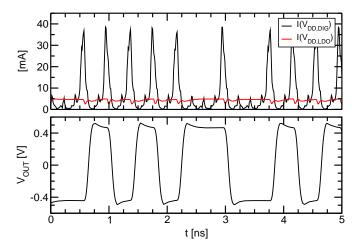

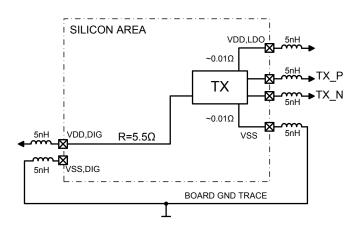

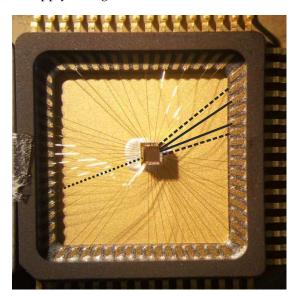

We have already shown how ISI is modeled in the transition-based method by means of the construction of segments representing all the possible transitions between voltage levels at the transmit side (see Figure 2.5). Now we have to consider that each transition is affected by jitter; thus, we have to take it into account when constructing the segments. This is done by considering a group of closely spaced segments instead a single one for each transition to model, as shown in Figure 2.11. The number of segments in the group depends on the TX jitter distribution, e.g. in Figure 2.11 the transition '01' has 5 segment shapes because its jitter PDF is discretized with 5 possible values. The channel responses to the segment group are then determined and sampled at each cursor. The different voltage samples obtained at each cursor position produce a PDF made of a group of Dirac's delta (see bottom of Figure 2.11) which, after multiplication with the jitter PDF, give the cursor transition PDF that binds ISI and TX jitter. Once the cursor transition PDFs for all the possible transitions have been determined, they are combined using the same sequential algorithm depicted in Figure 2.7. The advantage of this combined ISI and jitter modeling approach is that it produces a PDF accounting for both ISI and jitter, and also their interactions. The latter in particular is the missing element in the receiver sampling distribution approach.