# University of Udine

# INDUSTRIAL AND INFORMATION ENGINEERING PHD PROGRAM

# **Doctoral Dissertation**

# Digital Control of Power Converters and Drives for Hybrid Traction and Wireless Charging

PhD candidate:

| Prof. Roberto Petrella | Ing. Alessandro Pevere |  |  |

|------------------------|------------------------|--|--|

|                        |                        |  |  |

|                        |                        |  |  |

| Accademic              | Year 2014/2015         |  |  |

Supervisor:

"HARD WORK BEATS TALENT WHEN

TALENT DOESN'T WORK HARD."

(cit. KD)

Alla mia famiglia che mi ha sempre spronato a dare il meglio e alle persone che hanno sempre creduto in me.

# **ABSTRACT**

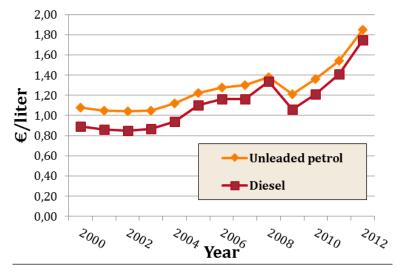

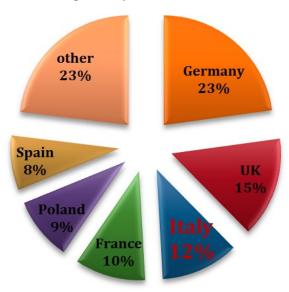

In the last years environmental issues and constant increase of fuel and energy cost have been incentivizing the development of low emission and high efficiency systems, either in traction field or in distributed generation systems from renewable energy sources.

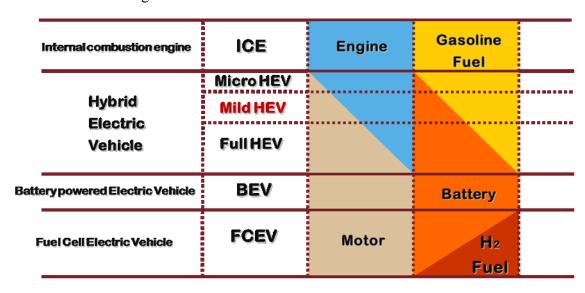

In the automotive industry, alternative solutions to the standard internal combustion engine (ICE) adopted in the conventional vehicles have been developed, i.e. fuel cell electric vehicles (FCEVs), hybrid electric vehicles (HEVs), plug-in hybrid electric vehicles (PHEV) or pure electric vehicles (EVs), also referred as battery powered electric vehicles (BEV).

Both academic and industry researchers all over the world are still facing several technical development areas concerning HEV components, system topologies, power converters and control strategies. Efficiency, lifetime, stability and volume issues have moved the attention on a number of bidirectional conversion solutions, both for the energy transfer to/from the storage element and to/from the electric machine side.

Moreover, along with the fast growing interest in EVs and PHEVs, wireless charging, as a new way of charging batteries, has drawn the attention of researchers, car manufacturers, and customers recently. Compared to conductive power transfer (usually plug-in), wireless power transfer (WPT) is more convenient, weather proof, and electric shock protected. However, there is still more research work needs to be done to optimize efficiency, cost, increase misalignment tolerance, and reduce size of the WPT chargers.

The proposed dissertation describes the work from 2012 to 2014, during the PhD course at the Electric Drives Laboratory of the University of Udine and during my six months visiting scholarship at the University of Michigan in Dearborn. The topics studied are related to power conversion and digital control of converters and drives suitable for hybrid/electric traction, generation from renewable energy sources and wireless charging applications. From the theoretical point of view, multilevel and multiphase DC/AC and DC/DC converters are discussed here, focusing on design issues, optimization (especially from the efficiency point-of-view) and advantages. Some novel modulation algorithms for the neutral-point clamped three-level inverter are presented here as well as a new multiphase proposal for a three-level buck converter. In addition, a new active torque damping technique in order to reduce torque oscillations in internal combustion engines is proposed here.

Mainly, two practical implementations are considered in this dissertation, i.e. an original twostage bi-directional converter for mild hybrid traction and a wireless charger for electric vehicles fast charge.

# TABLE OF CONTENTS

| 1 INTRODUCTION                                           | 1  |

|----------------------------------------------------------|----|

| 1.1 BACKGROUND                                           | 1  |

| 1.1 CONTRIBUTION OF THIS WORK                            | 4  |

| 1.2 Outline of the thesis                                | 4  |

| 1.3 List of publications                                 | 5  |

| 2 THREE-LEVEL NPC INVERTER                               | 6  |

| 2.1 Introduction                                         | 6  |

| 2.2 Multilevel converter history                         | 6  |

| 2.3 Multilevel structures                                | 7  |

| 2.3.1 Cascaded multi-cells                               | 7  |

| 2.3.2 Flying capacitor                                   | 9  |

| 2.3.3 Neutral-point clamped                              | 10 |

| 2.4 NPC CONTROL STRATEGIES                               | 12 |

| 2.4.1 Space vector modulations (SVM)                     | 12 |

| 2.4.2 Neutral-point balancing in SVM                     |    |

| 2.4.3 Carrier-based modulations (CBM)                    |    |

| 2.4.4 Optimal NP balancing regulator                     |    |

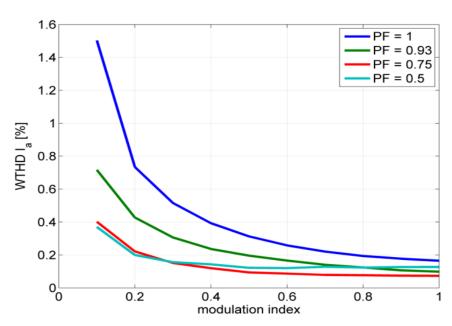

| 2.4.5 Comparison between CBM and SVM                     | 31 |

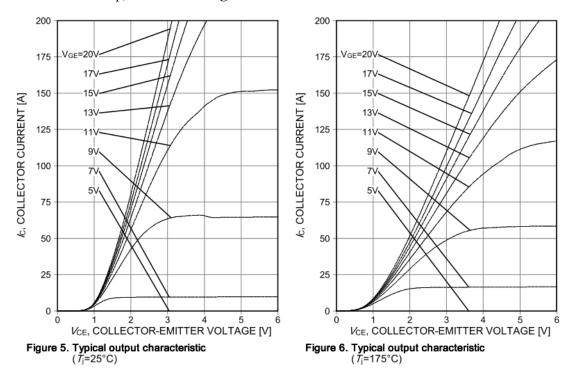

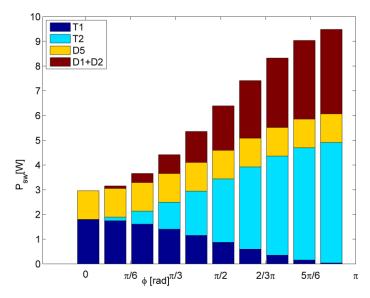

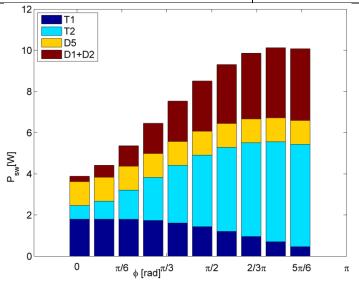

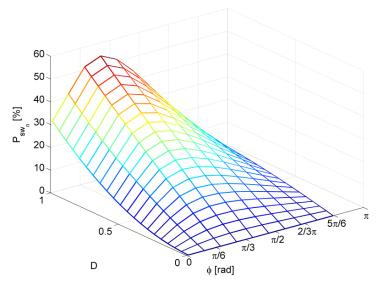

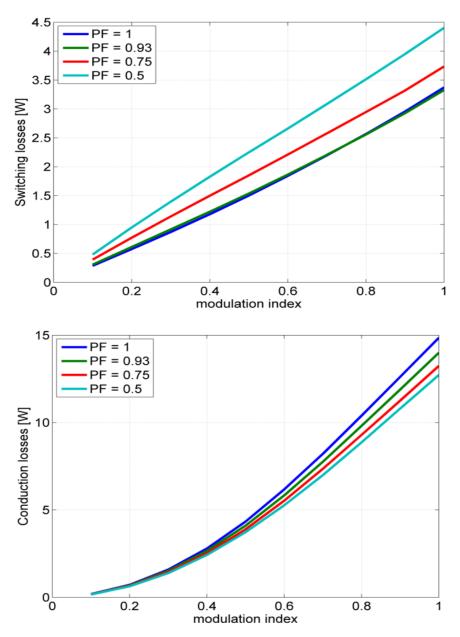

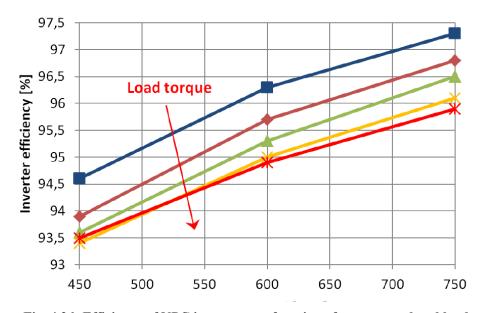

| 2.5 ANALYTICAL APPROACH FOR POWER DEVICE LOSS ESTIMATION | 37 |

| 2.5.1 Conduction Losses                                  |    |

| 2.5.2 Switching Losses                                   |    |

| 2.5.3 Simulations                                        |    |

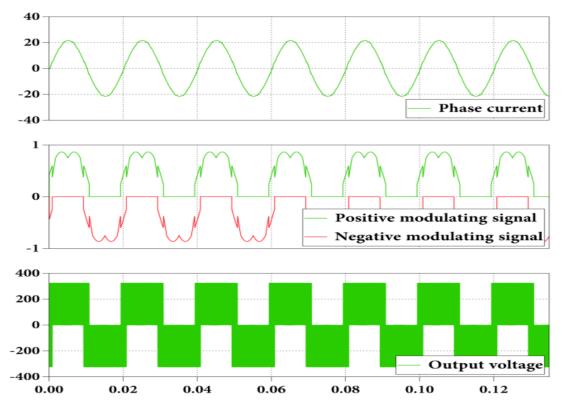

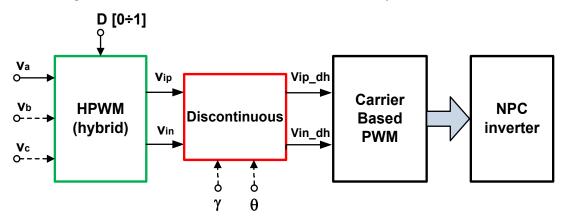

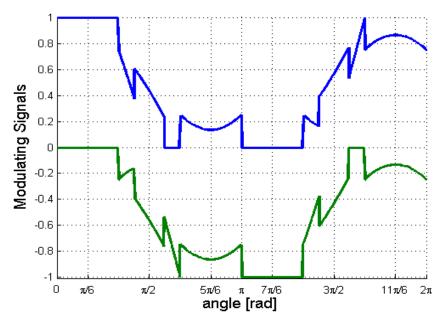

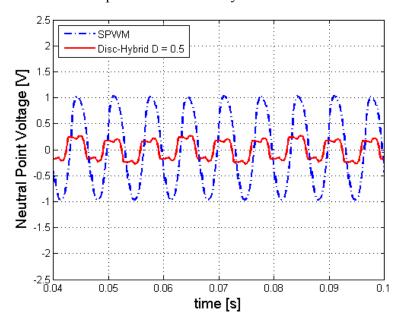

| 2.6 Proposed modulation techniques                       | 49 |

| 2.6.1 Discontinuous-hybrid modulation (DHPWM)            |    |

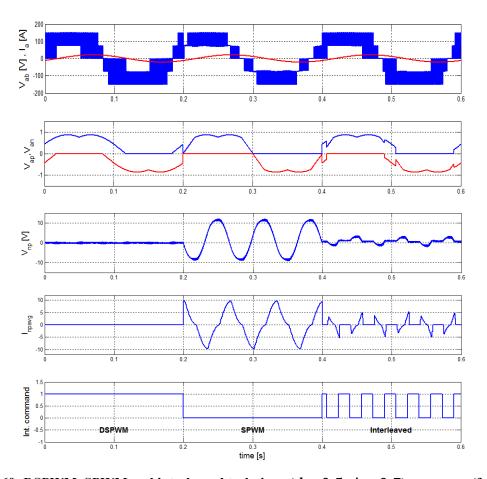

| 2.6.2 Interleaved modulation                             | 65 |

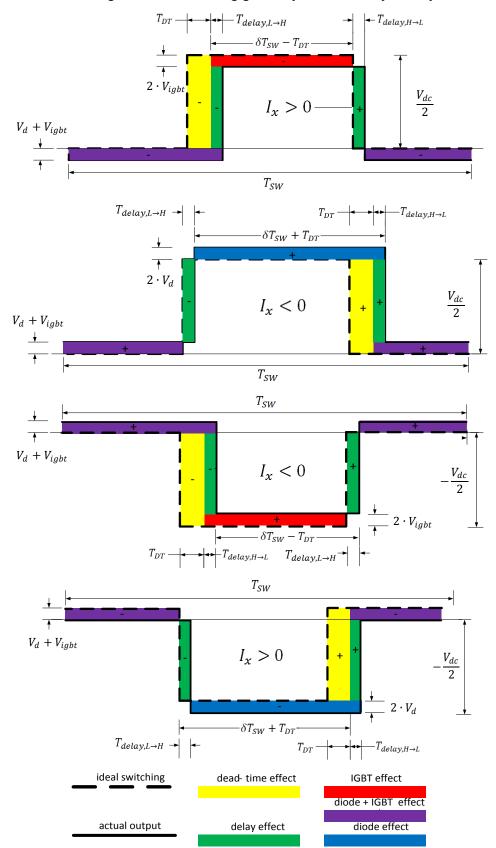

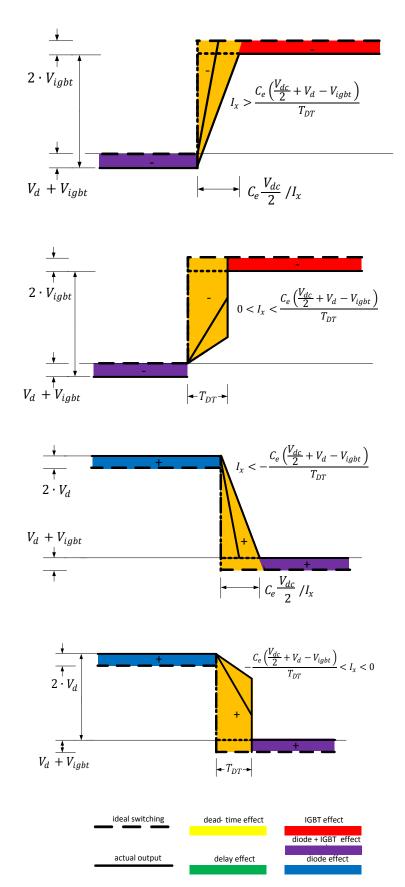

| 2.7 DEAD-TIME ACCURATE MODEL AND COMPENSATION            |    |

| 2.7.1 Introduction                                       |    |

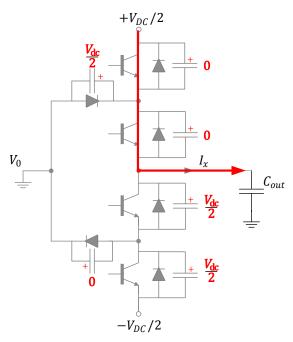

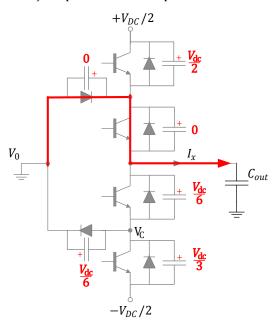

| 2.7.2 Accurate modelling of inverter distortion          |    |

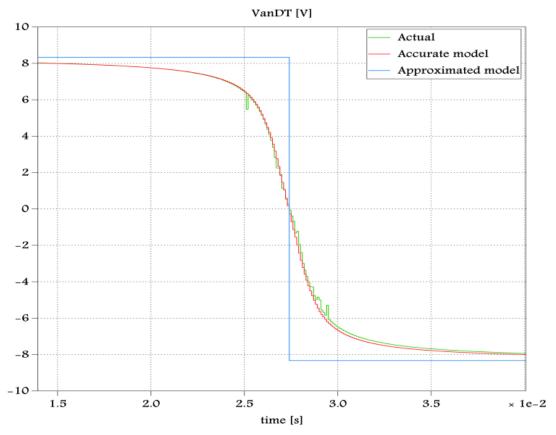

| 2.7.3 Model simplification and simulation results        |    |

| 3 NON-ISOLATED DC/DC CONVERTERS                          |    |

| 3.1 Introduction                                         | 89 |

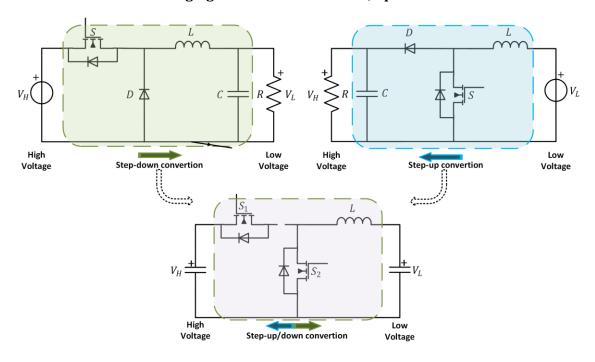

| 3.2 BI-DIRECTIONAL DC/DC CONVERTER                       | 89 |

| 3.2.1 Introduction                                       | 89 |

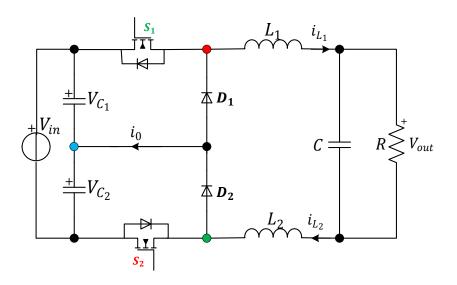

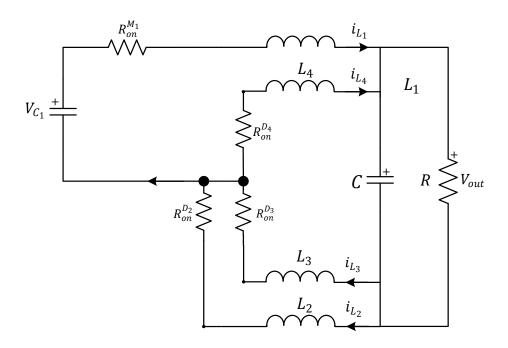

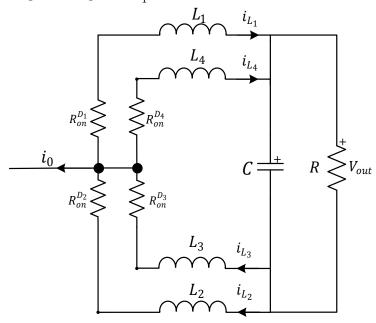

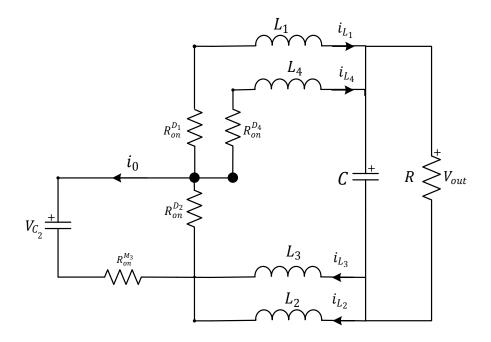

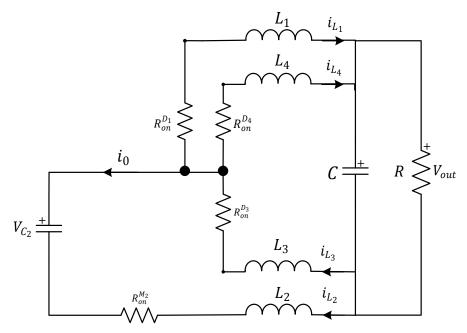

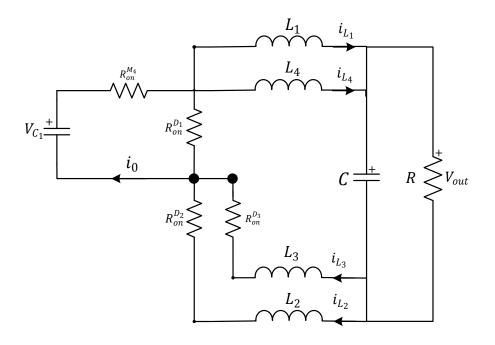

| 3.2.2 Topology                                           |    |

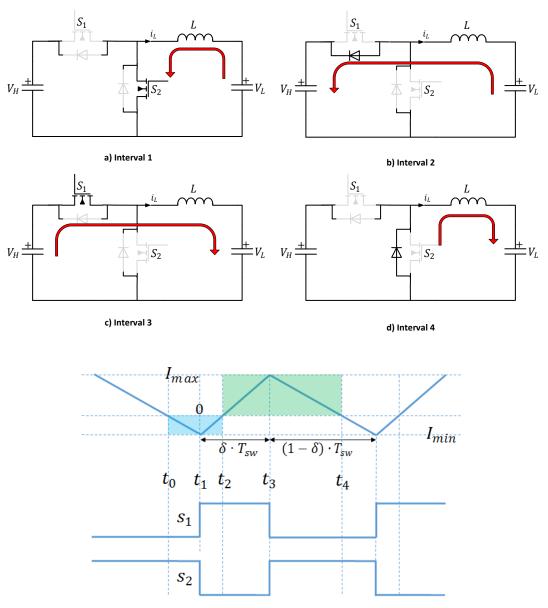

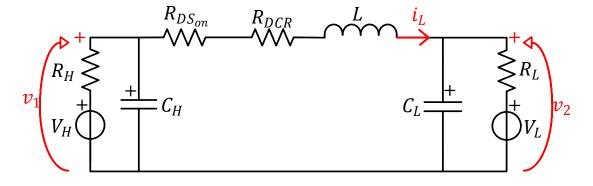

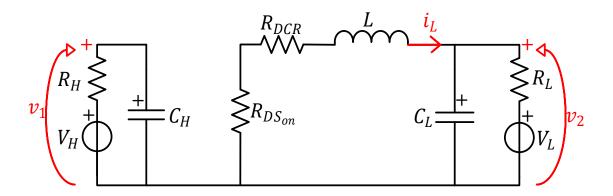

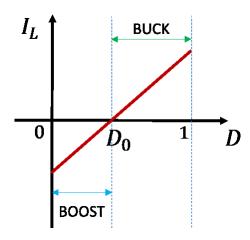

| 3.2.3 Operating modes                                    |    |

| 3.2.4 Unified state-space averaging model                |    |

| 3 3 THREE-I EVEL BLICK CONVERTER                         | 95 |

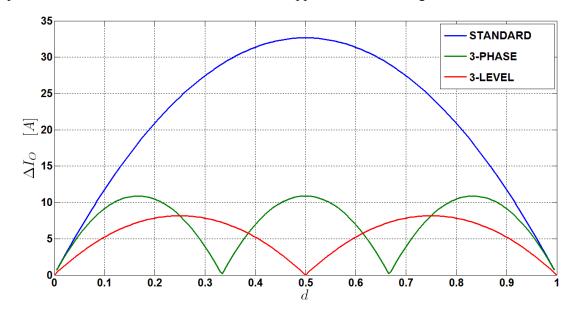

| 3.3.1 Operating principle                                 | 96      |

|-----------------------------------------------------------|---------|

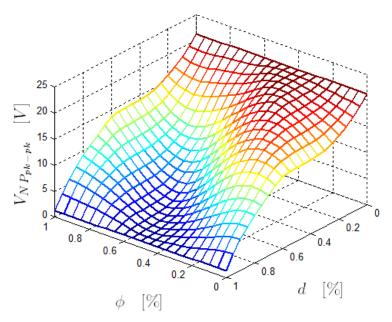

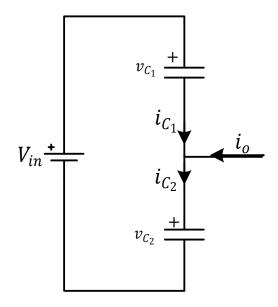

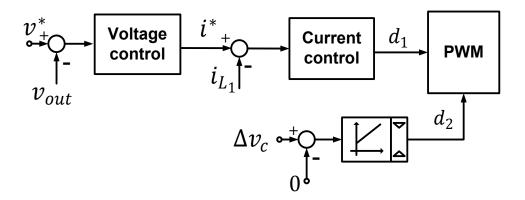

| 3.3.2 Neutral-point voltage regulation                    | 98      |

| 3.4 Interleaved zero current transition 3L buck converter | 103     |

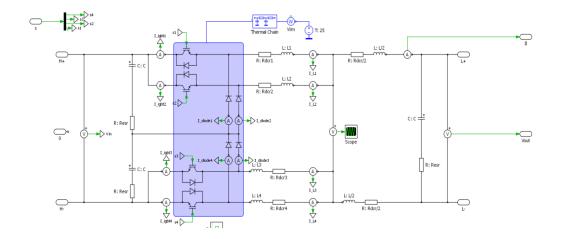

| 3.4.1 Implementation in PLECS                             | 104     |

| 3.5 PROPOSED MULTIPHASE 3L BUCK CONVERTER                 | 106     |

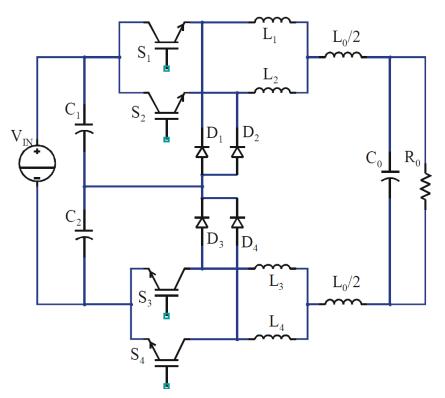

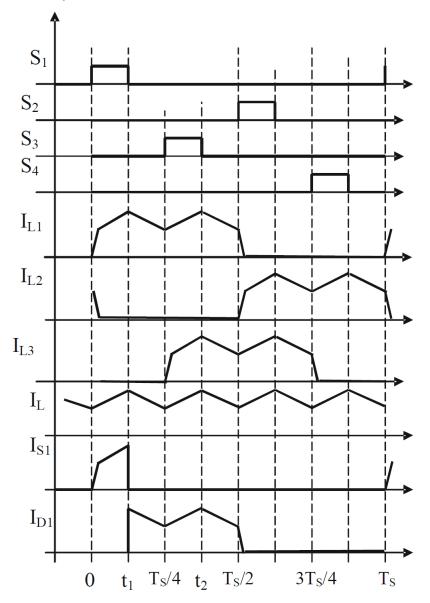

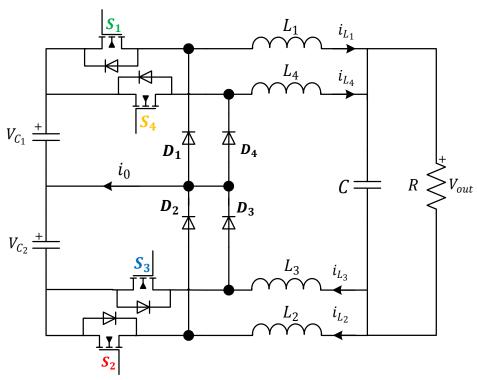

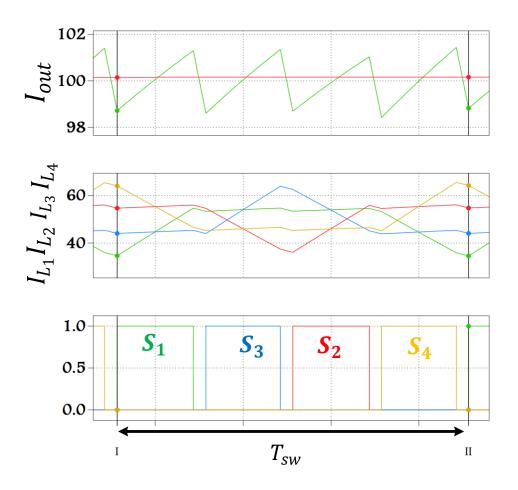

| 3.5.1 Switching modes                                     | 107     |

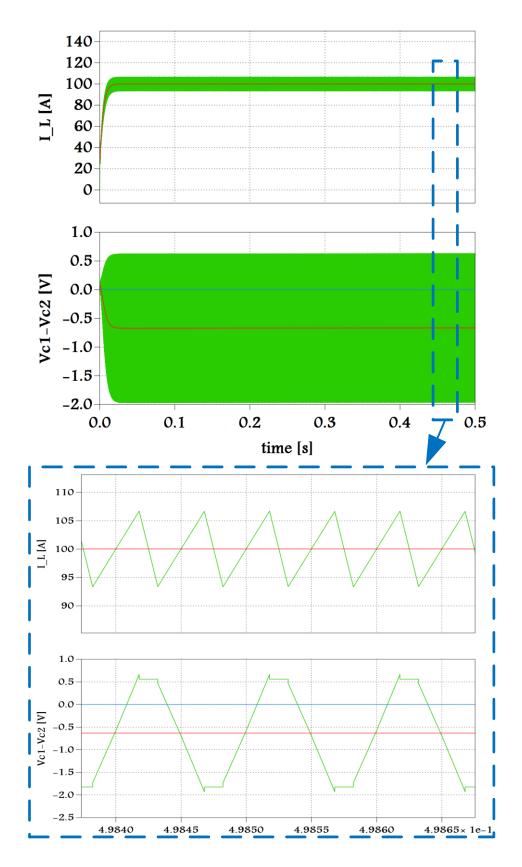

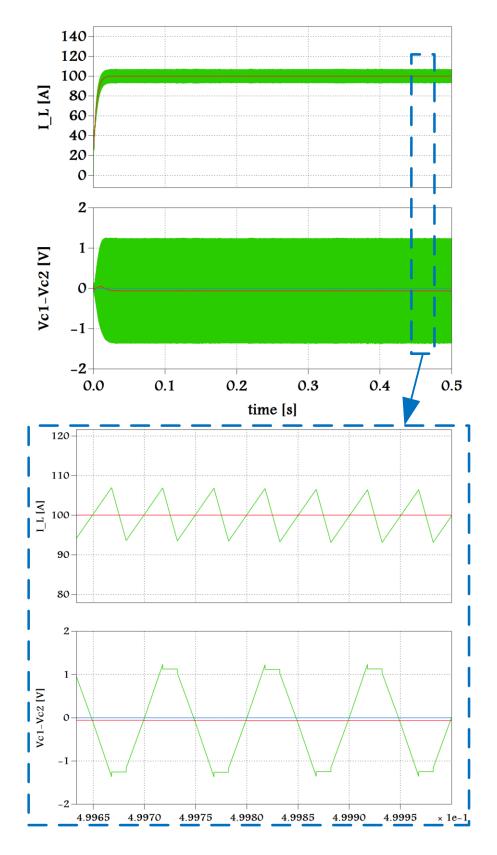

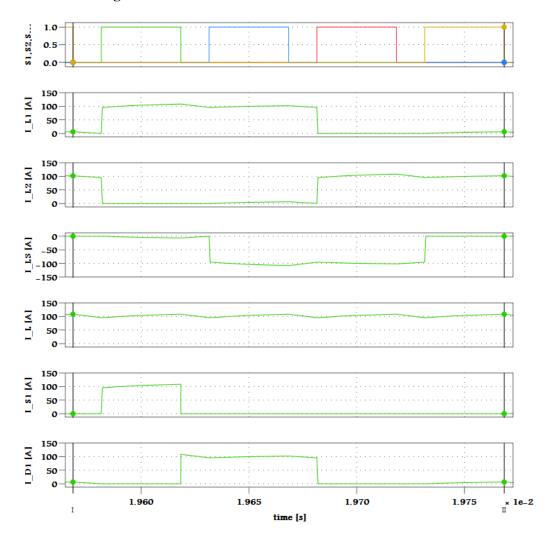

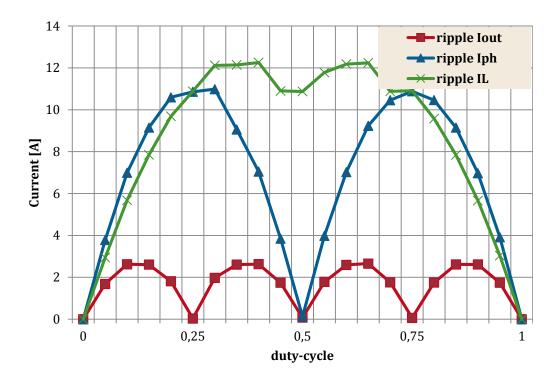

| 3.5.2 Simulation analysis                                 | 111     |

| 4 BI-DIRECTIONAL CONVERTER FOR HYBRID TRACTION            | 116     |

| 4.1 Introduction                                          | 116     |

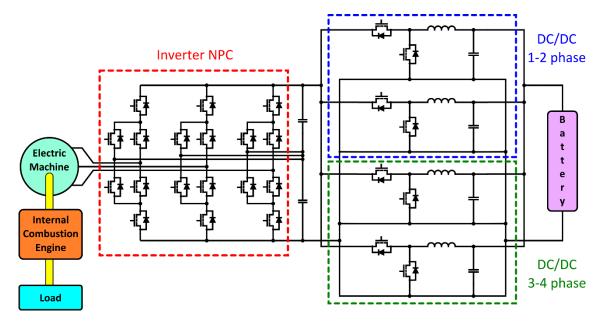

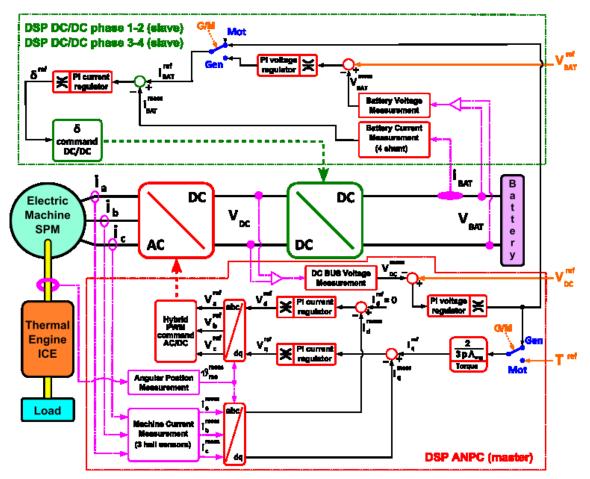

| 4.2 System overview                                       | 118     |

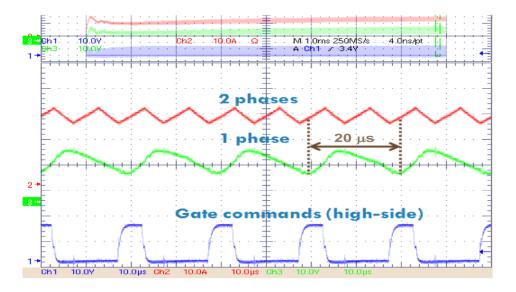

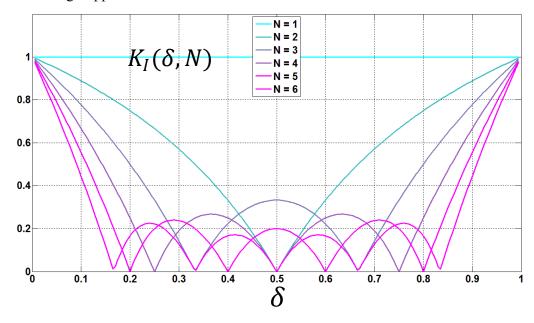

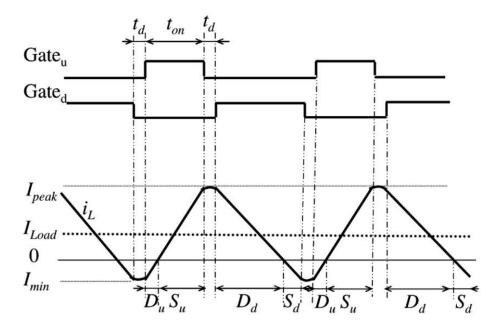

| 4.2.1 Four-phase interleaved half-bridge converter        | 118     |

| 4.2.2 Three-phase active NPC inverter                     | 119     |

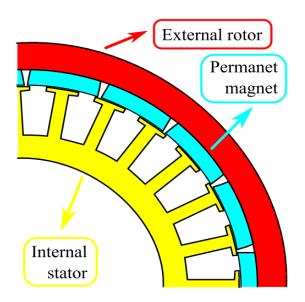

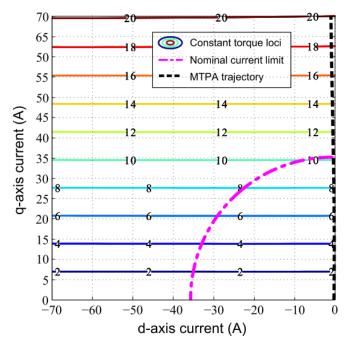

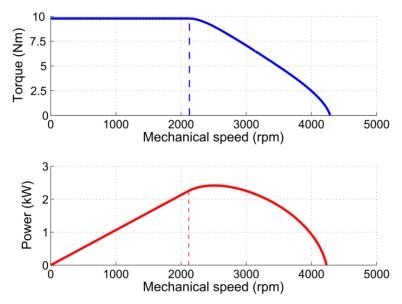

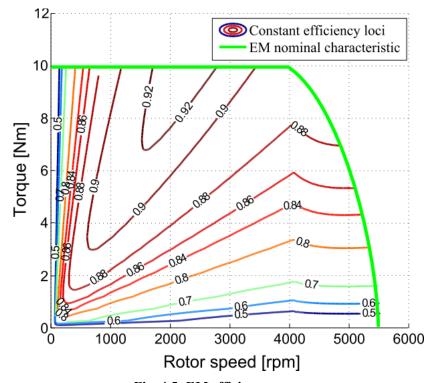

| 4.2.3 Electric machine                                    | 119     |

| 4.2.4 Design choices                                      | 122     |

| 4.3 CONTROL METHOD                                        | 125     |

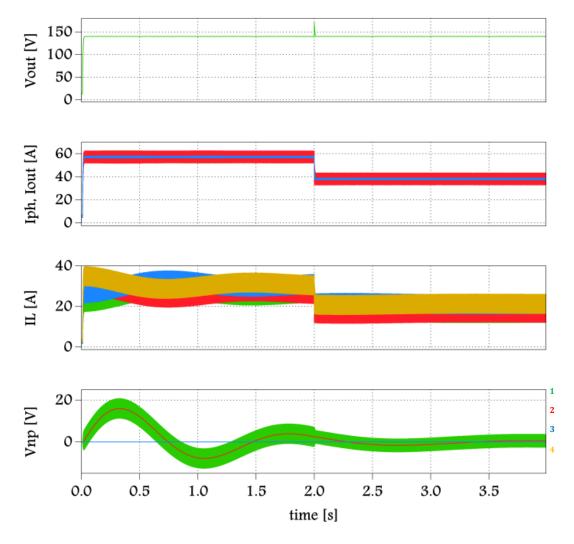

| 4.4 SIMULATION RESULTS                                    | 126     |

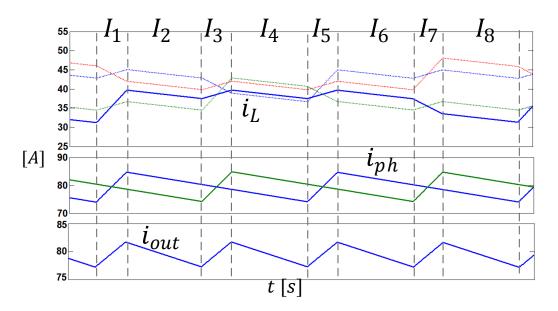

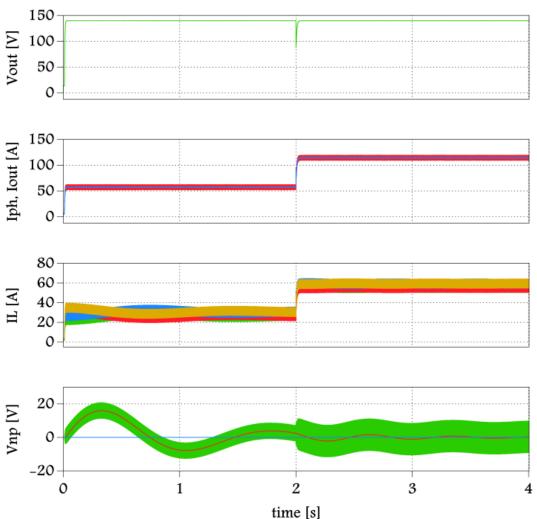

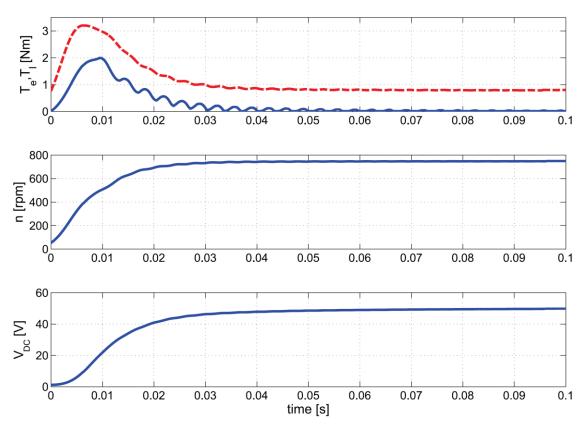

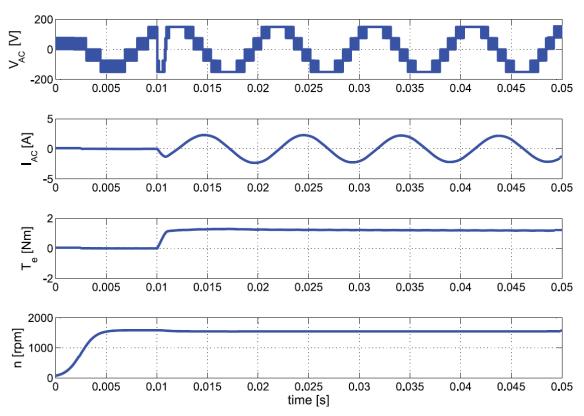

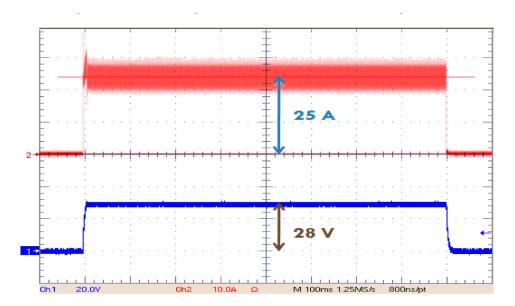

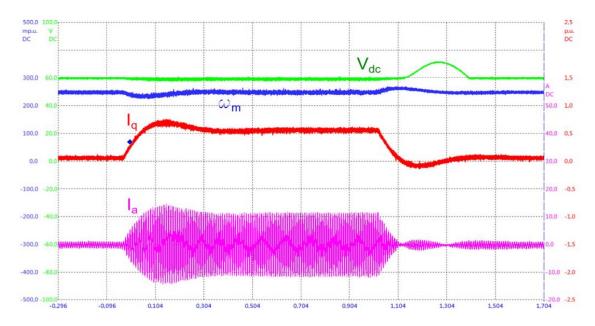

| 4.4.1 Dc-link pre-charge at ICE start-up                  | 126     |

| 4.4.2 Dc-link charge through SPM braking                  | 127     |

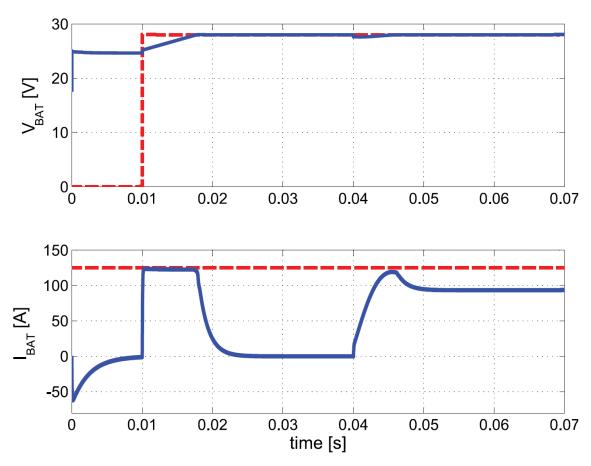

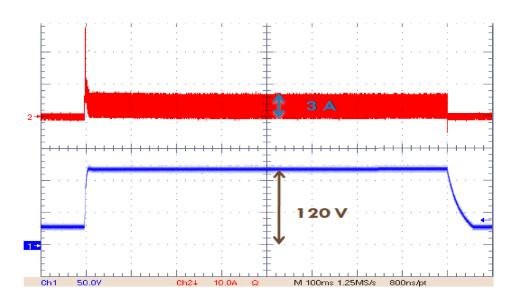

| 4.4.3 Battery Charging (i.e. Control of Battery Voltage)  | 128     |

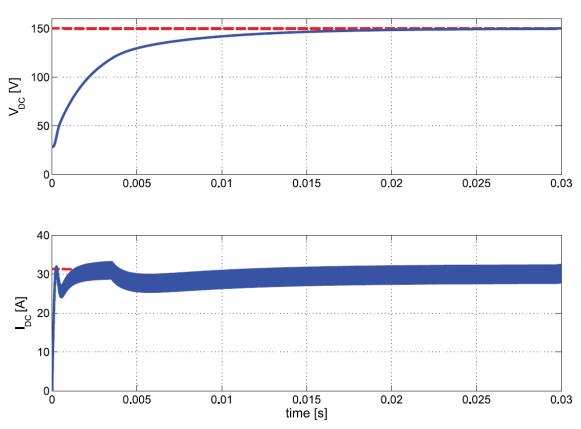

| 4.4.4 Charge of dc Bus from Battery                       | 129     |

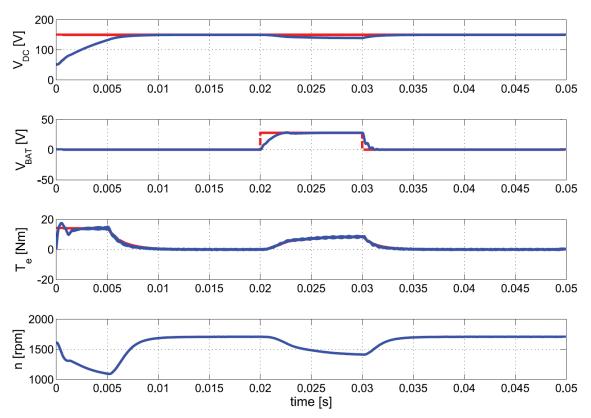

| 4.4.5 Generator Mode of SPM Machine                       | 130     |

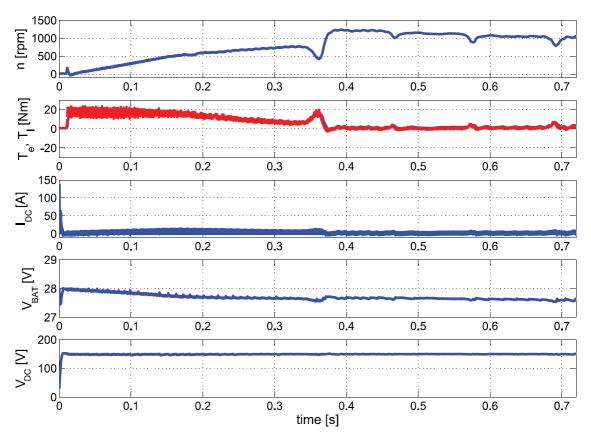

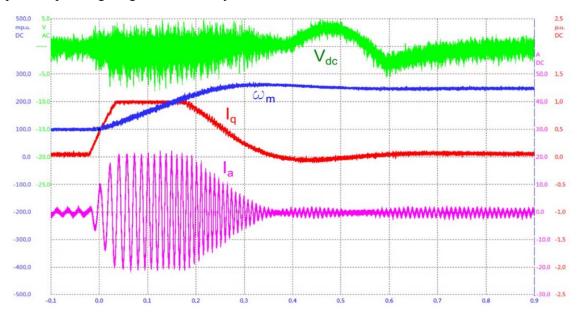

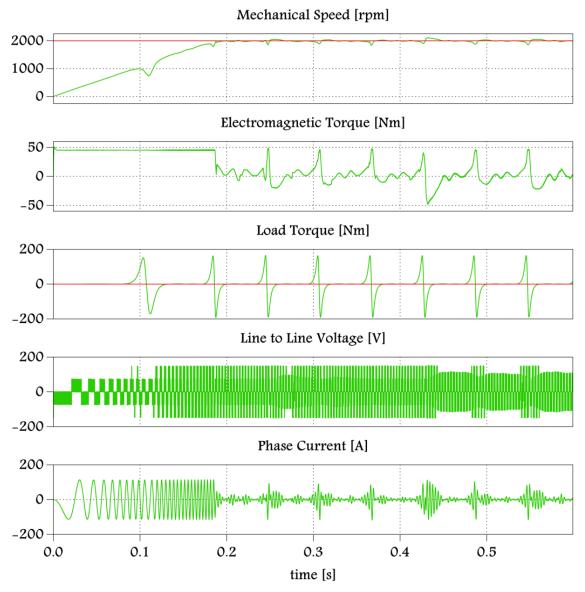

| 4.4.6 Full Start-up of Diesel Engine from Battery Source  |         |

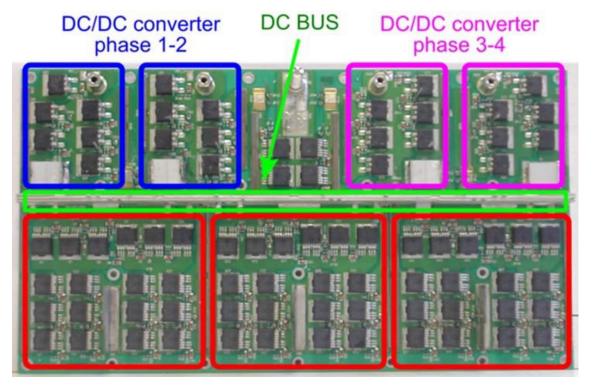

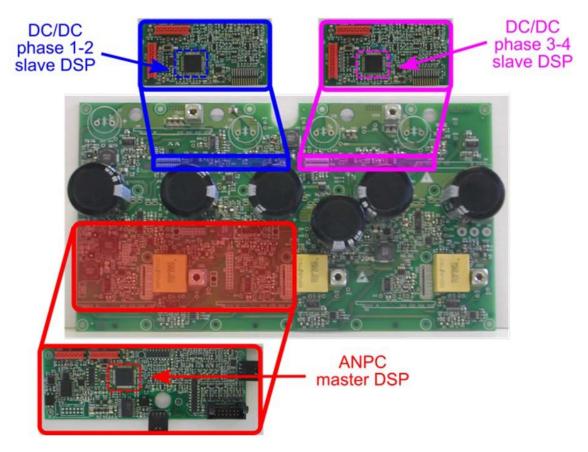

| 4.5 Drive prototype                                       | 132     |

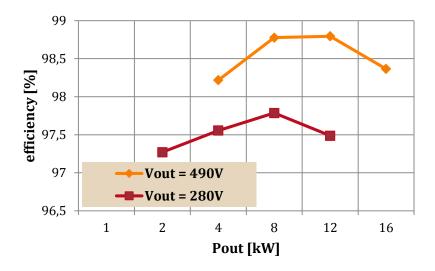

| 4.6 EXPERIMENTAL RESULTS                                  | 134     |

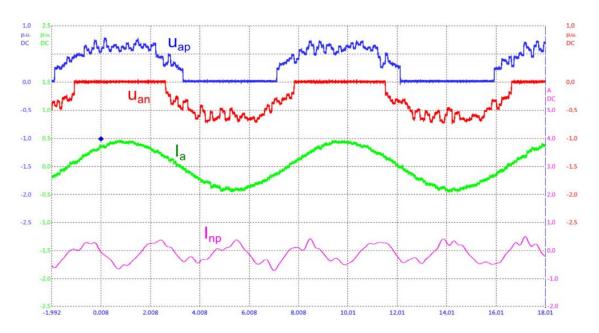

| 4.7 INTERNAL COMBUSTION ENGINE MODEL                      | 140     |

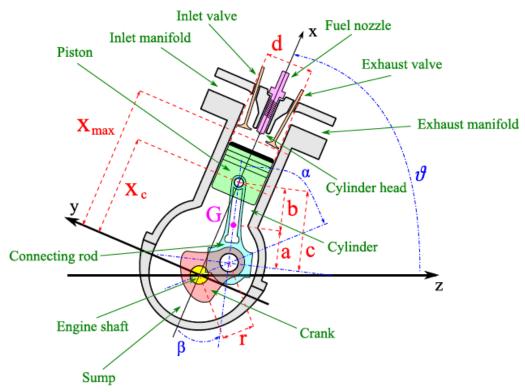

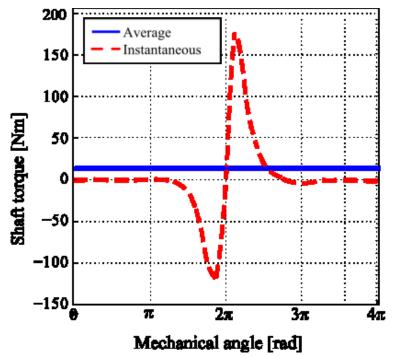

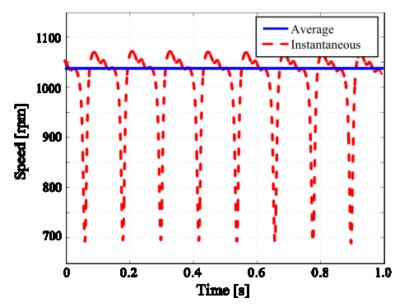

| 4.7.1 Trigonometric analysis                              | 140     |

| 4.7.2 Dynamic analysis                                    | 142     |

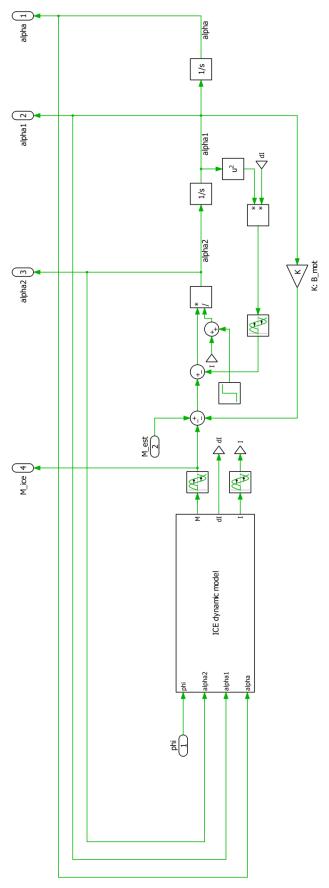

| 4.7.3 Model implementation in simulation                  | 143     |

| 4.8 TORQUE DAMPING TECHNIQUES                             | 147     |

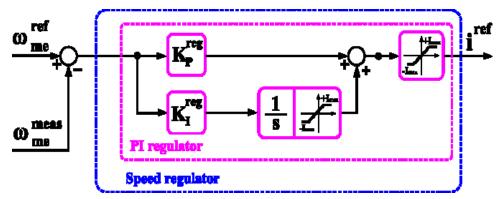

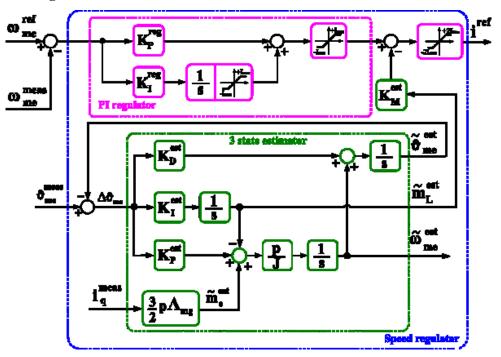

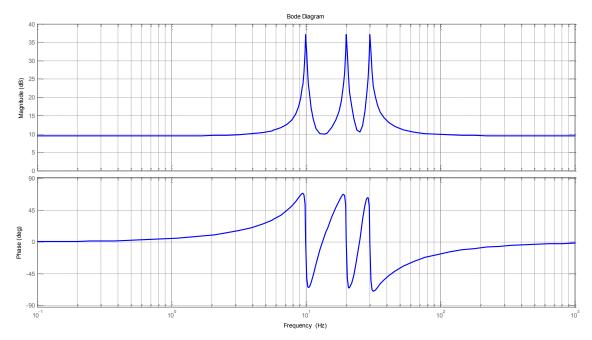

| 4.8.1 Conventional techniques                             | 148     |

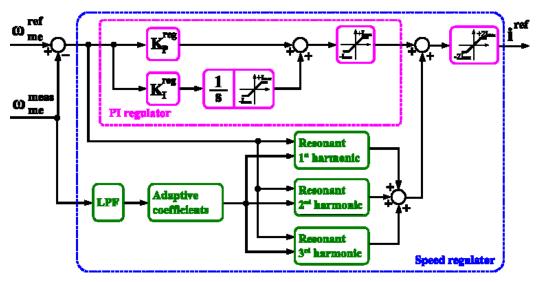

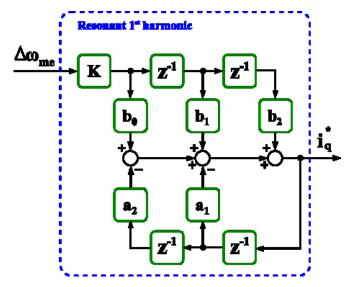

| 4.8.2 Proposed resonant control approach                  |         |

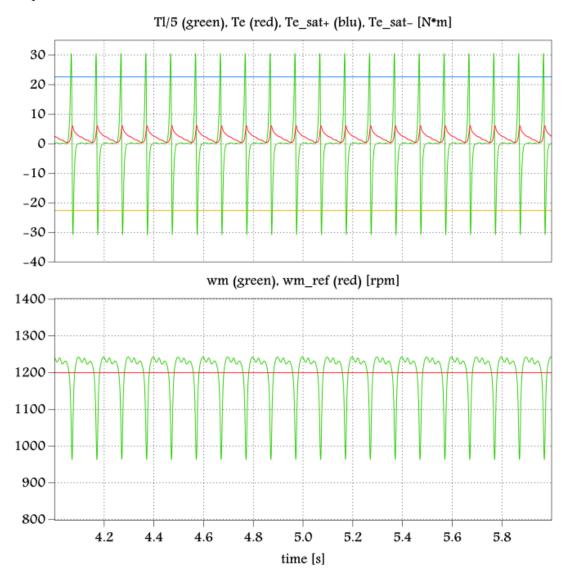

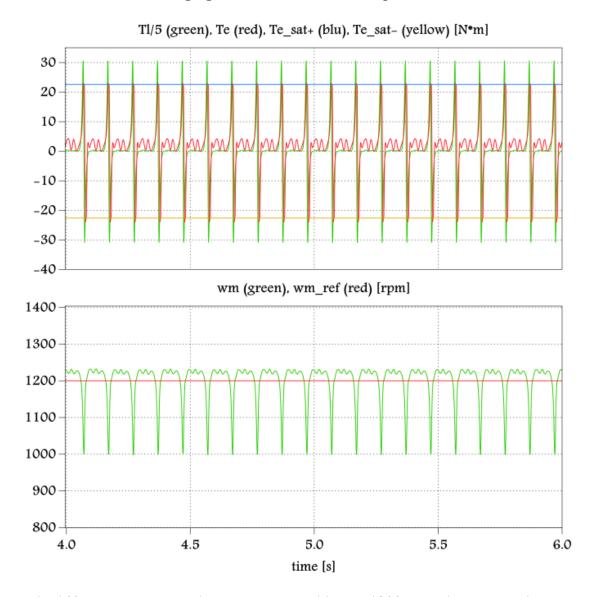

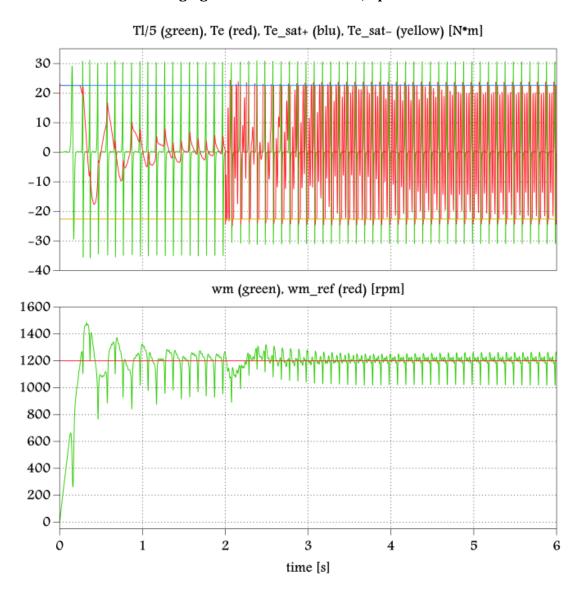

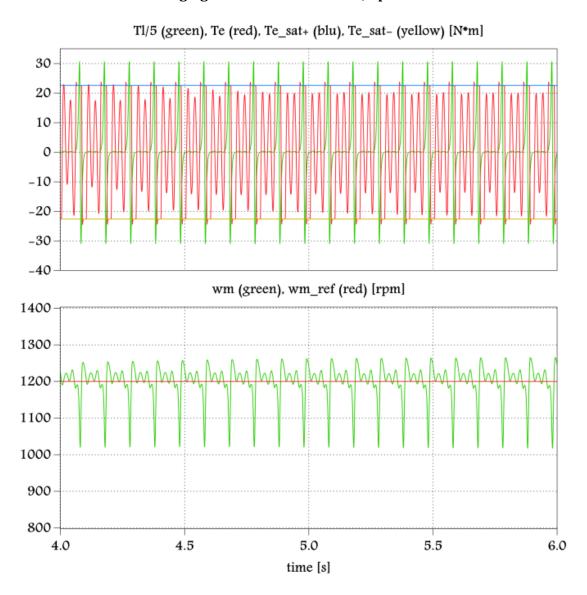

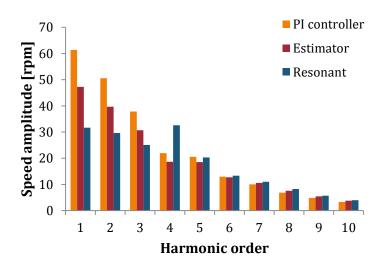

| 4.8.3 Simulation results                                  | 152     |

| 5 DESIGN AND CONTROL OF A WIRELESS CHARGER FOR E          | LECTRIC |

| VEHICLES                                                  | 157     |

| 5.1 Introduction                                          | 157     |

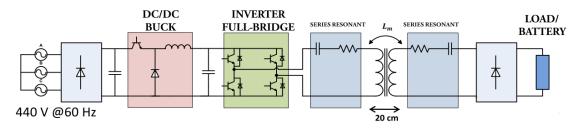

| 5.2 Proposed system design                                | 159     |

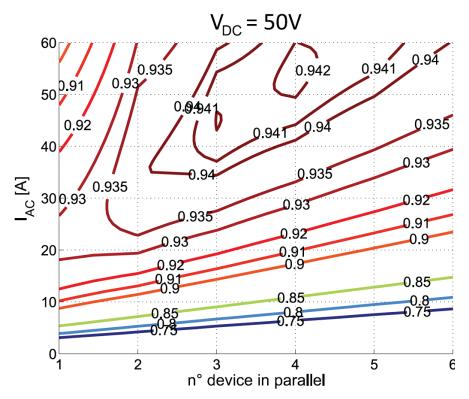

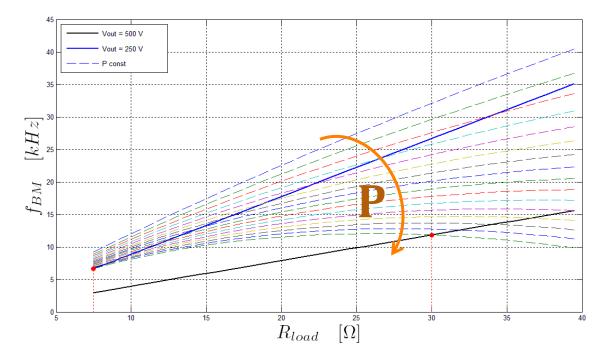

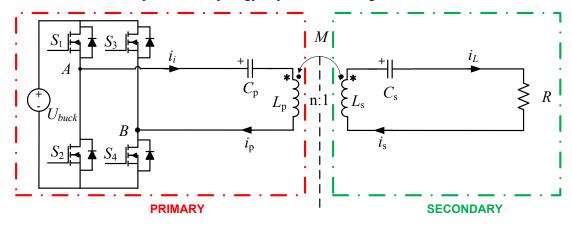

| 5.3 POWER CONTROL METHODS                                 | 159     |

| 5.3.1 Review                                              | 159     |

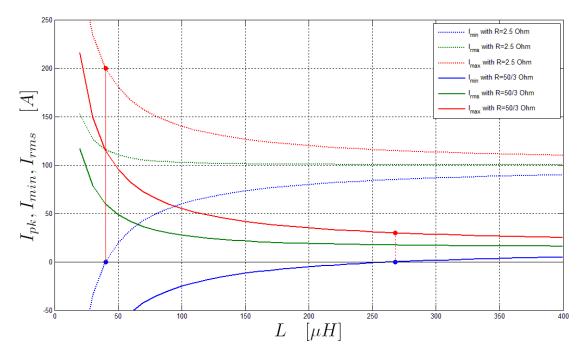

| 5.3.2 Proposed approach                                   | 160     |

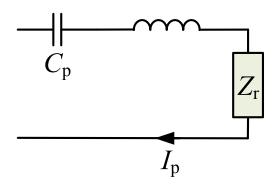

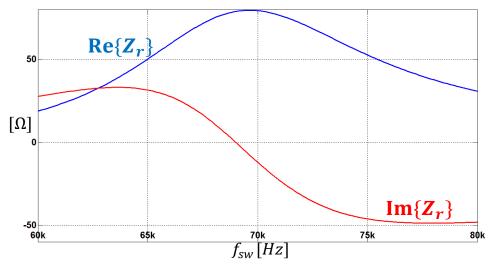

| 5.4 COMPENSATION TOPOLOGY                                 | 167     |

| 5.5 SIMULATION RESULTS                    | 171 |

|-------------------------------------------|-----|

| 5.6 PROTOTYPE AND EXPERIMENTAL TEST BENCH |     |

| 5.6.1 DC/DC converter                     |     |

| 5.6.2 Full-bridge resonant inverter       | 173 |

| 5.6.3 Coil structure parameters           | 173 |

| 5.6.4 Experimental test-bench             | 174 |

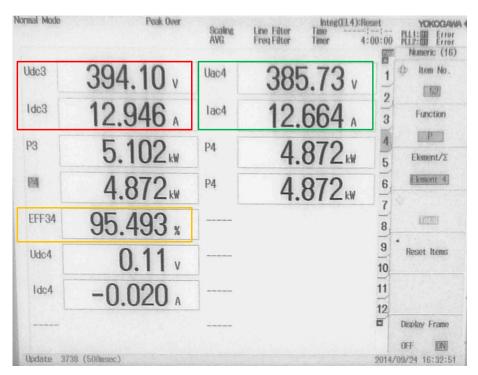

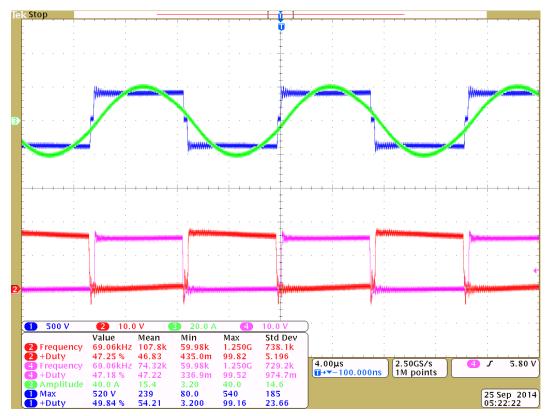

| 5.7 Experimental results                  |     |

| 6 CONCLUSIONS                             | 179 |

| 7 APPENDIX                                | 181 |

| APPENDIX 1                                |     |

| APPENDIX 2                                |     |

| REFERENCES                                | 191 |

# LIST OF TABLES

| TAB. 2.1 CONVERSION SPACE VECTORS SWITCHES                                      | 12  |

|---------------------------------------------------------------------------------|-----|

| Tab. 2.2 Sequences of vector s in the first sextant for 5-segment NTV           | 15  |

| TAB. 2.3 SWITCHING LOSSES COMPARISON                                            | 33  |

| TAB. 2.4 VOLTAGE AND CURRENT WTHD COMPARISON                                    | 34  |

| Tab. 2.5 Integrals for pure SPWM                                                | 39  |

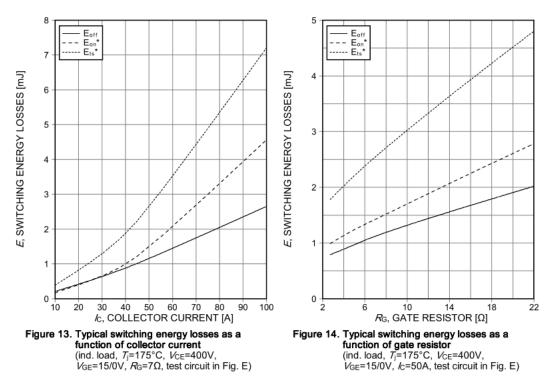

| TAB. 2.6 SWITCHING INTEGRALS FOR PURE SPWM                                      | 43  |

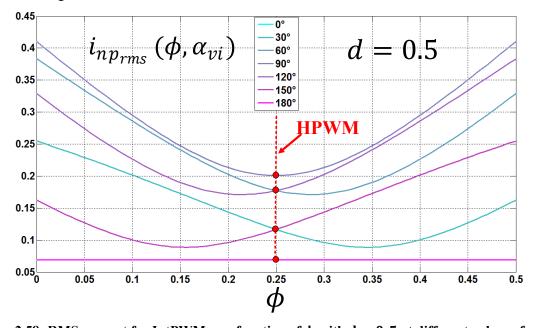

| TAB. 2.7 SWITCHING INTEGRALS FOR PURE HPWM                                      | 44  |

| Tab. 8.1 Integrals for HPWM                                                     | 181 |

| TAB. 8.2 SYSTEM PARAMETERS IN [APEC2013]                                        | 187 |

| Tab. 8.3 Parameters of the NPC inverter, load and SPM motor                     | 187 |

| Tab. 8.4 Parameters of the two-phase three-level Buck Converter.                |     |

| Tab. 8.5 Parameters of the wireless charger.                                    | 188 |

| TAB. 8.6 INTERLEAVED HALF-BRIDGE PARAMETERS FOR EACH PHASE.                     | 188 |

| Tab. 8.7 Active NPC inverter parameters.                                        | 188 |

| Tab. 8.8 Electric machine parameters.                                           | 189 |

| Tab. $8.9$ Switch device parameters at $100^{\circ} \boldsymbol{\mathcal{C}}$ . | 189 |

| TAB. 8.10 ICE MODEL NOTATIONS LIST.                                             | 189 |

# LIST OF FIGURES

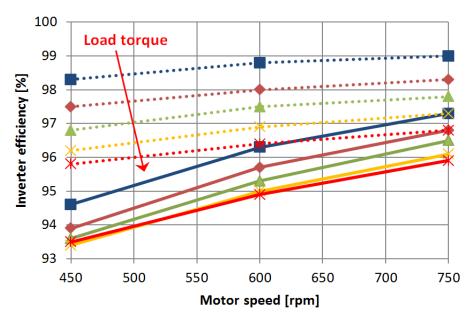

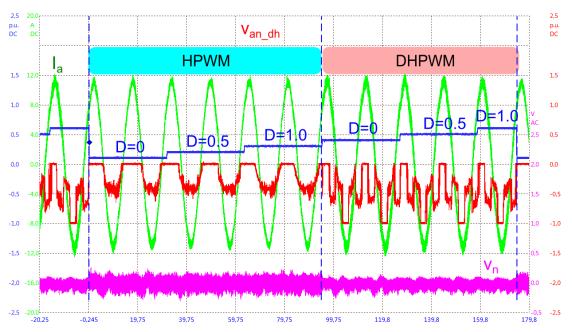

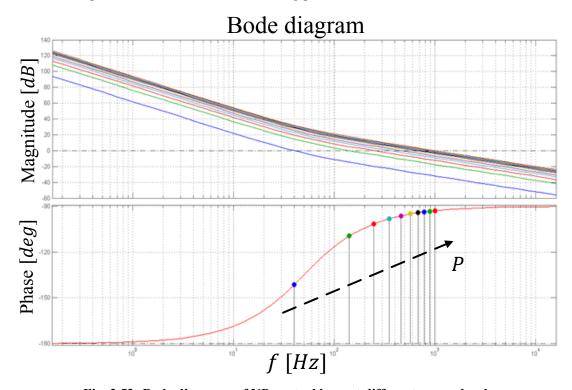

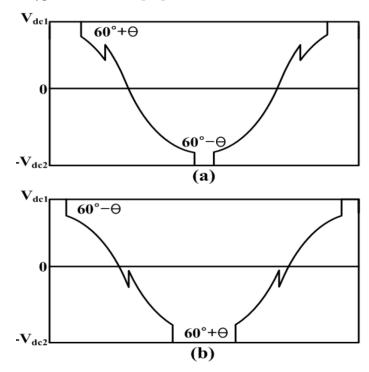

| Fig. 1.1: Last 12-years average retail price chart in Italy (Source: www.economyonline.it)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 1.2: 2012 European countries C02 emissions distribution (Source: Eurostat)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2   |

| FIG. 1.3: TRANSITION FROM ICE TO EV CHART.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3   |

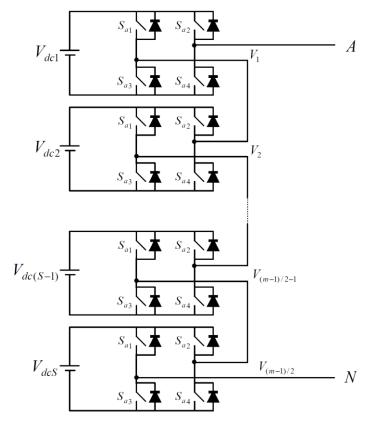

| Fig. 2.1: Single-phase example of a multilevel cascaded inverter with $m{m}$ -levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8   |

| Fig. 2.2: Single-phase example of a flying capacitor inverter with <b>4</b> -levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9   |

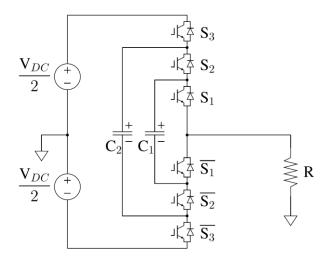

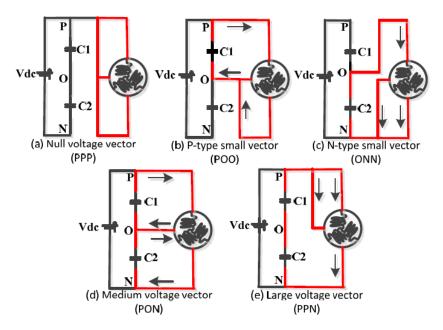

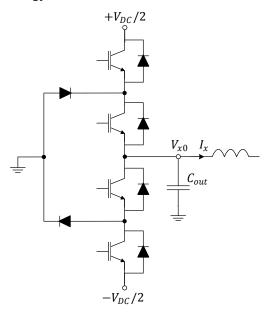

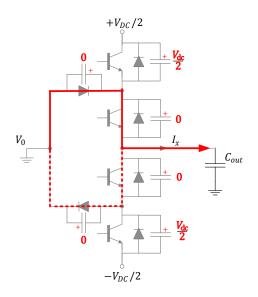

| Fig. 2.3: Three-phase three-level NPC inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11  |

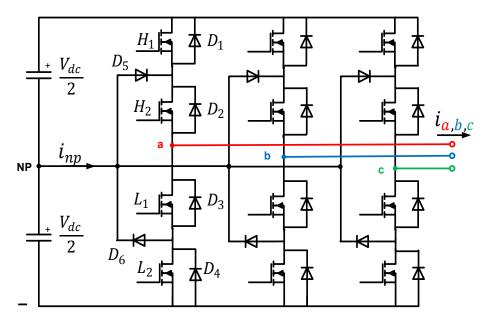

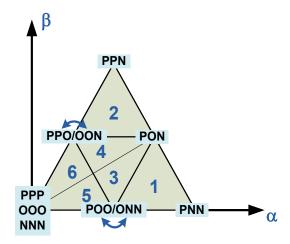

| Fig. 2.4: Space vector diagram for a three-level inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13  |

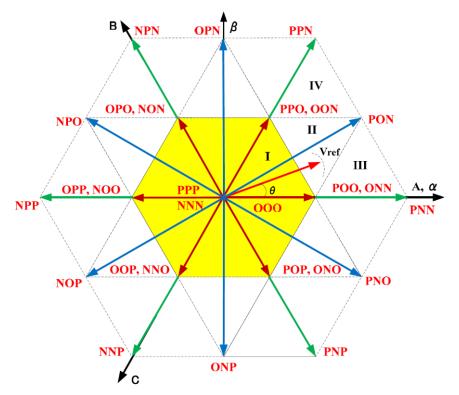

| Fig. 2.5: Effects of the different vector types on the NP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14  |

| Fig. 2.6: Vectors placement for SVM in the first sextant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16  |

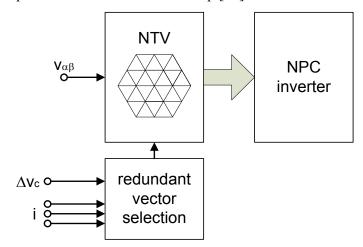

| Fig. 2.7: Redundant selection scheme for the NTV SV-PWM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16  |

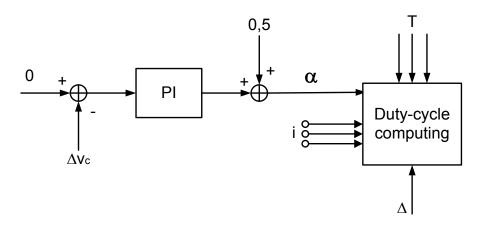

| Fig. 2.8: Calculation of parameter $\alpha$ in symmetric modulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17  |

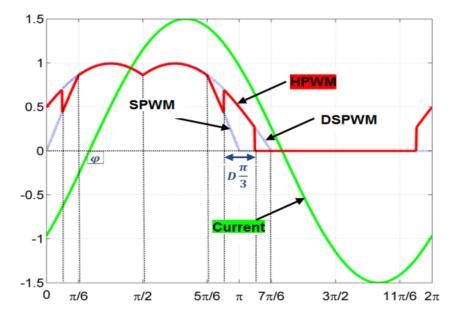

| Fig. 2.9: Modulation signals for SPWM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19  |

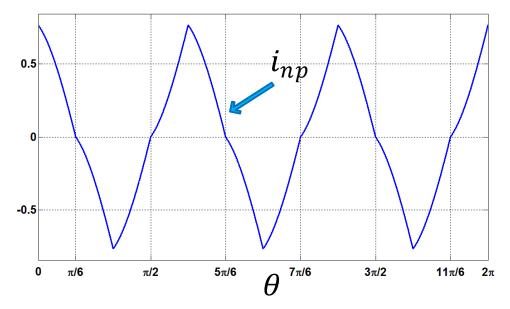

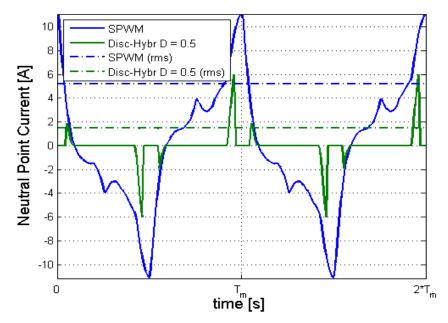

| Fig. 2.10: NP current average value within a fundamental period for SPWM with $\alpha vi=50^{\circ}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 21  |

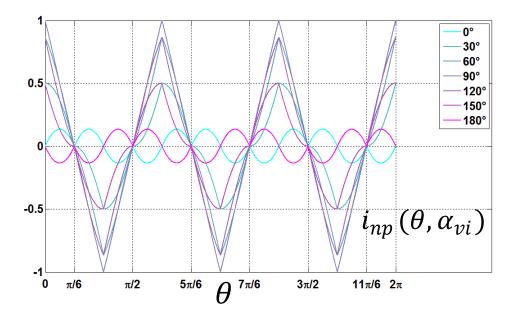

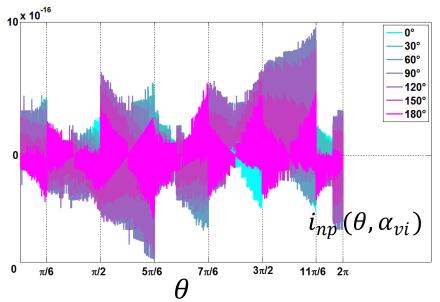

| Fig. $2.11\ NP$ average current waveform within a fundamental period for SPWM at different values of the second s | UES |

| 0F <b>αvi</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22  |

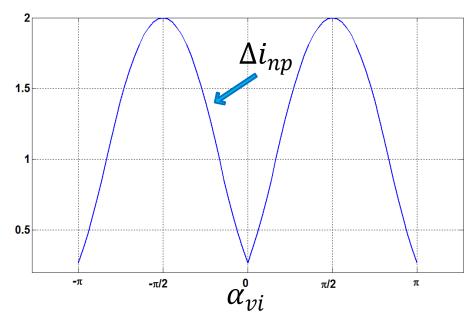

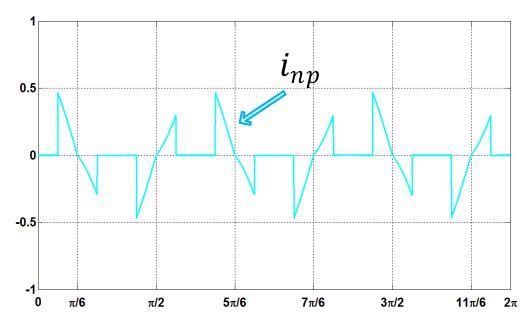

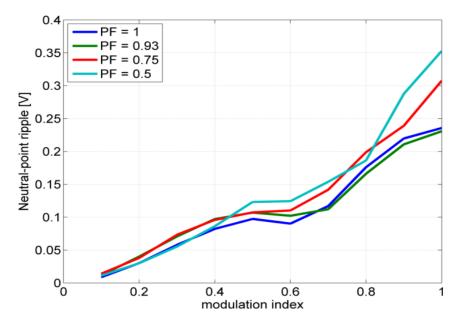

| Fig. 2.12: NP current ripple for SPWM as a function of load phase angle $\alpha vi$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22  |

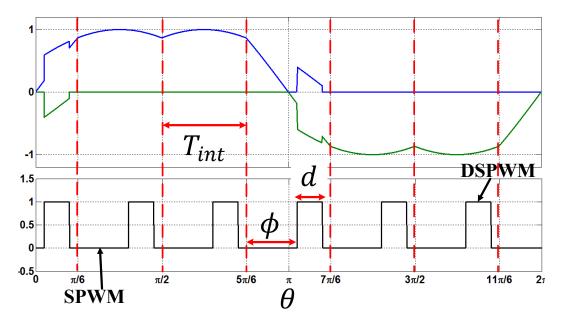

| Fig. 2.13: Modulation signals for DSPWM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24  |

| Fig. 2.14: NP average current waveform within a fundamental period for DSPWM at different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| VALUES OF ανi.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25  |

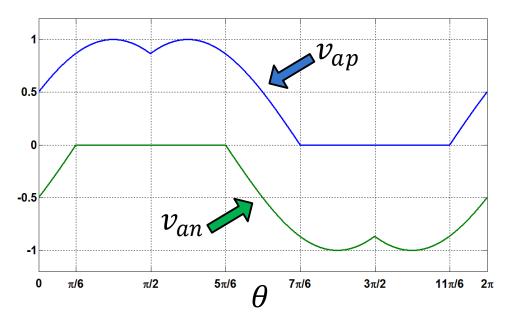

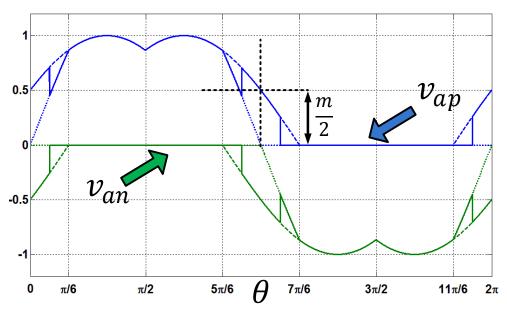

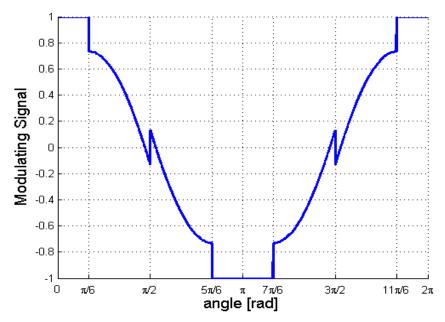

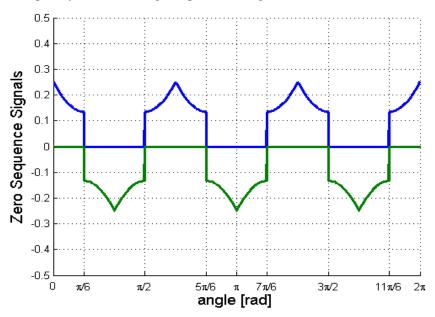

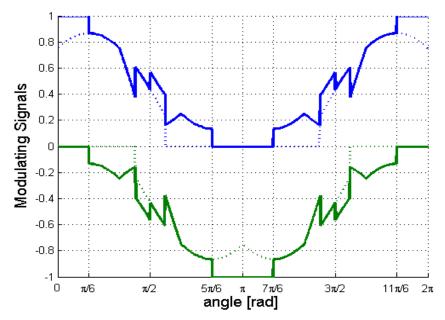

| Fig. 2.15: Modulation signals for HPWM with $\mathbf{D}=0,5.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26  |

| Fig. 2.16: NP current average value within a fundamental period for HPWM with $\mathbf{D}=0$ , $5$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| $AND.\alpha vi = 50^{\circ}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27  |

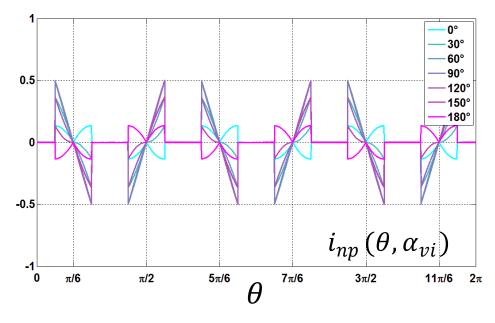

| Fig. 2.17: NP average current waveform within a fundamental period for HPWM with $\mathbf{D}=0,5$ as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ΥT  |

| DIFFERENT VALUES OF $lpha vi$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27  |

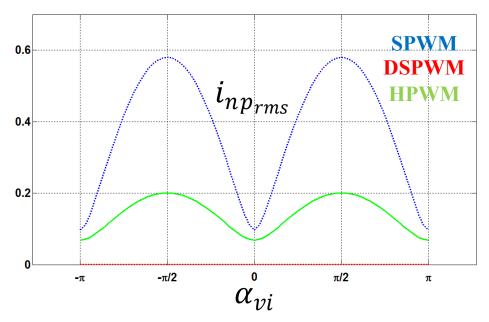

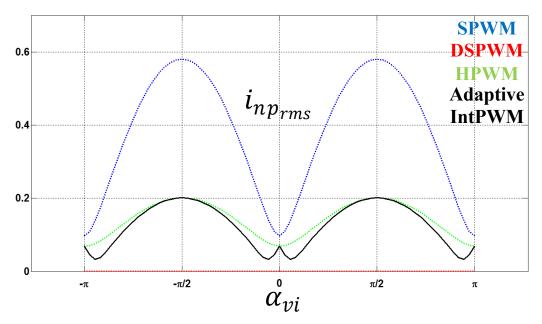

| Fig. 2.18: NP current RMS value as a function of load phase angle $\alpha vi$ for SPWM, DSPWM and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| HPWM with $\mathbf{D}=0,5.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28  |

| Fig. 2.19: Self-balancing effect in SPWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29  |

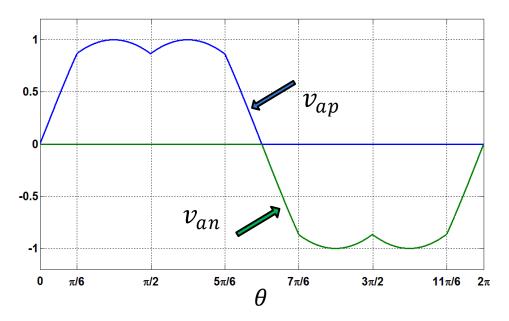

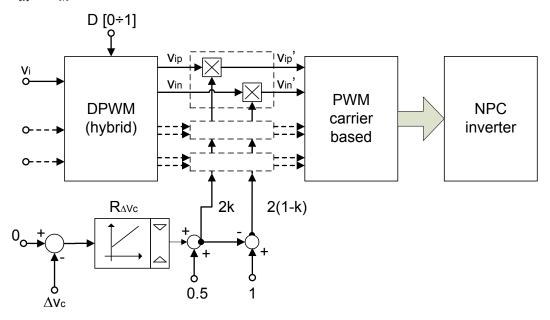

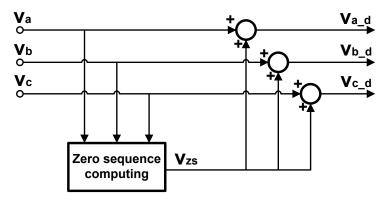

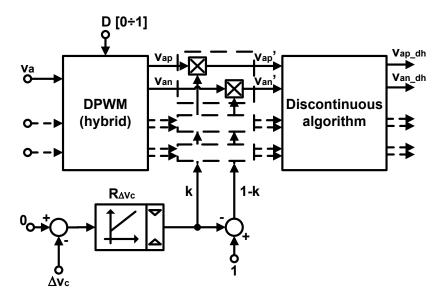

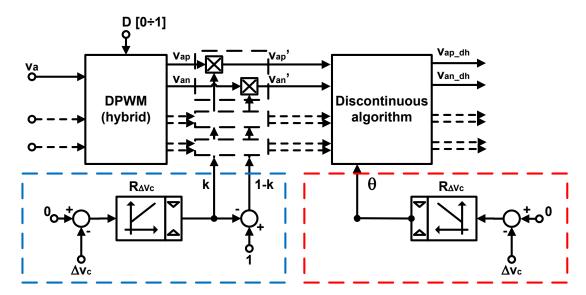

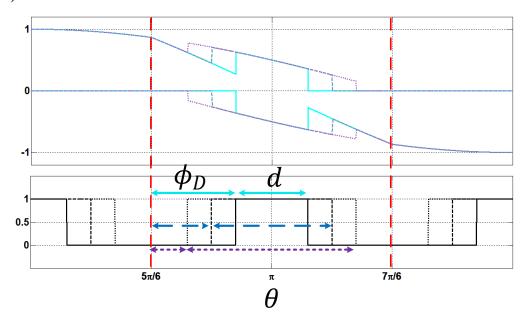

| Fig. 2.20: Neutral-point control scheme for the HPWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30  |

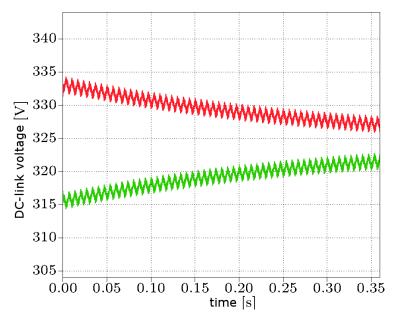

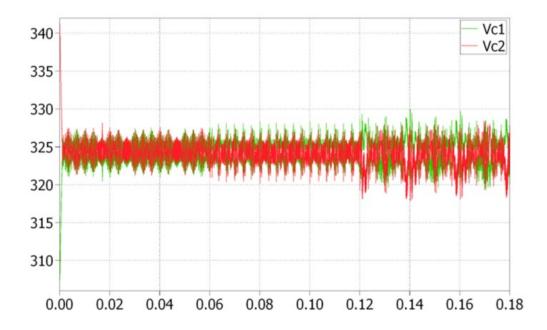

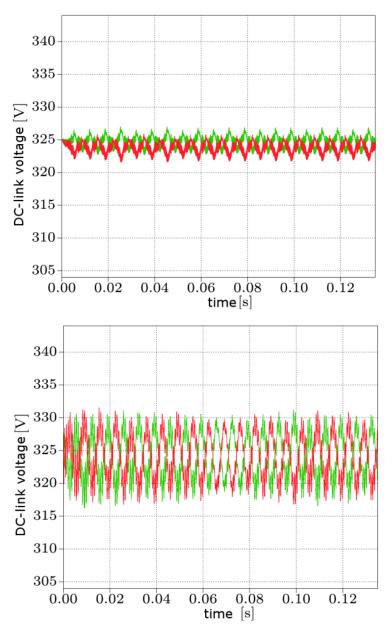

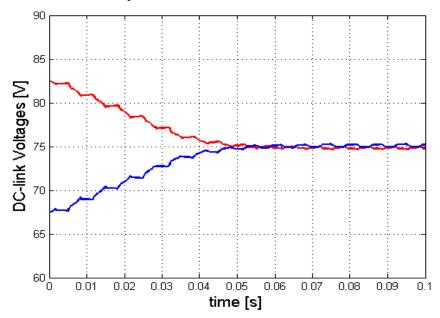

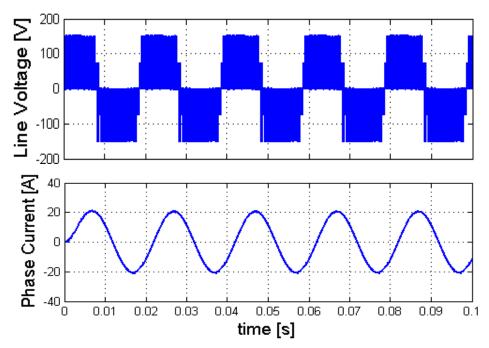

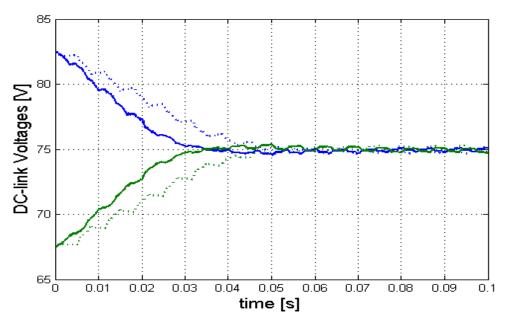

| Fig. 2.21: Bus capacitor voltages for the H-PWM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 32  |

| Fig. 2.22: Bus capacitor voltages for the NTV SV-PWM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32  |

| Fig. 2.23: Five-segment NTV SVM N-P ripple without (upper) and with (lower) LCL filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35  |

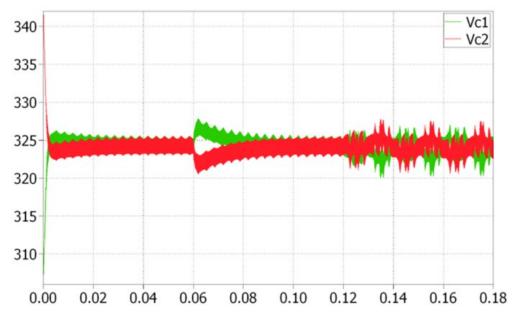

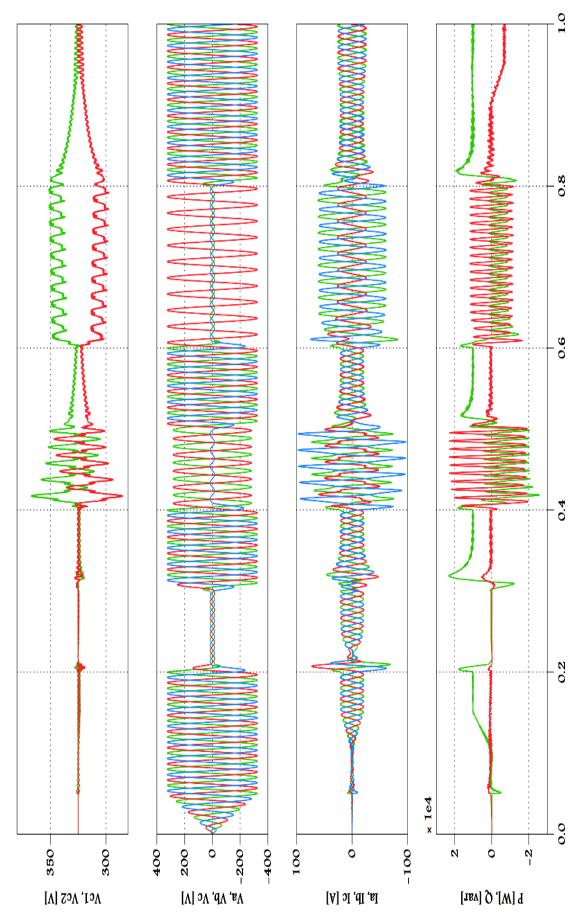

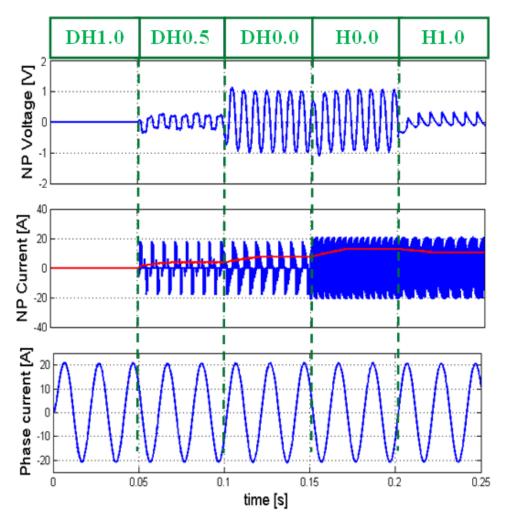

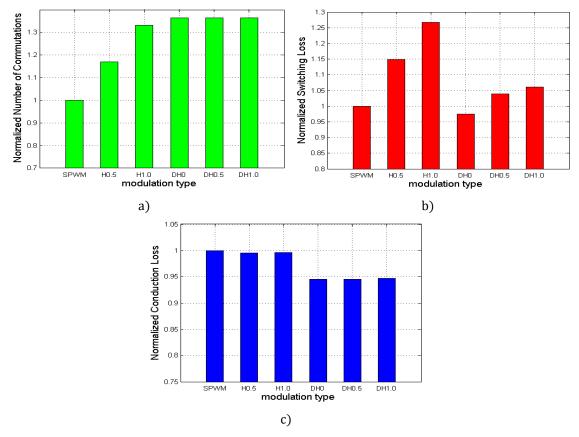

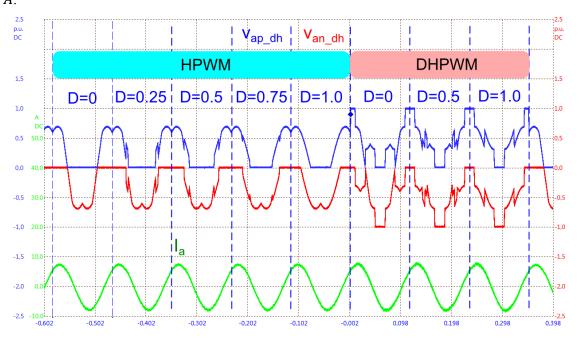

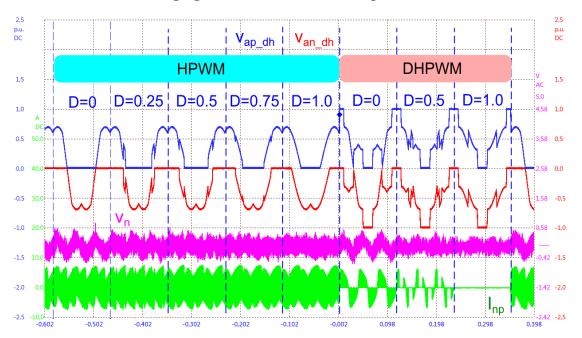

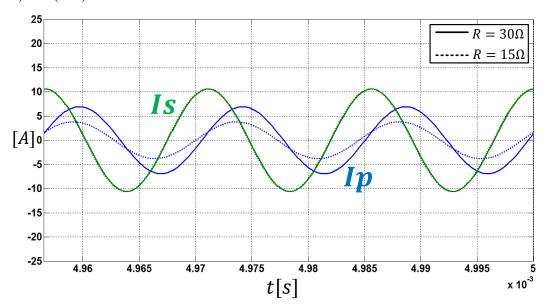

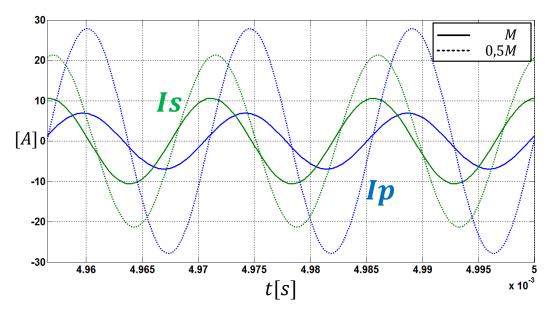

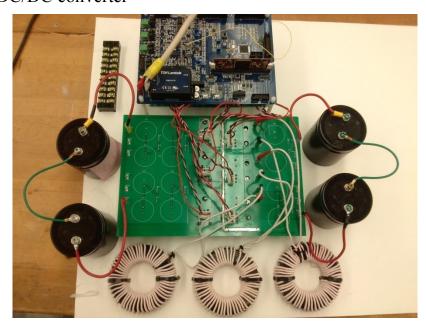

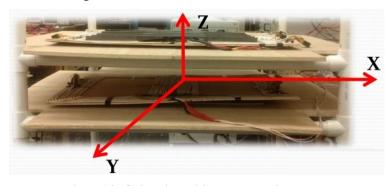

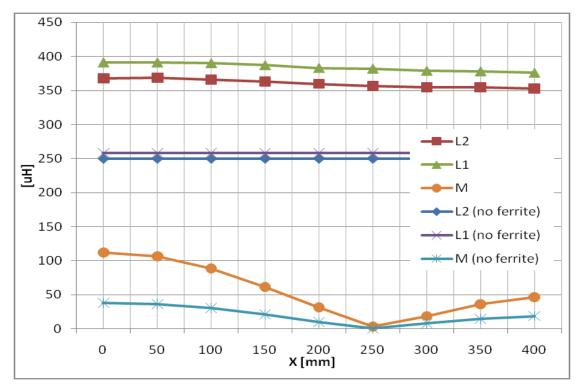

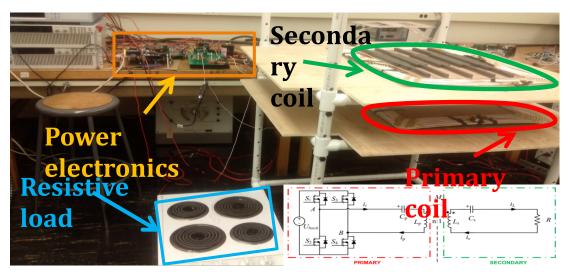

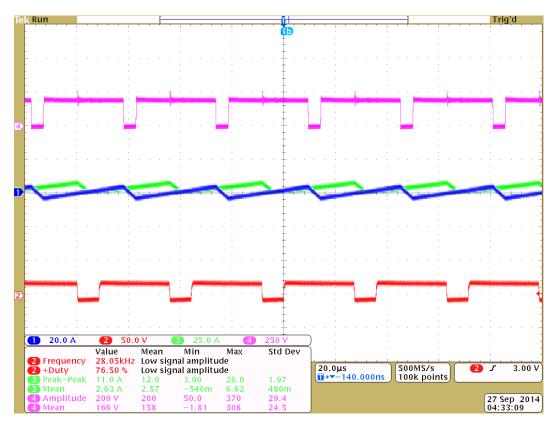

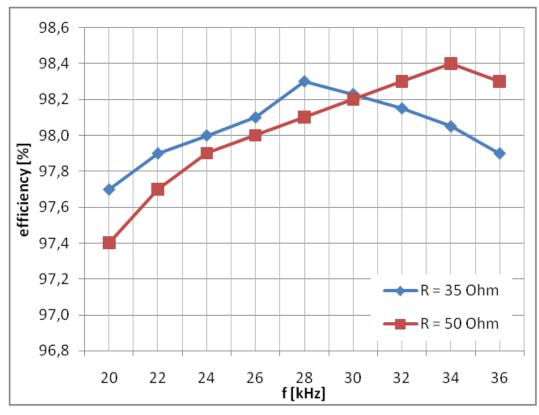

| FIG. 2.24: HPWM TECHNIQUE WITH "DYNAMIC" BALANCER UNDER GRID-FAULTS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36  |