Dipartimento Politecnico di Ingegneria e Architettura Corso di Dottorato in Ingegneria dell'Informazione

PhD Thesis

# Modellizzazione, Progetto e Caratterizzazione di un Link Seriale a 10Gbps

# Modeling, Design and Characterization of a 10Gbps Serial Link

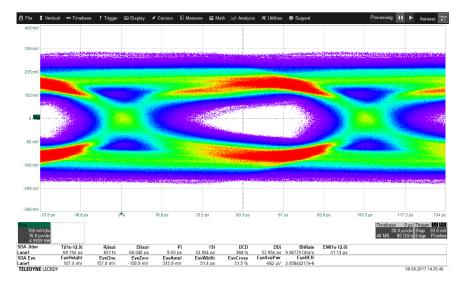

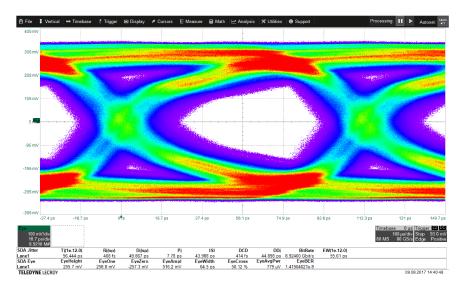

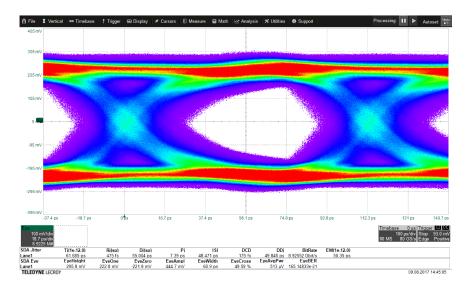

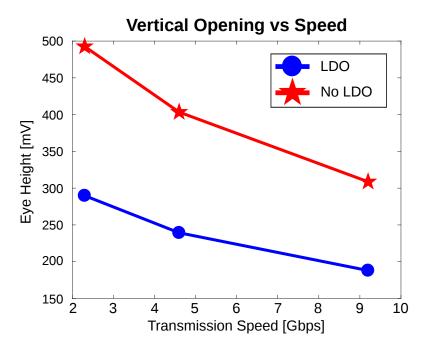

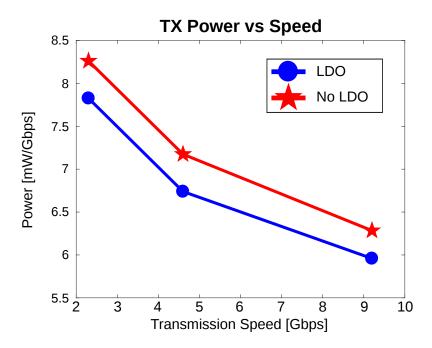

Supervisor: Prof. Ing. Pierpaolo Palestri PhD Candidate: Andrea Bandiziol

Anno Accademico 2016 – 2017

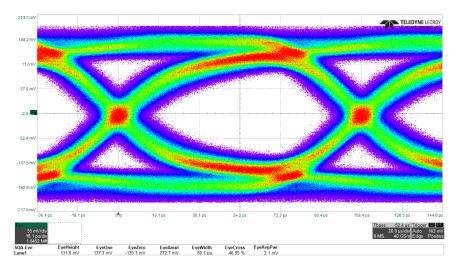

# Abstract

The goal of this PhD has been to model, design and characterize a 10Gbps serial interface suitable for automotive Electronic Control Units (ECU). The work has been carried out in collaboration with Infineon Technology.

High speed serial interfaces are a hot topic both in the academic and industrial world. Due to the stringent safety requirements and the extremely harsh environment in which the link must be able to correctly operate, the automotive sector lags some years behind the consumer market. Thus, the main goal of this work is to bridge the gap between the consumer electronic and the automotive electronic unit world, understanding which techniques are suitable for our working conditions among the ones that are already well established in the academic world and translating and improving these solutions to possibly make them more stable and less power consuming. This goal implies a deep understanding of a serial link both at system and transistor level, and the development of this thesis will follow this idea.

The first part of this work is dedicated to the transmitter: we will start from a system level analysis, creating a methodology to assess the equalization capability that has to be foreseen at transmitter side when dealing when channels typical of the automotive environment. The description of the transistor level design will follow, motivating design choices and supporting them with simulation results and comparison with the state of the art presented in literature. To conclude this first part of the work, measurements of the described transmitter will be presented and discussed.

The second part of the thesis is mainly focused on the receiver. As for the transmitter, we will start with a system level analysis, aimed at understanding the different equalization schemes proposed in the literature. With the help of a Simulink model, an architecture will be proposed. The transistor level analysis of the aforementioned architecture will follow and will be supported by transistor level simulations of the receiver alone and of the complete transceiver, along with the digital control part.

Finally, an experimental characterization of the full link will be presented, analyzing its performances with measurements performed in the design center of Infineon Technologies, Villach (A).

# Contents

| Abstract i |                                         |                                                       |          |  |  |  |

|------------|-----------------------------------------|-------------------------------------------------------|----------|--|--|--|

| Index i    |                                         |                                                       |          |  |  |  |

| 1          | Intr                                    | roduction                                             | 1        |  |  |  |

|            | 1.1                                     | 1 Why do we need faster High Speed Serial Interfaces? |          |  |  |  |

|            | 1.2                                     | Evolution over the years                              | 2        |  |  |  |

|            | 1.3                                     |                                                       |          |  |  |  |

|            |                                         | lutions                                               | 5        |  |  |  |

|            |                                         | 1.3.1 Structure of the Transmitter                    | 5        |  |  |  |

|            |                                         | 1.3.2 Clocking Schemes                                | 7        |  |  |  |

|            |                                         | 1.3.2.1 Clock and Data Recovery                       | 8        |  |  |  |

|            |                                         | 1.3.2.2 Oscillator-Based Recovery                     | 11       |  |  |  |

|            |                                         | 1.3.2.3 Phase Interpolator-Based Recovery             | 11       |  |  |  |

|            |                                         | 1.3.2.4 Forwarded Clock Architecture                  | 12       |  |  |  |

|            |                                         |                                                       | 14       |  |  |  |

|            |                                         |                                                       | 14       |  |  |  |

|            |                                         | 1                                                     | 14       |  |  |  |

|            |                                         | 1.3.4 Equalization                                    | 17       |  |  |  |

|            |                                         | 1                                                     | 17       |  |  |  |

|            |                                         | 1                                                     | 18       |  |  |  |

|            |                                         |                                                       | 19<br>22 |  |  |  |

|            | 1.4                                     | 0 1                                                   |          |  |  |  |

|            | 1.5                                     | Motivation of the Work and Thesis Organization        | 24       |  |  |  |

| 2          | System Level Design of the Transmitter  |                                                       |          |  |  |  |

|            | 2.1                                     |                                                       |          |  |  |  |

|            | 2.2                                     | Driver Architecture                                   |          |  |  |  |

|            | 2.3                                     | Choice of the Equalization Taps                       |          |  |  |  |

|            | 2.4                                     | Example with Realistic Channels                       |          |  |  |  |

|            | 2.5                                     |                                                       | 43       |  |  |  |

|            | 2.6                                     | Architecture of the Transmitter                       | 48       |  |  |  |

| 3          | nsistor Level Design of the Transmitter | 51                                                    |          |  |  |  |

|            | 3.1                                     | Introduction                                          | 51       |  |  |  |

|            | 3.2                                     |                                                       | 51       |  |  |  |

|            | 3.3                                     | Switch Matrix                                         | 54       |  |  |  |

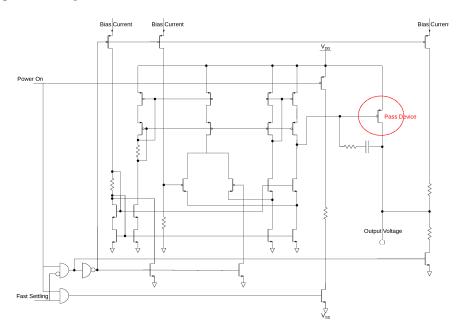

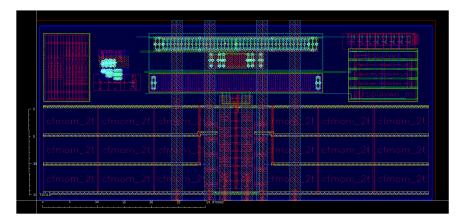

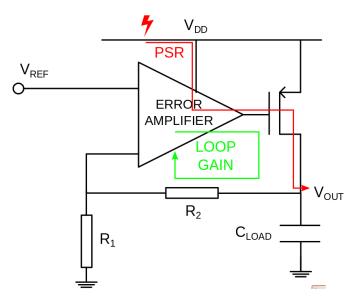

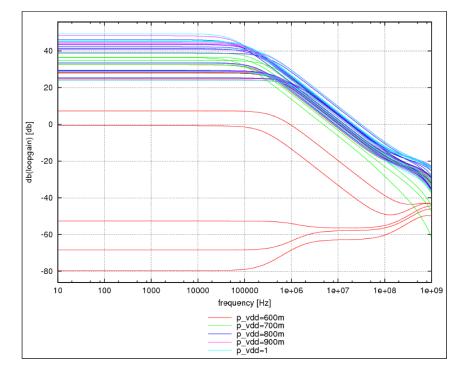

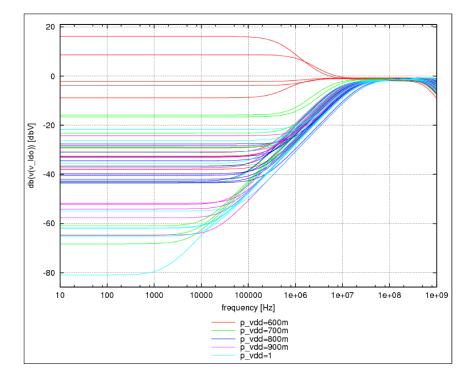

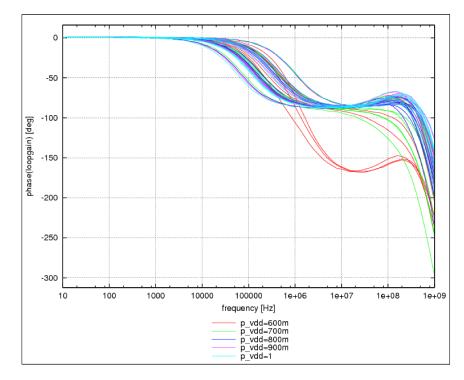

|            | 3.4                                     | LDO                                                   | 56       |  |  |  |

## CONTENTS

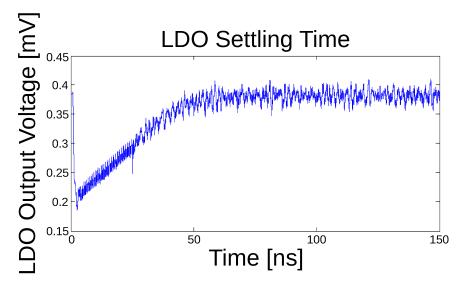

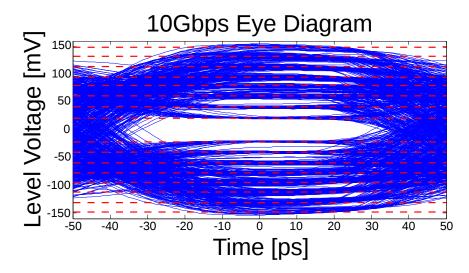

|                      | 3.5                                                | Simulation Results                                     | 61  |  |  |  |  |

|----------------------|----------------------------------------------------|--------------------------------------------------------|-----|--|--|--|--|

|                      | 3.6                                                | Analysis of the effect of parasitic inductances        | 64  |  |  |  |  |

|                      |                                                    | 3.6.1 Selection of the FFE taps                        | 65  |  |  |  |  |

|                      |                                                    | 3.6.2 Results without $V_{DD}$ and $V_{SS}$ inductance | 66  |  |  |  |  |

|                      |                                                    | 3.6.3 Results including VDD and VSS inductance         | 71  |  |  |  |  |

|                      | 3.7                                                | Conclusions                                            | 76  |  |  |  |  |

| 4                    | Experimental Characterization of the Transmitter   |                                                        |     |  |  |  |  |

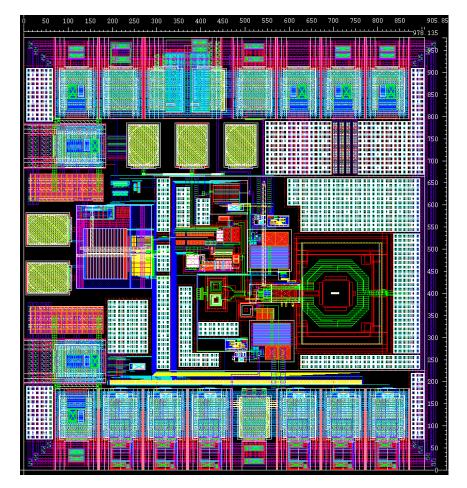

|                      | 4.1                                                | RMTX Test-Chip Overview                                | 77  |  |  |  |  |

|                      | 4.2                                                | RMTX Measurements Results                              | 79  |  |  |  |  |

|                      | 4.3                                                | InnoTC Overview                                        | 82  |  |  |  |  |

|                      | 4.4                                                | InnoTC Measurements Results                            | 82  |  |  |  |  |

| 5                    | System and Transistor Level Design of the Receiver |                                                        |     |  |  |  |  |

|                      | 5.1                                                | Structure of the receiver                              | 97  |  |  |  |  |

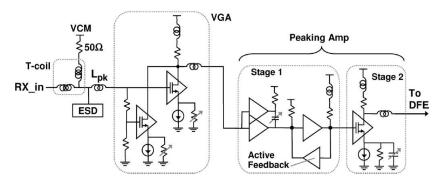

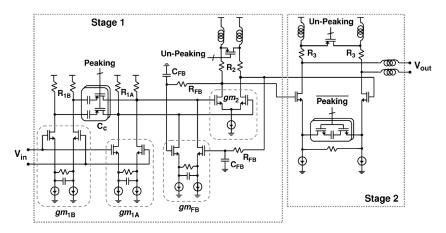

|                      |                                                    | 5.1.1 Input Amplifying Stage                           | 97  |  |  |  |  |

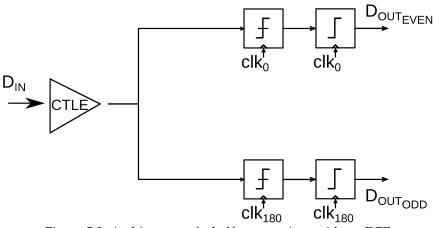

|                      |                                                    | 5.1.2 Half-Rate, CDR and DFE                           | 98  |  |  |  |  |

|                      |                                                    | 5.1.3 Architecture of the Receiver                     | 100 |  |  |  |  |

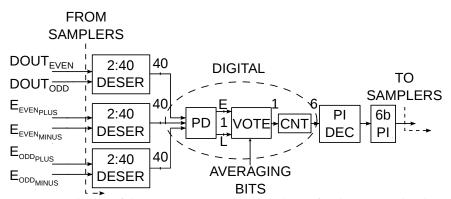

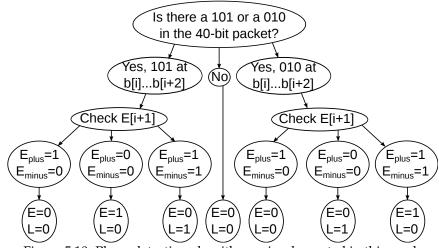

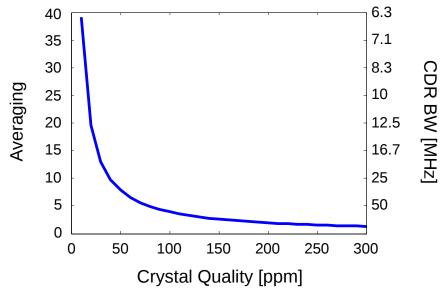

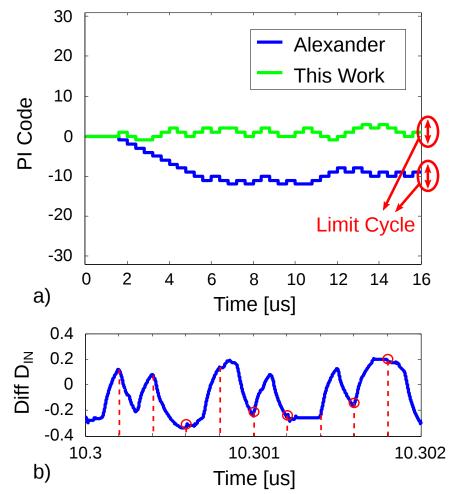

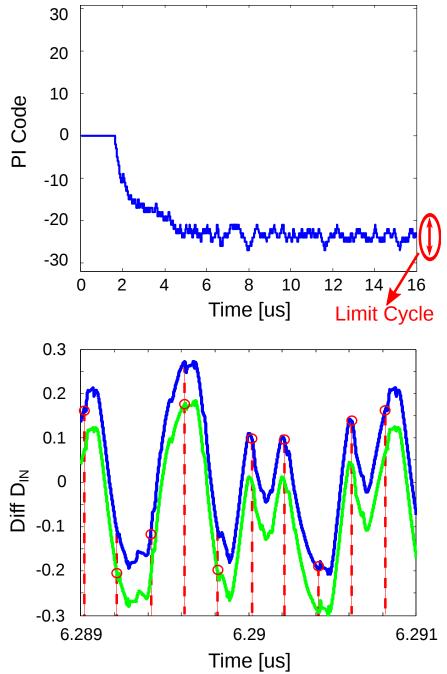

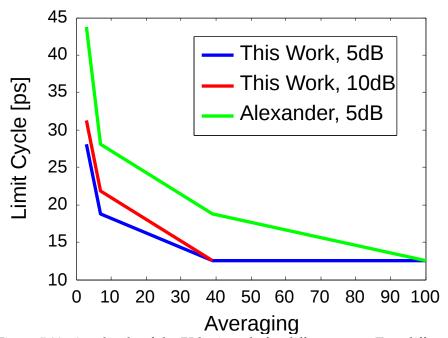

|                      | 5.2                                                | CDR Algorithm                                          | 102 |  |  |  |  |

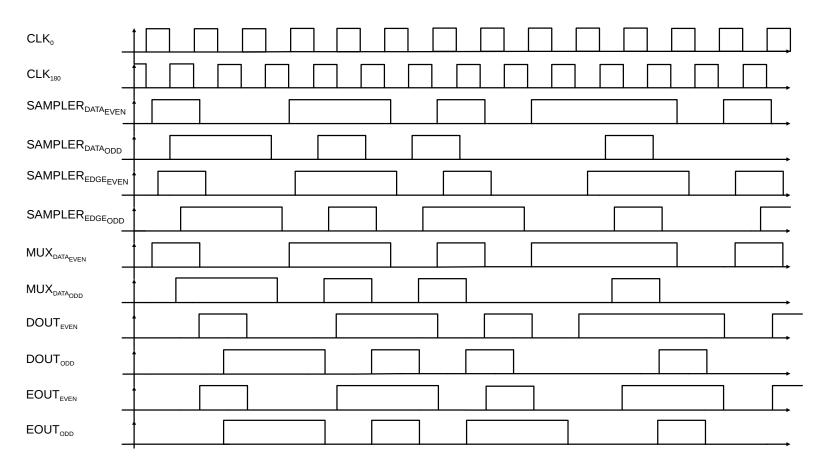

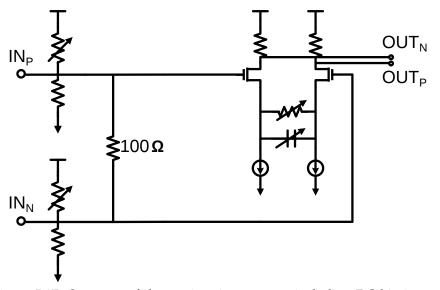

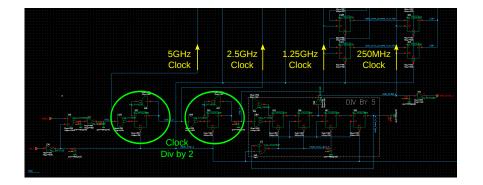

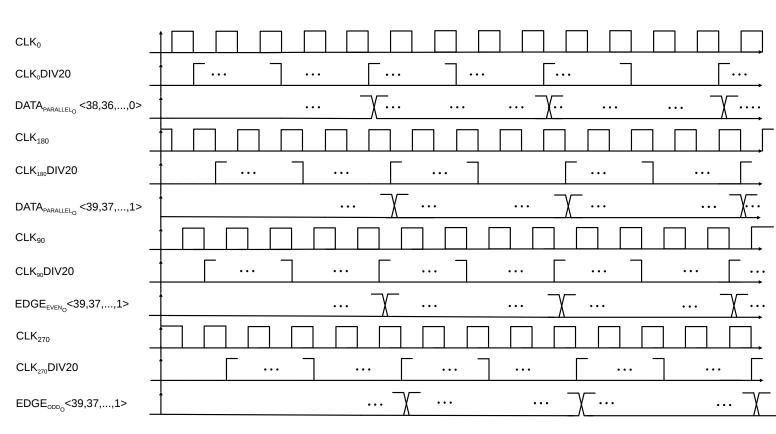

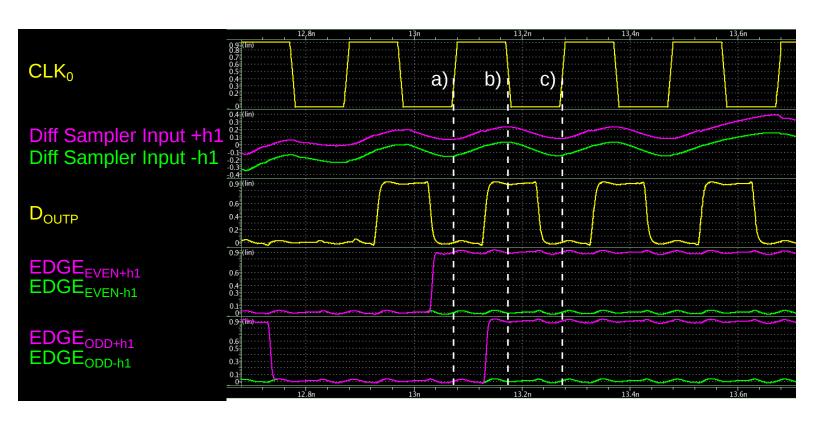

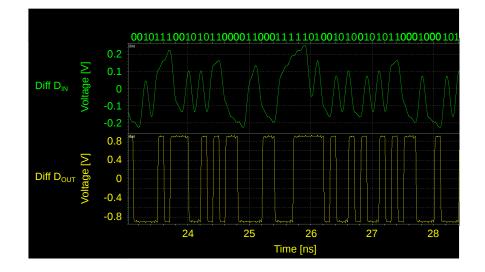

|                      | 5.3                                                | Transistor level design and simulation results         | 108 |  |  |  |  |

|                      |                                                    | 5.3.1 Input Stage                                      | 108 |  |  |  |  |

|                      |                                                    | 5.3.2 DFE Timing                                       | 112 |  |  |  |  |

|                      |                                                    | 5.3.3 Summers, Comparators and PI                      | 114 |  |  |  |  |

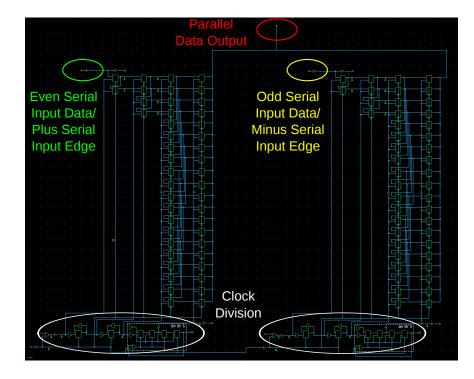

|                      |                                                    | 5.3.4 Deserializers                                    | 116 |  |  |  |  |

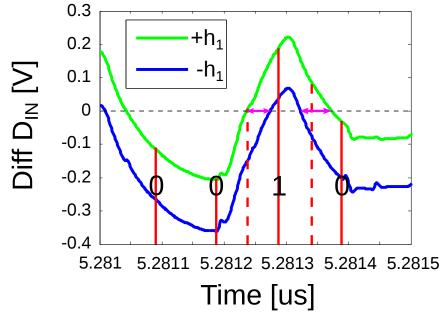

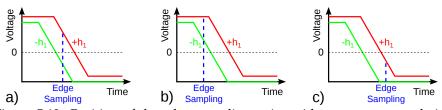

|                      |                                                    | 5.3.5 Timing of the CDR Algorithm                      | 119 |  |  |  |  |

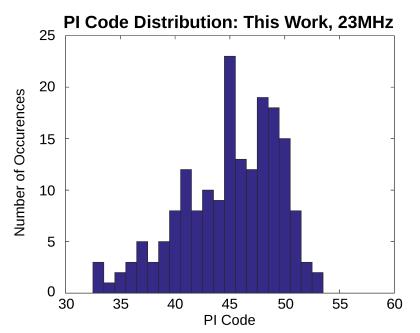

|                      |                                                    | 5.3.6 Results with fixed PI code                       | 121 |  |  |  |  |

|                      |                                                    | 5.3.7 Results with XA-VCS                              | 122 |  |  |  |  |

|                      | 5.4                                                | Conclusions                                            | 130 |  |  |  |  |

| 6                    | Cha                                                | racterization of the Full Link                         | 131 |  |  |  |  |

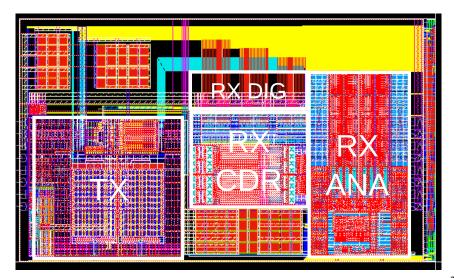

|                      | 6.1                                                | InnoTC Overview                                        | 131 |  |  |  |  |

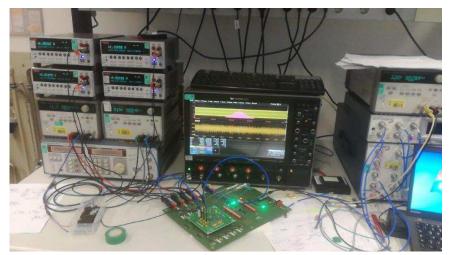

|                      | 6.2                                                | InnoTC Measurement Setup                               | 133 |  |  |  |  |

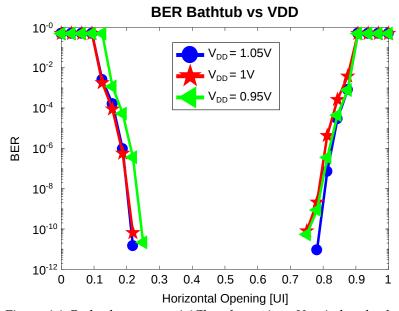

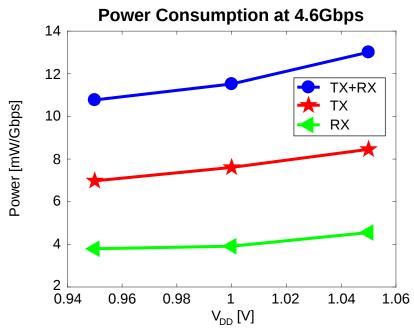

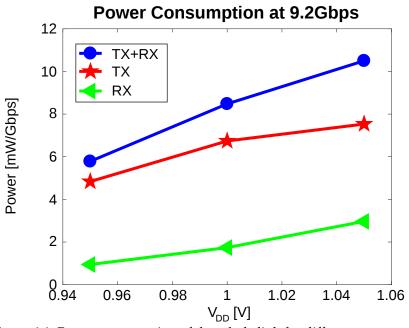

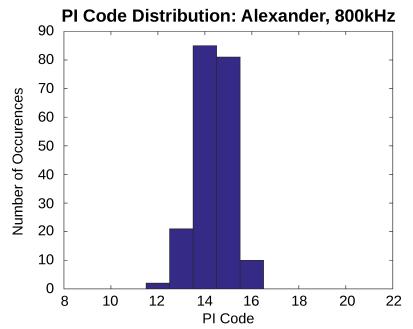

|                      | 6.3                                                | Full Link Measurements Results                         | 134 |  |  |  |  |

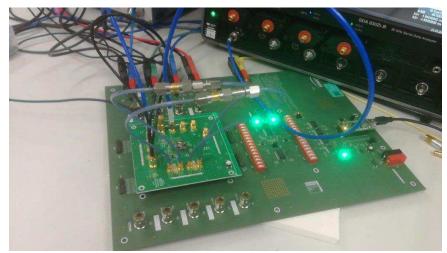

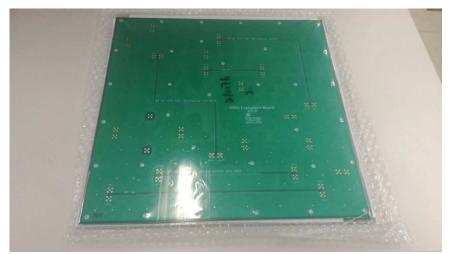

|                      | 6.4                                                | HSIO Evaluation Board                                  | 141 |  |  |  |  |

| Co                   | Conclusions                                        |                                                        |     |  |  |  |  |

| List of Publications |                                                    |                                                        |     |  |  |  |  |

| Acknowledgments      |                                                    |                                                        |     |  |  |  |  |

| Li                   | List of Publications                               |                                                        |     |  |  |  |  |

| Acknowledgments      |                                                    |                                                        |     |  |  |  |  |

iv

# Chapter 1

# Introduction

## 1.1 Why do we need faster High Speed Serial Interfaces?

Over the last decades, the innovation in semiconductor technology has been driven by Moore's Law, which states that the number of transistor in an integrated circuit doubles roughly every two year. A direct consequence of Moore's law is the continuous shrinkage of the feature size of the electronic devices and therefore a higher cut-off frequency for the devices themselves, which in turn enables a higher operation frequency for the integrated circuits and lower power consumption for each logic function to be performed. A natural consequence of all these points is an increased number of functionalities packed into a single processing unit and thus an increased amount of data to be stored and exchanged inside a single chip or among different chips.

There are two possible ways to achieve higher chip communication bandwidth: increase the number of serial interfaces or increase the transmission rate of the single interface. Increasing the number of I/O pins is in most cases not a viable options, both for padring space and cost (increasing the number of I/O pins means increasing the number of traces on the package and on the board, thus more metal and material to be placed on chip) reasons. In conclusion, increasing the data transmission rate of a single channel is a must for chip-tochip communication, even if doing so is complicated. In fact, aside from the technological improvement of the devices, the bandwidth of the transmission channel is an intrinsic limit that has to be overcome, possibly containing at the same time the power budget of the link.

## **1.2** Evolution over the years

Over the past years, the need for exchanging data has led to the pervasive presence of high speed serial interfaces (HSSI) in many application fields [1], for instance:

- Telecommunication networks, e.g. IEEE Ethernet Standards [2]-[3]

- Computing units with wire-lined I/Os, e.g. Peripheral Component Interconnect Express (PCIe) [4], Hypertransport [5], or inserted in wireless networks, linking the radio equipment control and the radio equipment in wireless base stations, e.g. Common Public Radio Interface (CPRI) [6]

- Interfaces inside optical networks, e.g. Interlaken [7] and OIF-CEI [8]

- Chip-to-chip and board-to-board links

- Storage Applications, e.g. Serial Advanced Technology Attachment (SATA) [9]

- High-performance embedded processing, e.g. Serial Rapid IO (SRIO) [10]

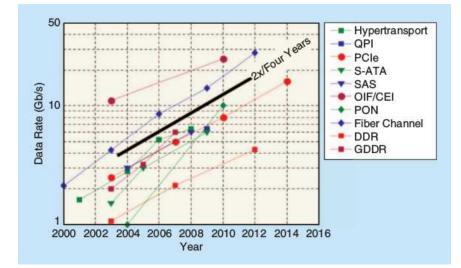

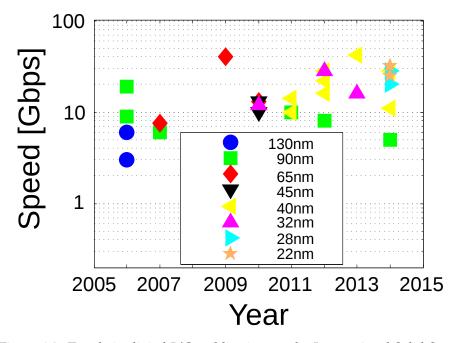

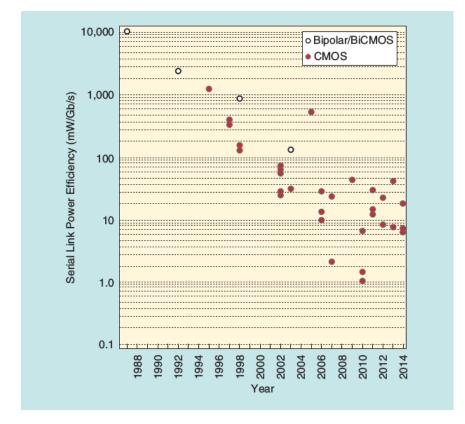

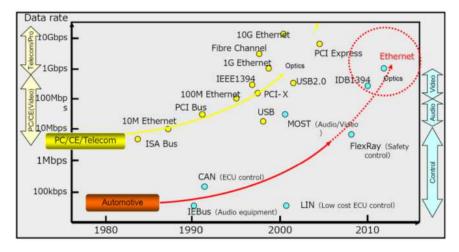

The variety of fields in which high speed serial links are nowadays used had brought to the adoption of many standards [11], sometimes conflicting between each other. In order to compare different standards, common definitions both for channel specifications and signal parameters [12]- [13] have been created. The speed of serial links in these fields reflects their different stages of maturity reached, as depicted in Fig. 1.1. The common trait is that the communication speed keeps increasing for all different applications, lagging some years behind state-of-the-art academic publications (see Fig. 1.2). Along with the increase in speed, there has been a corresponding improvement in power efficiency as shown in Fig. 1.3, even though channel limitations have become more and more severe going towards higher transmission rates.

Figure 1.1: Trend in emerging I/O standards, showing data rates doubling every four years [14]. QPI: QuickPath Interconnect; PCIe: Peripheral Component Interconnect Express; S-ATA: Serial AT Attachment; SAS: Serial Attached Small Computer System Interface; OIF/CEI: Optical Internetworking Forum/-Common Electrical I/O; PON: passive optical network; DDR: double data rate memory; GDDR: graphics double data rate memory.

Figure 1.2: Trends in digital I/O publications at the International Solid-State Circuits Conference for different technology nodes, showing a clear move toward high I/O data rates in more advanced CMOS technologies over time. Elaboration from a figure present in [14].

Figure 1.3: Serial Link Power Efficiency versus time both for hybrid BiC-MOS/CMOS and CMOS technologies [15].

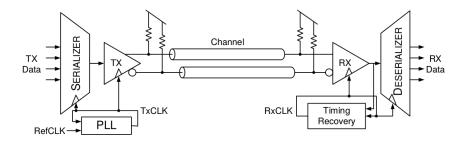

## 1.3 Architecture of a Serial Link: Main Problems and Proposed Solutions

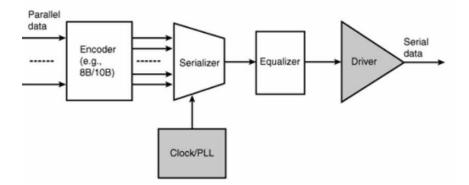

Fig.1.4 shows the general structure of a serial interface [16], including transmitter, channel and receiver. The first block we encounter is the serializer, which takes the parallel data from the digital side and outputs them serially to the driver. The driver generates an output voltage swing on the channel while at the same time having an output impedance matched to the channel to avoid reflections. The timing of the serializer and the driver itself is obtained via a clock reference and a Phase Locked Loop (PLL), which takes the low frequency of the crystal and multiplies it accordingly to the data rate frequency and to the one needed by the digital (normally, ten to one hundred times smaller than the data rate). After the channel, at the input of the receiver there is a slicer, which samples the actual received voltage value and compares it with a threshold to decide whether it is a '1' or a '0'. After this, the data is regenerated to CMOS values and is passed to the deserializer, which takes as an input the serial data stream and outputs parallel data to the digital post-processing. The sampling position of the slicer is fixed via a Timing Recovery Circuit, which aligns the clock with the incoming data stream so to have it positioned where it's easier to correctly distinguish between a '1' and a '0' value. In the following, all three main blocks composing a transceiver, transmitter, channel and receiver, will be analyzed in detail.

Figure 1.4: General Architecture of a high speed serial interface, including transmitter, channel and receiver [16].

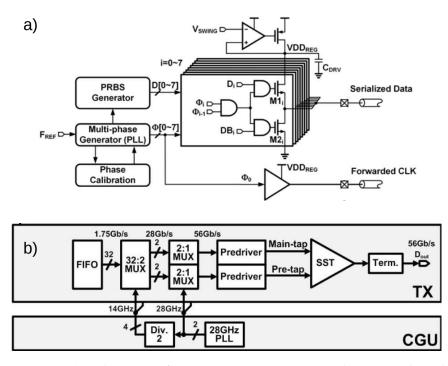

### **1.3.1** Structure of the Transmitter

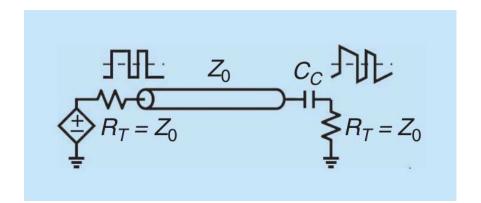

The general structure of a transmitter is reported in Fig. 1.5. Before transmitting the data as voltage levels via the driver, some digital preprocessing is usually performed by encoding the data, procedure that solves the problem of having a transmitter and a receiver block working on different DC levels [14]. In fact, this problem has to be faced every time two chips are communicating between each other, especially when they are fabricated in different technologies. The easiest solution to this problem is AC coupling, shown in Fig. 1.6. Anyway, using this structure, the ac coupling capacitance  $C_C$  and the receiver input termination resistance  $R_T$  form a high-pass filter, which in turn gives a slow loss of low-frequency components in the signal traveling along the chan-

nel. This loss results in a slowly drifting signal on the line whenever a long series of consecutive identical bits are to be transmitted: this issue is called baseline wander. This problem can be tackled in various manners: the easiest one is to use a very large AC capacitance so to have a very low cut-off frequency for the high-pass filter. Since this solution alone theoretically does not solve the problem, what can be done is to encode the data so to avoid the presence of extremely long sequences of identical bits, e.g. with the "8b10b encoding" [17]. This famous encoding scheme assures that no more than five identical bits in a row will be transmitted, but doing so it introduces a significant 25% overhead. Going towards higher data rates, more relaxed coding schemes introducing less overhead are now being used in many standards(e.g., 64b66b encoding in 10 Gigabit Ethernet [2]).

Figure 1.5: Typical structure of a high speed transmitter [18], including both digital preprocessing, analog transmission of the data and clocking concept.

Figure 1.6: To simplify the communication between two chips ac coupling is common, introducing a baseline wander in the received waveform [14].

Three are the main characteristics of the driver, which is the piece of the transmitter which outputs the analog levels on the channel: its mode (voltage or current, as we will discuss in extent in Chapter 2), its output swing and its output impedance. As previously said, it is of paramount importance to match the output impedance of the transmitter, especially going towards higher data

rates. At these frequencies, the wavelength of the transmitted signal is comparable with the physical length of a chip-to-chip communication link, therefore it is common practice to design the transmitter to match 50 $\Omega$ , which is the typical channel impedance for most serial links applications. Thus, given the fact that the output impedance to be matched is fixed, there is a strong interest in reducing the transmitter output signal swing in order to cut down the power dissipation on the termination resistance itself, given by  $\frac{V^2}{R}$ , where *V* is the voltage swing and *R* is the termination impedance. This has led to the development of various transmission standards based on Low Voltage Differential Signaling (LVDS), meaning by this that signals having low swing are traveling on the line.

### 1.3.2 Clocking Schemes

The clocking circuitry is an important part of a serial link, which varies depending on the adopted clocking strategy. Based on this, we can distinguish among four different classes of interfaces [14]:

- *Synchronous,* in which the clocks at the transmitter and at the receiver have exactly same frequency and same phase with respect to the data. This solution is almost never used at high data rates, as the wavelength at Nyquist frequency is comparable to the physical distance to go;

- *Mesochronous*, in which transmitter and receiver clock have exactly the same frequency, but different phase with respect to the data;

- *Plesiochronous*, in which transmitter and receiver clocks have almost the same frequency, but not precisely, and different phases with respect to the data;

- *Asynchronous,* where there is no relation whatsoever between the transmitter and the receiver clock. In links adopting this solution, normally the receiver does not even know about transmission rate.

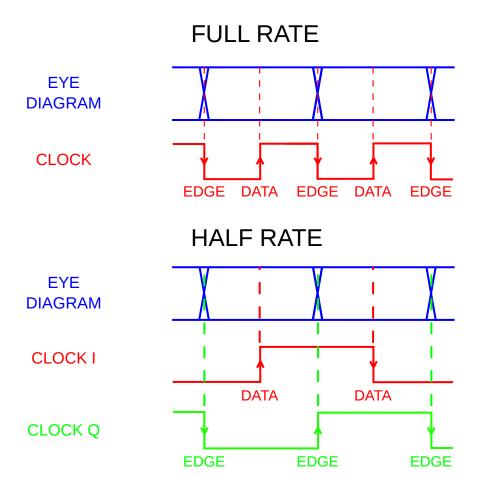

A common solution to relax the clocking circuitry, whatever the adopted clocking scheme is, is to use so-called *half-rate* architectures for transmitter and/or receiver. In half-rate architectures, the data are processed at a frequency which is the half of the data rate, but they are usually transmitted/received at full-rate, meaning that they travel along the transmission line at full-rate. Using parts of the transceiver at half of the speed means that also a half-rate clock has to be generated, which is less critical to manage than a full-rate one. This is done in order to relax the timing of some critical blocks in the circuit (e.g., flip-flops) that would be otherwise difficult to design for full-rate frequency. Using half-rates architectures has also the big advantage to lower the power consumption, since all the clocking distribution circuitry operates at half frequency. In the next chapters we will dive more into this concept, both for transmitter and receiver architectures.

#### 1.3.2.1 Clock and Data Recovery

It is easily understandable that, whatever the clocking scheme we are using is, at high frequencies the relation between data and clock at the transmitter side gets lost in the transmission, and it must be reconstructed at the receiver side. In fact, if the correct data-clock phase relation is not recreated, then it could happen that at the first sampling stage in the receiver wrong data are sampled, even though correct data have been transmitted, just because the sampling time is not the correct one. The circuit that takes care of aligning data and clock is the Clock and Data Recovery (CDR) [19], or as it is sometimes called Timing Recovery as in Fig. 1.4.

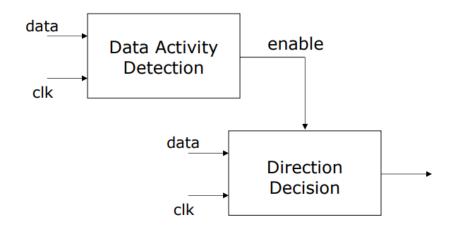

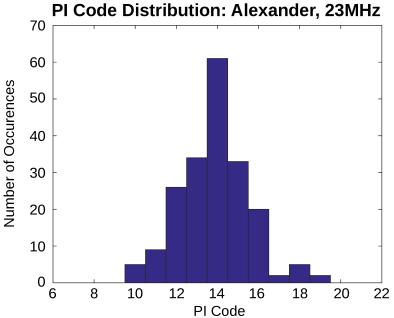

Since the job of the CDR is to align two phases, then a Phase Detector must always be present in it. As a particular study-case, we will now analyze the Alexander Phase Detector, one of the most commonly used Phase Detectors in High-Speed Interfaces. In order to extract phase informations, a transition in the data is needed: only when a transition occurs, the Phase Detector can take a decision (Fig. 1.7).

Figure 1.7: Generic scheme of a Phase Detector with Data Activity Detection.

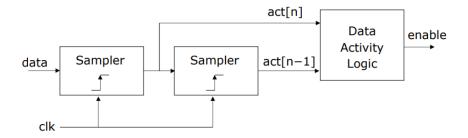

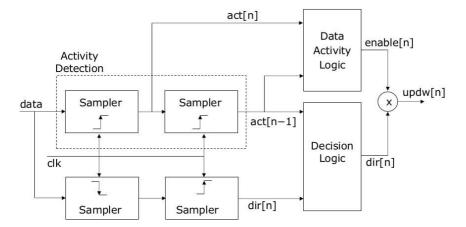

The easiest and most common way to implement a Data Activity Detector is shown in Fig. 1.8: the data are fed into a sampler chain and two consecutive bits are sampled (act[n-1] and act[n]); if the two are different, than a transition has occurred and the enable signal goes high.

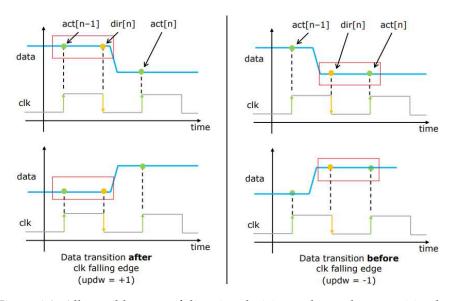

Once the direction decision block has been enabled, the edge sample enters in the picture. All possible cases when the enable signal is high are reported in Fig. 1.9: dir[n] is the edge sample, which is sampled at the falling edge of the clock, thus in anti-phase with the data. If the data transition occurs after the clock falling edge, then it means that the data have been sampled too early, therefore the decision will be to delay the next sampling point (updw = +1). If the data transition occurs before the clock falling edge, then it means that the data have been sampled too late, therefore the decision will be to anticipate the next sampling point (updw = -1).

The most straightforward way to implement the Direction Decision and to integrate it with the Data Transition Detection is shown in Fig. 1.10. The

### 1.3. ARCHITECTURE OF A SERIAL LINK: MAIN PROBLEMS AND PROPOSED SOLUTIONS9

Figure 1.8: Architecture of a data activity detector as implemented in an Alexander Phase Detector with full-rate clock.

Figure 1.9: All possible cases of direction decisions when a data transition has been detected in an Alexander Phase Detector with full-rate clock.

sampler that works on the rising edge of the clock in the direction decision is necessary to make sure that the output dir[n] is the sample of *data* associated with the falling edge of clock that occurred before the *n*-th rising edge of clock.

Figure 1.10: Block scheme of an Alexander Phase Detector, including both Data Activity Detection and Direction Decision circuitry.

The Alexander Phase Detector is a so-called Bang - Bang phase detector, by this meaning that it will take a direction decision every time it recognizes that a data transition has occurred. In a Bang-Bang phase detector, a stable operating point is when the system is in a limit cycle at the highest possible frequency, so when the Bang-Bang output (updw[n] in Fig. 1.10) swaps between -1 and 1 every clock cycle. In a CDR, the above limit cycle can thus occur only when the sampled data, act[n], swaps between 0 and 1 every clock cycle, hence the loop can correct for a phase error every clock cycle and the edge sample, dir[n], swaps between the value of sct[n] and act[n-1] every clock cycle.

Three are the most common solutions used in high speed links to embed the CDR in the transceiver: *oscillator-based recovery*, *phase interpolator-based recovery* and *forwarded clock architecture* [20].

#### 1.3. ARCHITECTURE OF A SERIAL LINK: MAIN PROBLEMS AND PROPOSED SOLUTIONS11

#### 1.3.2.2 Oscillator-Based Recovery

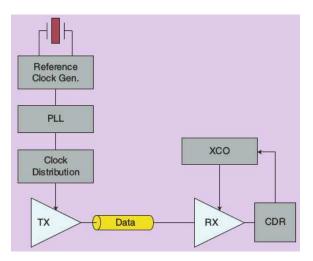

Fig.1.11 shows the scheme of a serial link with controlled oscillator(CO)-based clock recovery circuitry. This architecture falls under the asynchronous class, as the clock is generated thanks to a crystal reference and a PLL at the transmitter and then used for the data transmission timing. After the transmission, at the receiver side the Clock and Data Recovery (CDR) circuit reconstructs the clock from the timing of the received data by means of controlling a VCO (Voltage CO), both in frequency and phase, so to align the sampling clock with the data stream.

Figure 1.11: Scheme of a serial link with controlled oscillator-based clock recovery circuitry [20].

#### 1.3.2.3 Phase Interpolator-Based Recovery

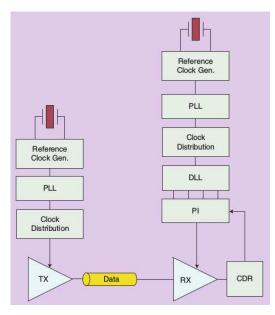

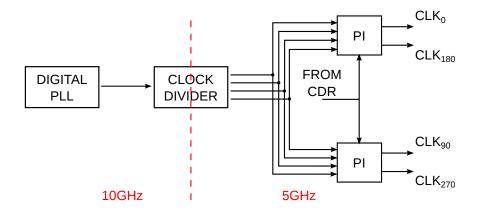

Fig.1.12 shows the architecture of a serial link with CDR based on phase interpolator. In this circuit, two clocks with nominally identical frequencies are generated at the transmitter and at the receiver thanks to two crystal references, which might differ inside the boundaries defined by their quality specifications, expressed in Parts Per Million (PPM). This means that this circuit falls under the category of plesiochronous systems. The CDR circuit at the receiver aligns the phase of the clock locally generated via a crystal and a PLL with the incoming data stream so to set an optimal sampling point. There are two main ways to do this, with a Delay Locked Loop (DLL) and with a clock divider and a Phase Interpolator (PI).

The DLL is an inverter chain that generates different delays with a separation step defined by the number of inverters inserted in the chain. If the separation step is fine enough, then one of the phases extracted from the DLL can be directly used to be the sampling clock.

In the second solution, the clock coming out from the PLL enters a clock divider, that outputs a clock with four different phases ( $0^\circ$ ,  $90^\circ$ ,  $180^\circ$  and  $270^\circ$ , the so-called I-Q phases). These four phases then enter a PI, that works as a

weighted summer between two of the four input phases [21]-[22], so that the clock at its output will have a phase somewhere in between these two.

This is done by means of a Delay Locked Loop (DLL) and a Phase Interpolator (PI). The DLL is an inverter chain that generates different delays with a separation step defined by the number of inverters inserted in the chain. Usually, four quadrature phases are extracted from the DLL, and then the PI interpolates among these four to obtain the correct phase to be applied to the clock.

Figure 1.12: Scheme of a serial link with phase interpolator-based clock recovery circuitry [20].

#### 1.3.2.4 Forwarded Clock Architecture

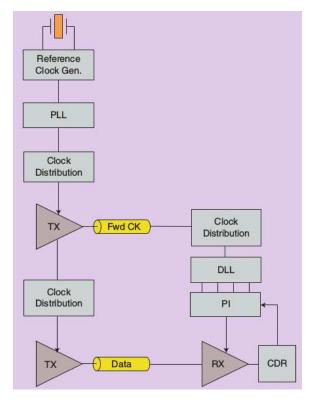

Fig.1.13 shows the scheme of a serial link with forwarded clock. In all previously analyzed schemes, the data was the only information transmitted to the receiver, whereas in this case both data and clock are sent over the channel. The clock is generated at the transmitter thanks to a crystal reference and a PLL, then sent with a different driver to the receiver along with the data. At the receiver side, the CDR then aligns the phase of the local clock with the incoming data stream, but with respect to the system described in Fig. 1.12 the difference is that the local clock is not generated by a crystal and a PLL, but it's the forwarded one. This circuit falls under the mesochronous systems category, but it's extremely impractical to be used at high data rates mostly because matched clock and data latency is not achievable. This in turn brings to a degradation of the CDR bandwidth, the highest jitter frequency the CDR can track. Moreover, using a different driver to transmit the clock requires more area and power, making this approach not so appealing.

## 1.3. ARCHITECTURE OF A SERIAL LINK: MAIN PROBLEMS AND PROPOSED SOLUTIONS13

Figure 1.13: Scheme of a serial link with forwarded clock architecture [20].

### 1.3.3 Noise and Interference Sources in Serial Links

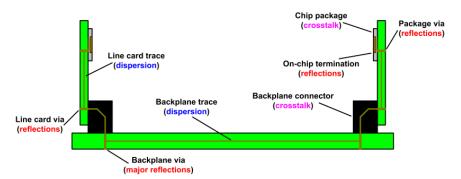

Fig.1.14 shows the cross-section of a complete backplane link and all elements that can bring interference and noise into the system. We have already introduced the bandwidth limitations given by the channel characteristics, but there is much more than that. A first rough distinction can be made dividing all disturbances into noise and dispersion characteristic of the link.

Figure 1.14: The cross-section of a complete backplane link, in which all elements of possible disturbances (reflections, crosstalk and dispersions) are highlighted [16].

#### 1.3.3.1 Noise Disturbances

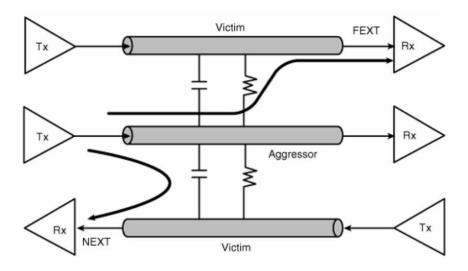

Noise sources can be roughly divided in two main category, *crosstalk* and *random signal fluctuations*. *Crosstalk* is a mechanism of coupling between two neighboring lines that can occur both via capacitance and mutual inductance, as can be seen in Fig. 1.15. In crosstalk two parts can always be identified, an *aggressor* and a *victim*. Depending on the position of these two, we refer to Far-End Crosstalk (FEXT) or Near-End Crosstalk (NEXT). The latter is the most dangerous one, because the aggressor is on the same chip as the victim and near to it, therefore it is a direct coupling mechanism. In FEXT, the energy of the aggressor travels along the channel and then couples at the receiver's side with the victim, being therefore already attenuated by the medium. *Random signal fluctuations* is always present in the system due to thermal and shot noise of active and passive devices and results in timing deviations of the signals, causing crossing edges to be anticipated or postponed. These deviations fall under the definition of *jitter*, which we will often talk about in the following.

### 1.3.3.2 Dispersion of the Transmission Medium

In this subsection we will analyze the dispersion and loss mechanisms inherent to the transmission medium, namely skin effect, dielectric loss and impedance mismatch and discontinuities.

Skin effect is a form of channel insertion loss, given by the fact that at high frequencies the effective cross-section of the wire in which the current flows

Figure 1.15: Two different crosstalk mechanisms, Near-End Crosstalk (NEXT) and Far-End Crosstalk (FEXT) [18].

reduces and therefore current is flowing just in the proximity of the surface. This effect can be modeled into a frequency dependence of the impedance per unit length of the channel that reads as

$$R(f) = R_0 + \sqrt{f} \cdot (1+j) R_S$$

(1.1)

where  $R_0$  is the channel DC loss per unit length and  $R_S$  is a skin effect constant. The dependence upon  $\sqrt{f}$  means that the skin effect causes a loss of 10dB/decade.

Dielectric loss is given by the absorption of energy by the dielectric medium from the traveling wave, which is in turn transformed into heat. This effect can be summarized into an imaginary part of the permittivity  $\epsilon$  of the dielectric medium that reads

$$\epsilon(f) = \epsilon'(f) - j\epsilon''(f) \tag{1.2}$$

where *j* is the imaginary unit. Eq. 1.3 can be rewritten in the form of an admittance to ground as

$$Y_{\perp}(\omega) = j\omega C + \omega C \tan(\delta)$$

(1.3)

where *C* is the transmission line's capacitance at low frequencies and  $\delta$  is the loss angle. The dielectric loss results in a loss dependence of 20 dB/decade at high frequencies, where  $Y_{\perp}(\omega)$  gets high.

The third loss mechanism to analyze is impedance mismatch and discontinuities. Packaging, sockets, connection to ac-coupling capacitors, PCB vias and connectors of different nature all introduce discontinuities in the channel's impedance [23], that in turn generate signal reflections that show up as notches in the pulse response of the system. Another effect of impedance mismatch is *mode conversion* [24]: part of the energy of a differential signal is transformed into a common mode component, that in turn may cause reflections.

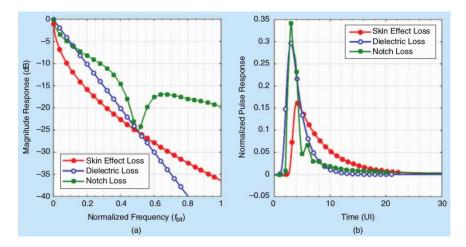

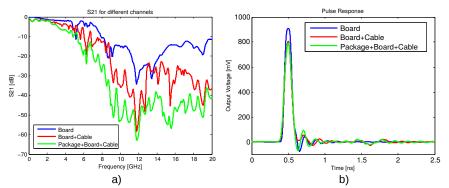

In a generic channel, all these effects are coupled together and show up in the pulse response of the channel. In order to identify which loss mechanism is the dominant one in a channel, one might look either at the magnitude of the transfer function (also called  $S_{21}$ ) or at the pulse response of the system, since they are strictly related to each other: both these metrics are shown in Fig.1.16. To better understand these pictures, we have to introduce the concept of InterSymbol Interference (from now on, ISI). ISI is a form of distortion of a transmitted bit in which one bit interferes with the subsequent and/or the previous ones. The amount of ISI of a channel can be derived by looking at its pulse response (Fig. 1.16 (b)): all residuals in the UIs before and after the one at which the pulse is transmitted interfere with the following bits. All residuals in the UIs before the current bit are called *pre-cursors*, all the ones after the current bit are called *post-cursors*. The current bit is often referred to as main-cursor. ISI is the reason why usually defining just the loss at a certain frequency is not enough in order to decide for an equalization strategy, and this can be better understood by looking at Fig. 1.16: in fact, all  $S_{21}$  shown in the figure present a loss of 25dB at half the transmission frequency (the so called Nyquist frequency), but the rest of the spectrum may vary very much from one interference mechanism to the other. In Fig. 1.16 b), the normalized pulse response (i.e. a pulse response scaled so that the absolute sum of all pre-, post- and main-cursors is 1) of the  $S_{21}$  is shown.

Figure 1.16: On the left,  $S_{21}$  (magnitude of the transfer function) versus normalized frequency  $(\frac{f}{f_{bit}})$ , where  $f_{bit}$  is the transmission frequency). On the right, normalized pulse response (i.e. the pulse response is scaled so that the absolute sum of all pre-, post- and main-cursors is 1) of the channel versus time, normalized in UI (1 UI equals to one bit period, thus  $1UI=\frac{1}{f_{bit}}$ ). Both graphs are shown for three different channels, one dominated by skin effect, one by dielectric loss and one by impedance discontinuities.

## 1.3.4 Equalization

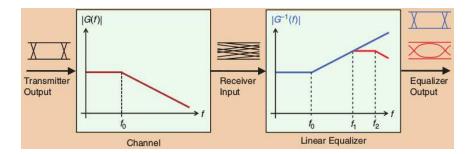

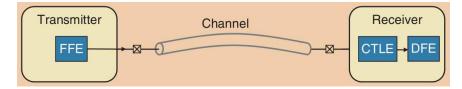

As mentioned in the previous section, especially when moving towards extremely high data rates, the transmitting medium can completely kill the ability of a transceiver to establish even a Non-Return-to-Zero (NRZ) communication. What the designer can do is to foresee such detrimental effect of the channel and to compensate for it: this compensation is what in the literature is called equalization [25]- [26]. The main idea behind equalization is shown in Fig. 1.17: the "non-flatness" in the transfer function of the transmitting medium are compensated for by means of an inverse transfer function. Assuming the nonideality in the transfer function to be proportional to the frequency (i.e., given by skin effect or dielectric loss), it is identical to apply the correction either at the transmitter or at the receiver. If the behavior of the non-ideality versus frequency is not merely proportional, but with various notches (i.e. coming from impedance discontinuities), then it's possible to correct for it either via digital techniques (e.g., with a Finite Impulse Response filter) or with non-linear ones (e.g., Decision Feedback Equalization). In the following subsections we will analyze the most used equalization techniques that can be found nowadays in serial links and are listed in Fig. 1.18.

Figure 1.17: Transfer function of the channel, G(f) and inverse transfer function,  $G^{-1}(f)$ , applied as an equalization technique, along with the eye diagram at the output of the transmitter, at the input of the receiver and after equalization [26].

Figure 1.18: General structure of a serial link in which the most common equalization techniques have been highlighted [26].

### 1.3.4.1 Feed-Forward Equalization

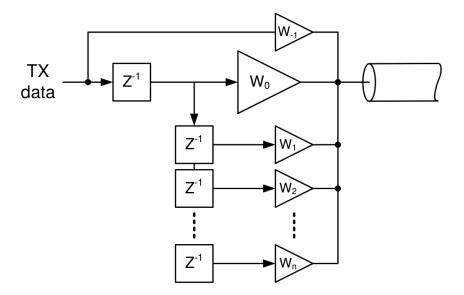

Equalization at the transmitter is done via preconditioning of the signal before setting the voltage level at the input of the channel. In order to do so, one has two possible choices: amplifying the high-frequency components (*pre-emphasis*) or reducing the low-frequency ones (*de-emphasis*), since the wanted effect is anyway the one of a high-pass filter to counteract the low-pass characteristics of the channel. This can be easily done by multiplying delayed versions of the bit stream to be transmitted (the so called *taps*) by weighted coefficients. Delayed data can be easily created since the clocking circuitry is always present at transmitter side. This approach is sketched in Fig. 1.19 and will be vastly analyzed in the following chapters.

Figure 1.19: Conceptual scheme of a feed-forward equalization with one precursor tap, the main tap and *n* taps, created via a flip-flop register chain [16].

As can be understood, this approach can be applied both at transmitter and at receiver side [27]-[28]-[29]- [30]. Anyway, usually such FIR filter is implemented at transmitter side (FFE) because at this point of the transmission chain the system is still working with digital bits, '1' or '0', coming directly from the digital encoding and thus easy to create delayed versions of just with a simple register chain, while the multiplication by suitable coefficients is realized by means of switching circuits. On the other hand using this approach at the receiver would imply working with analog signals. To avoid this, one could replace the first sampler at the receiver side with a very fast ADC, so to digitize the signal and then apply FFE [31], [32], [33]. As shown in the Fig. 1.19, all taps are summed together at the output of the transmitter, just before entering the channel.

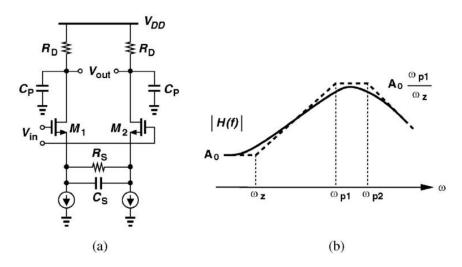

#### 1.3.4.2 Continuous Time Linear Equalization

Continuous Time Linear Equalization (CTLE) is a linear technique that is implemented in the Analog Front-End (AFE) of the receiver. Fig. 1.20 show a typical implementation of this concept and explains what's its aim and how it is achieved. The goal of using CTLE is to compensate for the low-pass characteristics of the channel by introducing a zero at a frequency slightly smaller than the data rate. This is usually obtained with a source-degenerated differential pair, which has a high-pass filter behavior if the zero frequency is designed to be much lower than the dominant pole, which should be the one given by the output parasitics capacitance  $C_P$ . This technique works equally well both for pre-cursors and post-cursors, since it directly acts on the transfer function of the system.

Figure 1.20: Source-degenerated differential pair used as CTLE: a) circuit implementation and b) transfer characteristic, both in its asymptotic approximation (dashed line) and its real version (full line) [34].

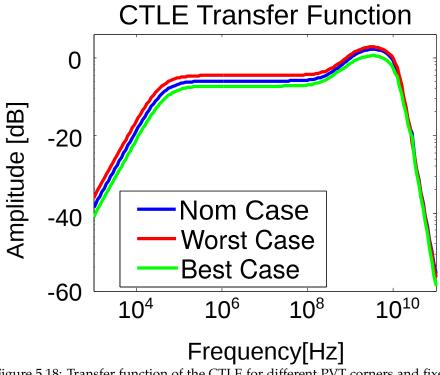

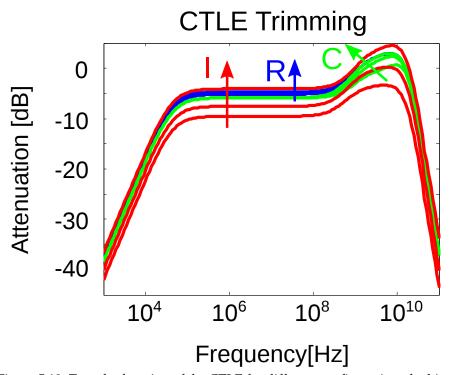

The main problem of CTLE is that with a single-stage implementation as the one shown in Fig. 1.20 a) is hard to obtain a high peaking gain. If one wants to have high-gain it should use multi-stage architectures, as many cascaded source-degenerated differential pair, but then it becomes extremely difficult to tune all parasitic poles present in such a structure over broad PVT variation ranges typical of the automotive environment. For this reason, CTLE normally acts together with other equalization schemes and is used as a mean of facilitating the work of other equalization techniques (e.g., DFE).

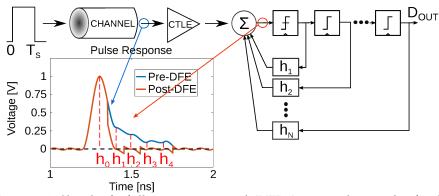

#### 1.3.4.3 Decision Feedback Equalization

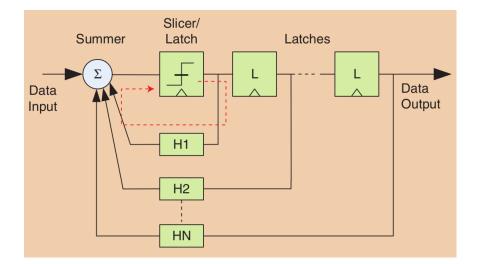

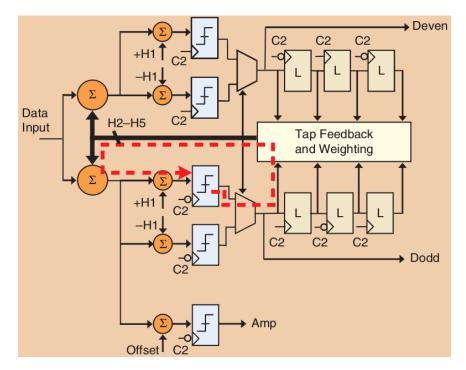

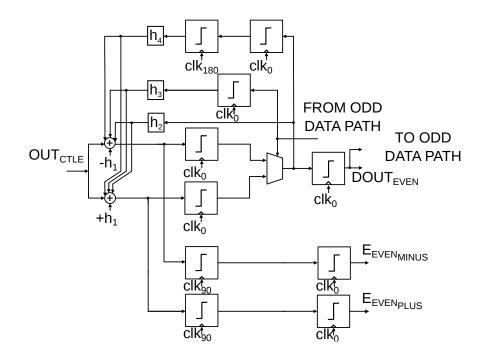

Decision Feedback Equalization (DFE) is a non-linear technique that is applied at the receiver side, usually after a CTLE stage. The idea behind DFE is to directly address Inter-Symbol Interference acting on the incoming analog voltage levels based on the already-detected bits, as shown in Fig. 5.1. The last sentence implies that it's not possible to address any pre-cursor ISI, and therefore DFE is normally used in collaboration with FFE or/and CTLE.

The biggest advantage of DFE is that, contrarily to FFE and CTLE, it does not amplify high-frequency noise, since it works on previously sampled digital bits: for this reason, over the last years researcher started to heavily prefer DFE to FFE. It can be understood also that this equalization technique is particularly effective when it comes to equalize for impedance discontinuities, which as we have seen manifest themselves as notches in the  $S_{21}$  curve, as it precisely counteracts for ISI and it is thus able to correct those notches [35]. On the contrary, the main drawback of this equalization technique is error propagation: if the noise at the input of the slicer is so big that a wrong detection occurs, this wrong decision affects in a detrimental way the equalization of the following bits, until a stream of correct bits are recognized and the error is pipe-cleaned out of the shift register composed by *N* latches for an *N*-tap DFE. So, while DFE is generally useful to decrease the Bit Error Rate (BER), from time to time it may occur that bursts of errors appear and need to be corrected. For this reason, it is quite common to use forward error correction codes (e.g., Reed-Solomon) in addition to it, to correct for these error bursts.

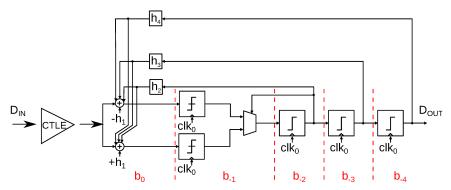

Another issue in implementing DFE is the stringent timing constraints that it imposes: in fact, the feedback loop corresponding to the first tap has to come in one bit period. While this might not be an issue while transmitting at low data rates, it means that for a receiver that works at 10Gbps the time for closing the feedback loop is 100ps. In order to address this problem, a variety of techniques have been used: the most common solution is to mix decision lookahead schemes (the so called *loop unrolling* techniques) with half rate ones, to increase even by four times the time for closing the feedback loop, see Fig. 1.22.

Figure 1.21: Conceptual scheme of a receiver with an N-tap DFE [26]. Highlighted in red there is the critical path whose timing has to be guaranteed at very high data rates.

20

## 1.3. ARCHITECTURE OF A SERIAL LINK: MAIN PROBLEMS AND PROPOSED SOLUTIONS21

Figure 1.22: Conceptual scheme of a half-rate receiver featuring 5-tap DFE with a 1-tap loop unrolling [26]. The critical path, shown in red, is now two times longer than the one of Fig. 5.1. In the bottom branch of the receiver there is the so called *eye monitoring*, which checks the effective improvement of the eye diagram after DFE is applied.

## 1.4 High Speed Serial Interfaces in the Automotive Environment

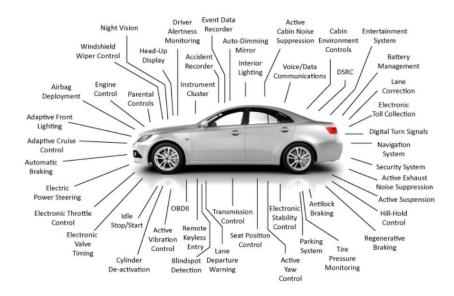

Nowadays, pervasive and smart electronics is present in every aspect of our life, by this meaning that the environment in which we are living is capable to react appropriately in case of foreseeable events thanks to the presence of sensors and actuators. Vehicles have followed this same path, driven by development of actuators, control and monitoring systems for different applications inside the car, ranging from Safety and Infotainment to Drive Assistance, Power-train and Comfort, as briefly summarized in Fig. 1.23.

Figure 1.23: Partial summary of electronic-aided functions that can be found in a car nowadays.

The increase of electronics in automotive environment seems unavoidable, and the market to be shared is very likely to continue to grow in the next decades [36]- [37]- [38], especially with the advent of Advanced Driver Assistance Systems (ADAS) and autonomous driving in the upcoming years, not to mention the already ongoing explosion of the infotainment sector. The amount of functions to be performed in vehicles is increasing everyday, thus also the number of Electronic Control Units (ECUs) present in a car is going to further raise. Increasing the number of computational nodes implies increasing the network connection among these nodes, therefore increasing the amount of data to be exchanged and thus strongly enhancing the current data transmission rate.

Nowadays, the most diffused communication standards inside the vehicles are Controller Area Network (CAN), Local Interconnect Network (LIN) and Flexray, but all these standards range from few kb/s to 10Mb/s. It is clear that the applications cited above require much higher data-rate, and the adoption of 1Gbps Ethernet as a standard for automotive goes exactly in this direction and demonstrates a trend that is going to be confirmed in the next years. In

| Parameter                           | Consumer                       | Automotive           |

|-------------------------------------|--------------------------------|----------------------|

| Temperature                         | $0^{\circ}$ C - $40^{\circ}$ C | -40°С - 175°С        |

| Voltage                             | 3.3V                           | 80V                  |

| Operation Time                      | 1-3 years                      | up to 25 years       |

| Humidity                            | Low                            | 0% to 100%           |

| <b>Tolerated Field Failure Rate</b> | <1000ppm                       | Target: zero failure |

| ESD                                 | 4-8kV                          | 8-15kV               |

|                                     |                                |                      |

Table 1.1: Requirements of automotive electronics [40].

fact, as shown in Fig. 1.24, the increase in data transmission rate in automotive environment follows the one in consumer electronics, but with 10-15 years of delay. So it's quite fair to assume that in few years having serial connections at 10Gbps will be the state-of-the-art for automotive.

Figure 1.24: Overview of data rates over the last decades for both consumer and automotive electronics [39]. From the graph it can be seen that automotive electronics follows the improvement of the consumer market, but lags behind it by 10-15 years.

Nevertheless, a direct technology transfer from consumer to automotive environment is not possible, due to the serious challenges that the harsh automotive standards pose to the circuit designers, especially to HSSI designers. In fact, requirements in automotive environment are much more stringent than for consumer applications, as summarized in Tab. 1.1.

The requirements that pose the highest challenge to the HSSI designer are for sure the extremely broad temperature range, in which very shrunk devices may see their threshold voltage  $V_T$  vary even by 200mV, and ESD protection, which works as a low-pass filter for the transmitter output and receiver input and may therefore be a killing aspect. From what we have stated above, it appears quite clear that designing HSSIs in an automotive environment is a path full of obstacles, even more than in the other markets.

## 1.5 Motivation of the Work and Thesis Organization

From this introduction, it appears clear that there is a strong interest surrounding the world of high speed serial interfaces, both in the academic and industrial world. At the same time, it is pretty understandable that the automotive sector lags some years behind the consumer market, especially due to the stringent safety requirements and the extremely harsh environment in which the link must be able to correctly operate. Thus, the main goal of this work is to bridge the gap between the consumer electronic and the automotive electronic unit world, understanding which techniques are suitable for our work conditions among the ones that are already well established in the academic world and translating and improving these solutions to possibly make them more stable and less power consuming. This goal implies a deep understanding of a serial link both at system and transistor level, and the development of this thesis will follow this idea. After this introduction, the thesis is divided into chapters, which will be here briefly presented:

- Chapter 2 focuses on the system level design of the transmitter, creating a procedure to assess the equalization strategy at the transmitter side and defining its main parameters by evaluating performance metrics as pulse response and eye diagram;

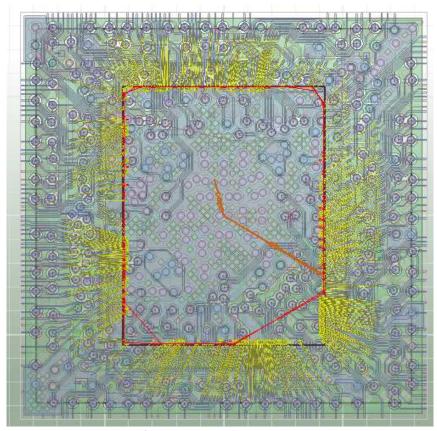

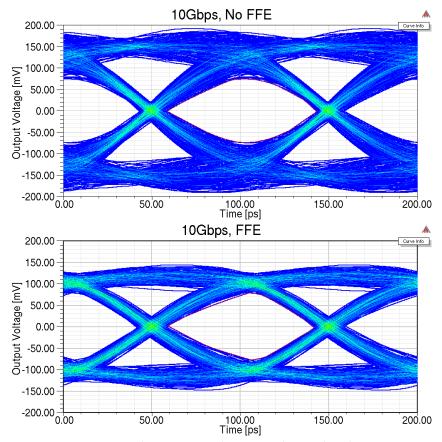

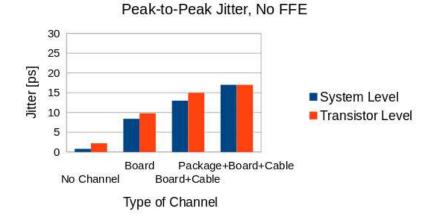

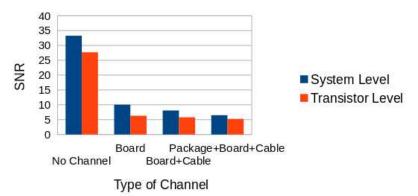

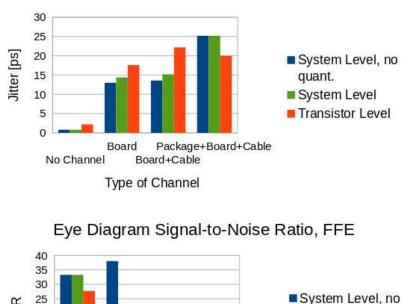

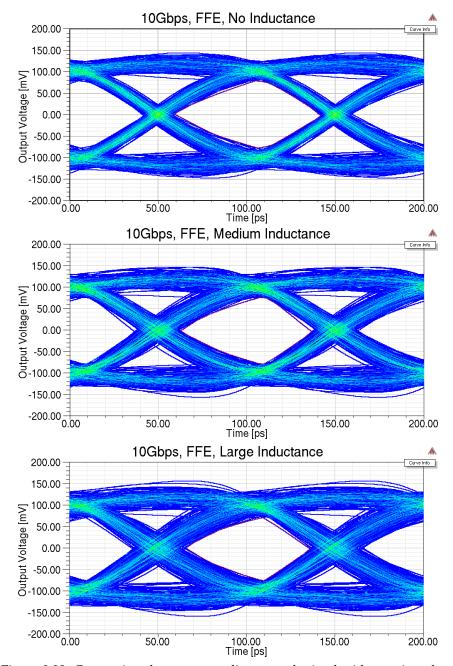

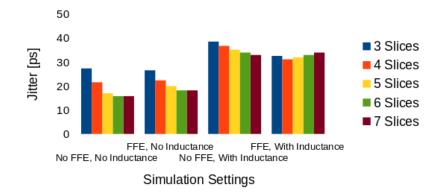

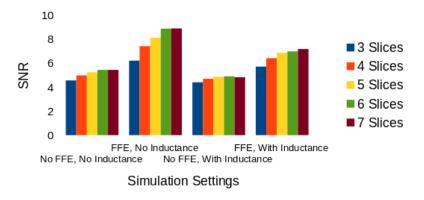

- Chapter 3 is centered around the transistor level design of the transmitter. Here design choices stemming from literature will be analyzed, justified and explained. The design of a 10Gbps transmitter will be detailed along with the results deriving from schematic and post-layout simulations. After this, a schematic analysis of the effect of parasitic inductance on FFE will be carried out.

- Chapter 4 talks about the experimental characterization of the transmitter above, showing the results of the measurements of the first test-chip and demonstrating the improvements in BER obtained thanks to FFE.

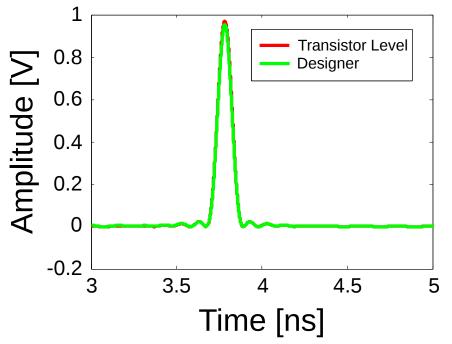

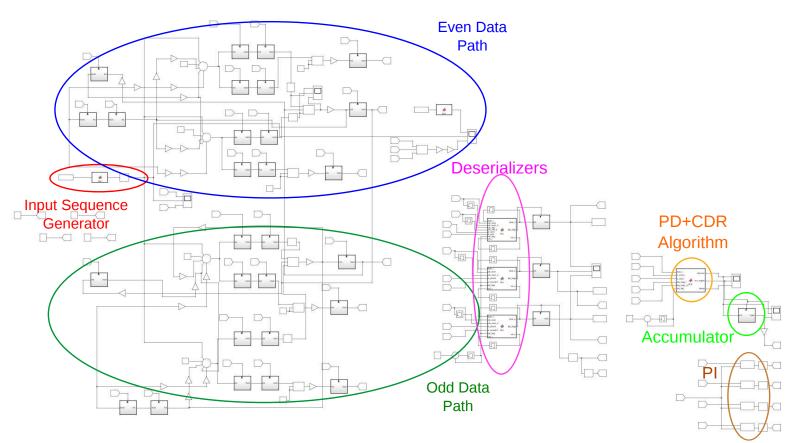

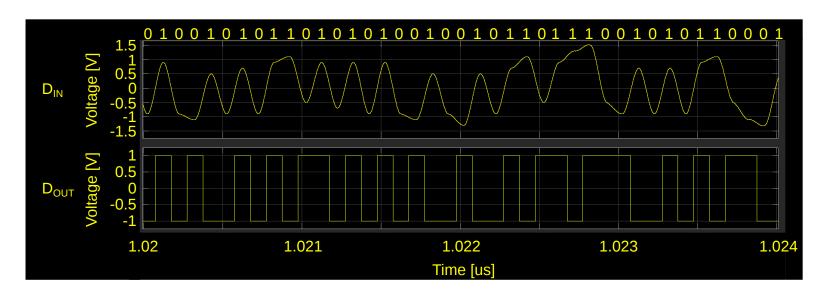

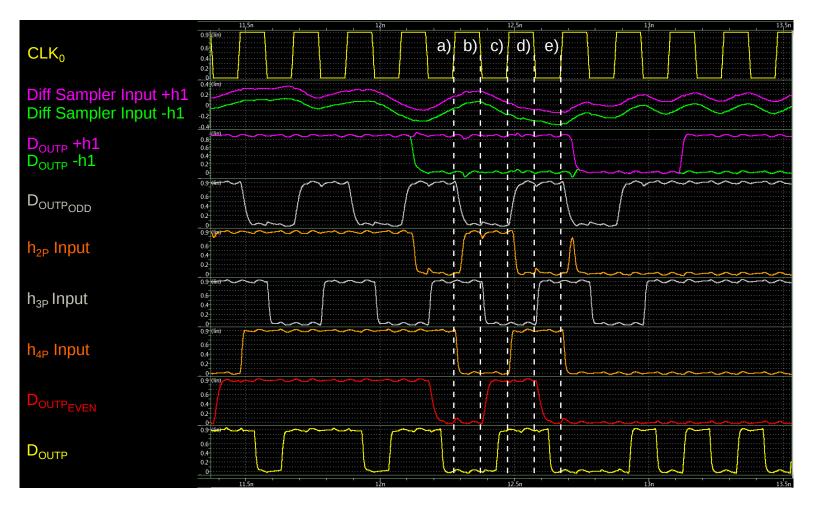

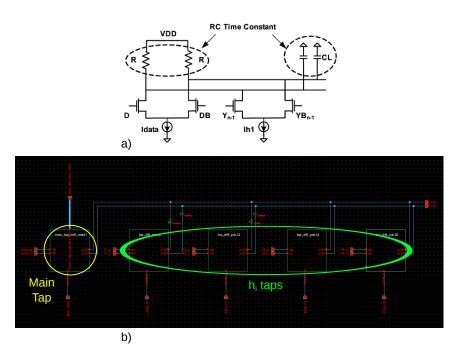

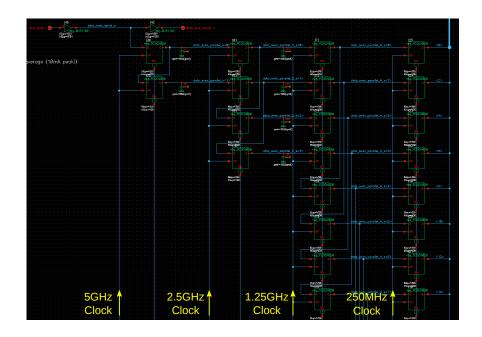

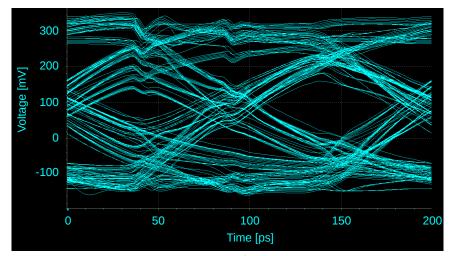

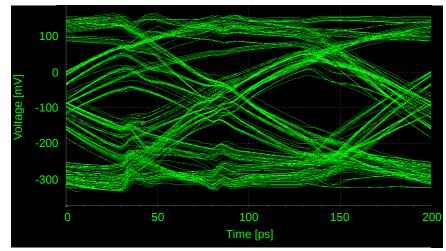

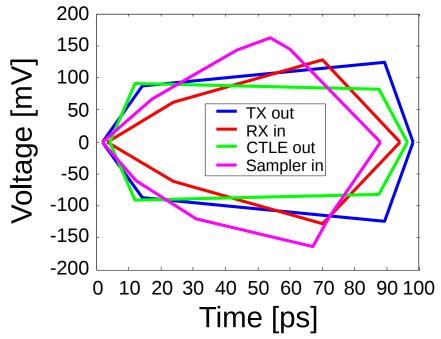

- Chapter 5 deepens on the system and transistor level analysis of the receiver. Here an extensive review of the existing literature will go by with a complete Simulink representation of a half rate receiver with DFE and loop unrolling, so to guide the design choices. Along with this, our CDR implementation will be presented. The transistor level design will be confirmed with post-layout simulations of single receiver blocks (CDR, DFE+CTLE) and schematic simulations of the whole 10Gbps system including transmitter and receiver. Finally, mixed-signal simulation will help to verify the correctness of the CDR and its algorithm.

- Chapter 6 regards the characterization of the receiver, showing the results of the measurements performed in the lab on the second test-chip.

- Chapter 7 wraps up all work done so far, presenting the results of the whole transceiver and illustrating all possible equalization and CDR solutions implemented in our design.

### 1.5. MOTIVATION OF THE WORK AND THESIS ORGANIZATION 25

• Finally, an appendix about Electromagnetic Interference (EMI) in High-Speed Serial Interfaces, topic analyzed in the first months of work, will be added in the final version of the thesis.

## Chapter 2

# System Level Design of the Transmitter

This chapter will focus on the system level design of the transmitter, creating a procedure to assess the equalization strategy at the transmitter side and defining its main parameters by evaluating performance metrics as pulse response and eye diagram.

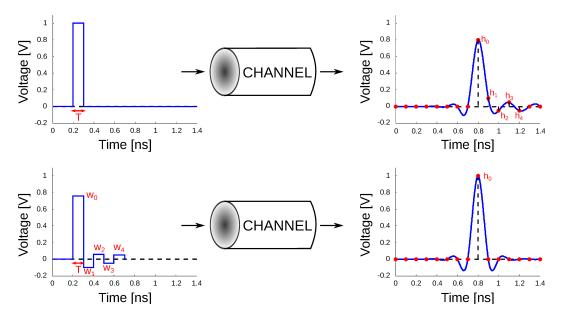

In the introduction, we have talked about the rise of high-speed links and their increase in speed over the last years. Since the baud rates at which these links work today are extremely high, inter-symbol interference (ISI) has become the most limiting factor [41]. In order to mitigate ISI, the most effective solution is channel equalization [26]. We have seen that equalization can be done either at the transmitter side just before the channel (and it is called Feed-Forward Equalization, FFE) or at the receiver (for example in the form of Decision-Feedback Equalization, DFE). In this chapter we will focus on the system level design of the transmitter: our goal is to create a procedure to analyze the amount of equalization needed at the transmitter side depending on the channel, calculate the weights for such equalization scheme and assessing the impact of tap quantization in a real-world scenario. After this, the correctness of the applied FFE will be evaluated by checking the pulse response and some eye diagram parameters, such as eye height and eye width.

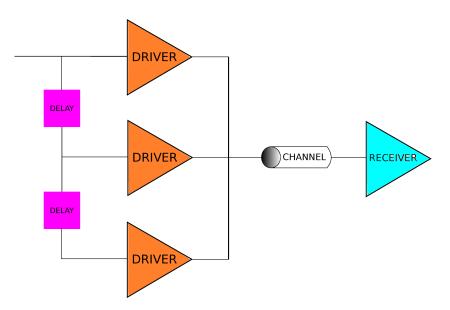

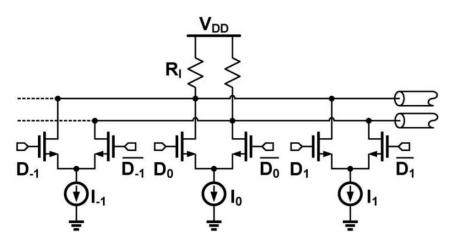

Fig. 2.1 shows the general structure of a transmitter with feed-forward equalization: delayed versions of the bit stream are fed to drivers with different strengths, thus implementing an FIR filter.

## 2.1 Choice of the Driver Topology

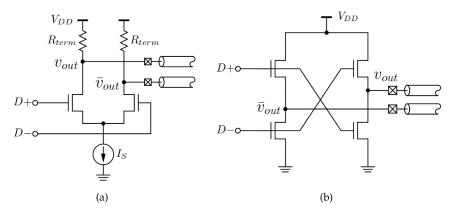

There are two possible ways to implement a high-speed driver: using a currentmode driver (Fig. 2.2(a)) or a current-mode driver (Fig. 2.2(b)). Each of the two implementations presents advantages and drawbacks. Current-mode drivers support higher data rates than voltage mode ones and have a low susceptibility to power supply noise, but they consume four times more power than the voltage-mode ones for the same output swing when a differential termination is used.

In order to demonstrate the last sentence, we will assume that the MOSFETs in Fig. 2.2 have an output resistance  $r_o = Z_0$ , where  $Z_0$  is the characteristic

Figure 2.1: General scheme of a serial link implementing FFE using driver slices.

Figure 2.2: (a) Differential current mode driver and (b) differential voltage mode driver topologies.

impedance of the channel (usually 500hms). An alternative to this assumption (which would in fact imply using very small MOSFETs for the driver) is to insert a termination resistance  $R_{term} = Z_0$  between the MOSFETs and the channel and using MOSFETs big enough so that their resistance can be assumed to be negligible when they are on. If one of this two assumptions is met, when using a differential termination  $2R = 2Z_0$ , for a current-mode driver one finds a differential output voltage that reads

$$V_{diff,out} = V_{out} - \bar{V}_{out}$$

=  $I_S(Z_0||3Z_0)\frac{2Z_0}{3Z_0} - I_S(Z_0||3Z_0)\frac{2Z_0}{3Z_0}$

=  $I_S \cdot Z_0$

from which it follows that the power dissipation for a current-mode driver is

$$P_D = V_{DD} \cdot I_S = \frac{2V_{DD}V_{diff,out}}{Z_0}$$

(2.1)

whereas under the same hypothesis for a voltage-mode driver one finds

$$I_{DD} = \frac{V_{DD}}{4Z_0}$$

$$V_{diff,out} = \frac{V_{DD}}{2}$$

(2.2)

from which it follows that the power dissipation is

$$P_{D} = I_{DD} V_{DD} = \frac{V_{DD} V_{diff,out}}{2Z_{0}}$$

(2.3)

Thus, from Eqs. 2.1,2.3 it follows that in order to achieve the same output voltage swing  $V_{diff,out}$  a current-mode driver consumes four times more power then a voltage-mode one [15].

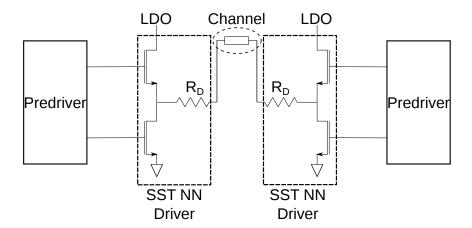

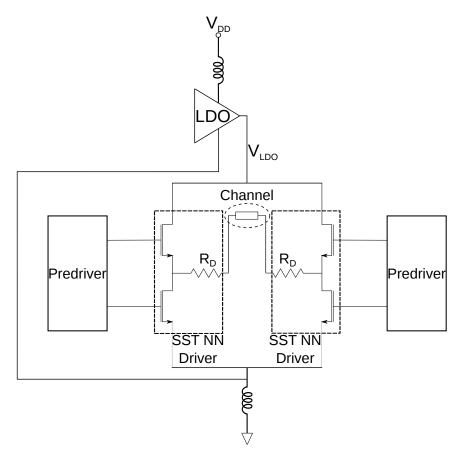

## 2.2 Driver Architecture

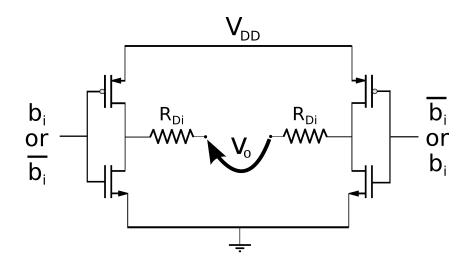

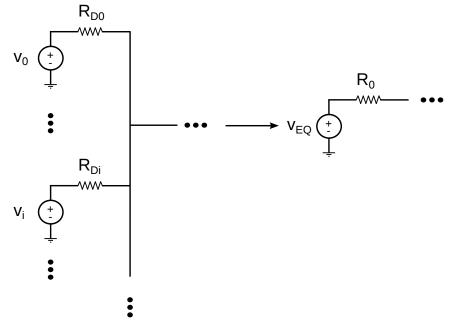

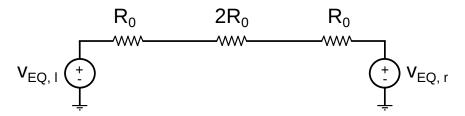

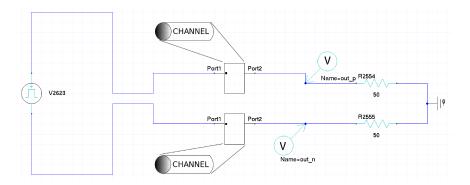

For the transmitter, a voltage mode architecture has been chosen in our project, because it consumes less power than a current mode for the same output swing, as stated in the previous section. Fig. 2.3 shows the general structure of a voltage-mode differential driver: two inverters are driven by bit  $b_i$  and to produce a differential voltage  $v_o$ . If the MOSFETs are large enough to have a negligible voltage drop when on, therefore negligible resistance, then impedance matching is implemented via the resistances  $R_{D_i}$ .

Fig. 2.3 is also the starting point to explain the basic principle of FFE applied to voltage mode drivers. A single driver can be split into many slices, and the same bit  $b_i$  of the serial data input can drive many of these slices, i.e. the

different drivers in Fig. 2.1 are each formed by many slices with the schematics of Fig. 2.3. This can be better understood in Fig. 2.4. The index i of a bit indicates the position in the bit stream.

When dividing the driver into slices, one must still guarantee impedance matching. In fact, when FFE is not implemented, only one slice might be used, and its output resistance should match  $R_0=50\Omega$ . If more slices are used, it has to be considered that the total resistance of all the slices in parallel should be 50 $\Omega$ , leading therefore to bigger values for  $R_{D_i}$  of each slice. This results in the following equation

$$\sum_{i} \left(\frac{1}{R_{D_i}}\right) = \frac{1}{R_0} \tag{2.4}$$

Under this assumption, one can find a closed-form expression for the output voltage  $v_0$  starting from an equivalent circuit for the half-driver as depicted in Fig. 2.5. In fact, it holds that

$$v_{eq} = \sum_{i} v_{i} \left( \frac{1 / \sum_{k \neq i} \frac{1}{R_{Dk}}}{R_{Di} + 1 / \sum_{k \neq i} \frac{1}{R_{Dk}}} \right)$$

=  $\sum_{i} v_{i} \left( \frac{1}{1 + R_{Di} \sum_{k \neq i} \frac{1}{R_{Dk}}} \right)$

=  $\sum_{i} v_{i} \left( \frac{1}{1 + R_{Di} \left( \sum_{k} \frac{1}{R_{Dk}} - \frac{1}{R_{Di}} \right)} \right)$  (2.5)

from where, recalling Eq. 2.4 one gets

Figure 2.3: General scheme of a voltage-mode transmitter.

Figure 2.4: Example of FFE implementation using slices (with schematics as in Fig. 2.3) put in parallel.

Figure 2.5: Thevenin equivalent for a half driver.

Figure 2.6: Thevenin equivalent for the whole driver with differential termination.

#### 2.2. DRIVER ARCHITECTURE

$$v_{eq} = \sum_{i} v_i \frac{R_0}{R_{Di}} \tag{2.6}$$

Considering that  $v_i$  can only be  $V_{DD}$  or 0 depending on the value of  $b_i$  (1 or 0) and on the connection with the driver, Eq. 2.6 can be rewritten as

$$v_{eq} = \sum_{i} \left( \frac{V_{DD}}{2} \pm \frac{V_{DD}}{2} b_i \right) \frac{R_0}{R_{Di}}$$

(2.7)

which holds true for both  $v_{eq,l}$  and  $v_{eq,r}$  just by swapping the  $\pm$  sign in front of the  $b_i$  term, since when  $v_{eq,l}$  is 1  $v_{eq,r}$  is 0 and vice-versa. Finally, one can write a close expression for  $v_0$  that reads

$$v_{o} = \frac{v_{eq,l} - v_{eq,r}}{2}$$

$$= \sum_{i} \left( \pm \frac{V_{DD}}{2} b_{i} \right) \frac{R_{0}}{R_{Di}}$$

$$= \frac{V_{DD}}{2} \cdot \sum_{i} \left( \frac{n_{i}}{M} \right) \cdot b_{i} \cdot sgn_{i}$$

(2.8)

where (see Fig. 2.4)  $n_i$  is the number of slides connected to the bit  $b_i$ , M is the number of total slices and  $sgn_i$  is the sign of  $b_i$  (i.e. putting  $b_i$  at the left or right part of Fig. 2.3 making the driver inverting or non-inverting). For the  $b_i$ , '1' corresponds to  $b_i = 1$  and '0' means  $b_i = -1$ .

Eq. 2.8 can be rewritten as

$$v_{o}[j] = \frac{V_{DD}}{2} \sum_{i} (w_{i} \cdot b_{i}[j]) = \frac{V_{DD}}{2} \sum_{i} (w_{i} \cdot data[j-i])$$

(2.9)

where *j* indicates a bit period and  $w_i$  is the strength of the slices connected to the *i*-th bit normalized to the full driver strength. From now on, we will refer to  $w_i$  as to the "weight" for the *i*-th tap. From Eq. 2.9 we see that the structure realizes an FIR filter, which implements a convolution between the bit stream (*data* [*j*]) and the tap vector  $w_i$ .

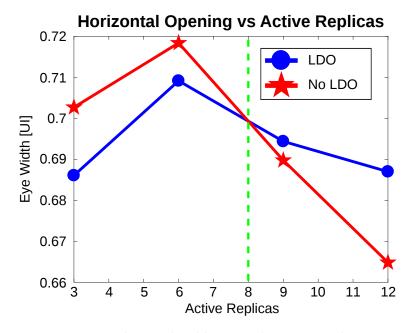

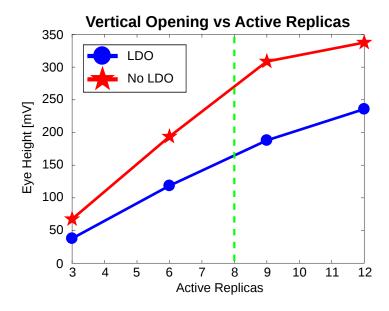

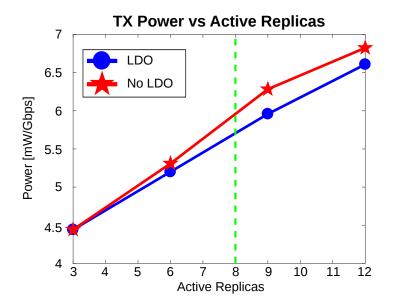

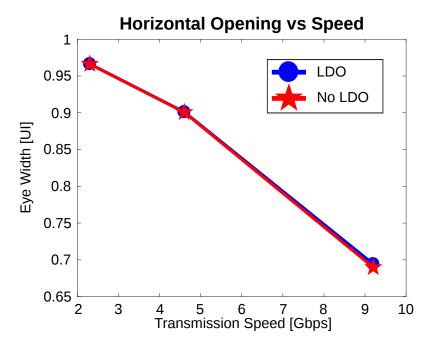

It should be noted that in order to obtain fine impedance tuning and compensate PVT (Process, Voltage and Temperature) variations, one does not strictly follow Eq. 2.4: the driver (divided in slices) is sized to obtain a resistance much larger than 50 $\Omega$ ; then many replicas of the structure are duplicated and the number of such replicas put in parallel is adjusted to match the 50 $\Omega$  target [42].

#### 2.3 Choice of the Equalization Taps

34

In this paragraph, we will cover the basic steps that are required to determine the weights  $w_i$  for FFE. The approach that we follow in our equalization process is the zero-forcing method [43]. Here the discussion will be at a tutorial level to bridge the gap between the theory in [43] and the actual hardware implementation (Figs. 2.3, 2.4). The goal is to minimize the distance between the desired response of the transmitter+channel (i.e. a signal without ISI) and that actually received; this is done via a Least Squares Minimization problem that reads

$$\min_{w_{ZFE}} ||z_{DES} - H_{CH} w_{ZFE}||^2$$

(2.10)

where  $w_{ZFE}$  is the weights vector  $[w_0, w_1, \ldots, w_i, \ldots, w_N]$  to be determined by the minimization problem and  $z_{DES}$  is the desired output response. In other words, if we consider a bit stream '10000', the transmitter will generate a sequence of pulses of height  $[w_0, w_1, \ldots, w_i, \ldots, w_N]$ , each one stimulating the channel. We want to set  $w_i$  in such a way that the receiver samples the original sequence '10000' without ISI, meaning that  $z_{DES} = [1,0,0,\ldots,0.]$ .  $H_{CH}$ is a matrix that rearranges the channel pulse response (*h*) in order to transform the convolution with the different pulses of height  $w_i$  into a matrix product. For example, if the channel pulse response is not null only for the first three samples and we decide to equalize with 5 post-cursor taps, then we have

$$H_{CH} = \begin{bmatrix} h_0 & 0 & 0 & 0 & 0 \\ h_1 & h_0 & 0 & 0 & 0 \\ h_2 & h_1 & h_0 & 0 & 0 \\ 0 & h_2 & h_1 & h_0 & 0 \\ 0 & 0 & h_2 & h_1 & h_0 \end{bmatrix}$$

(2.11)

If one wants to include also pre-cursor taps in the weights vector to be found, some slight changes have to be performed on both  $z_{DES}$  and  $H_{CH}$ . In fact, if one pre-cursor tap is to be considered, then  $z_{DES}$  becomes  $z_{DES} = [0,1,0,...,0]$ , whereas  $H_{CH}$ , in a case where the channel pulse response is not null only for one pre-cursor tap and the first three post-cursor taps with one pre-cursor and five post-cursor taps of equalization, is

-

$$H_{CH} = \begin{bmatrix} h_{-1} & 0 & 0 & 0 & 0 & 0 \\ h_0 & h_{-1} & 0 & 0 & 0 & 0 \\ h_1 & h_0 & h_{-1} & 0 & 0 & 0 \\ h_2 & h_1 & h_0 & h_{-1} & 0 & 0 \\ 0 & h_2 & h_1 & h_0 & h_{-1} & 0 \\ 0 & 0 & h_2 & h_1 & h_0 & h_{-1} \end{bmatrix}$$

(2.12)

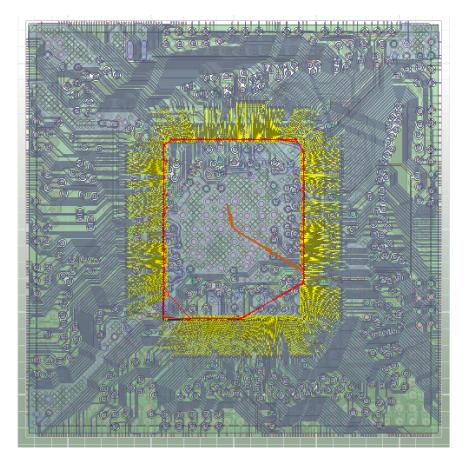

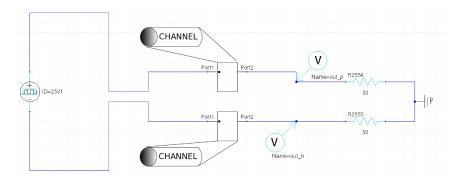

This approach can be extended to the number of pre-cursor and post-cursor equalization taps needed. The solution of the minimization problem introduced by Eq. 2.10 requires extracting the channel pulse response. In order to do this, the simulation setup shown in Fig. 2.7 is used. This setup is implemented in Ansys Electronic Desktop [44] and consists of a differential link with a pulse generator (with ideally steep rise and fall times) and an S-parameter block. This block changes from system to system and represents all the elements that compose the system after the transmitter.

#### 2.3. CHOICE OF THE EQUALIZATION TAPS

The solution of the Eq. 2.10 reads

$$w_{ZFE} = \left(H_{CH}^T \cdot H_{CH}\right)^{-1} \cdot H_{CH}^T \cdot z_{DES}$$

(2.13)

which is the well-known solution for the LS objective function of Eq. 2.10. The effect of a correct choice of equalization tap weights is sketched in Fig. 2.8.

Figure 2.7: Setup implemented in Ansys Electronic Desktop in order to extract the channel pulse response.

Figure 2.8: Pulse response when no feed-forward equalization is applied (top) and when ideal weights  $w_i$  are applied (bottom).

#### 2.4 Example with Realistic Channels

36

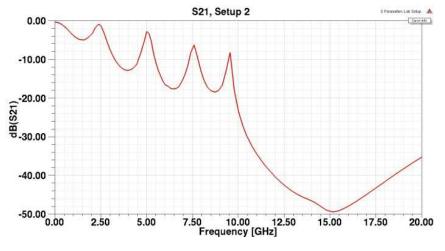

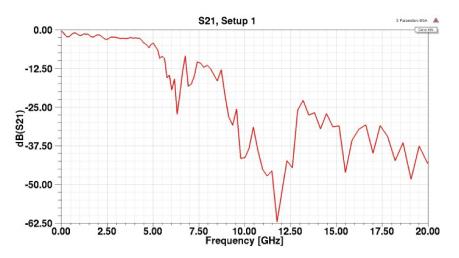

In this section, as an example, we analyze two different systems, which we will refer as "BGA system" and "Leadframe system". The Ball Grid Array (BGA) system is composed by a via, approximately 5 mm long, which connects the transmitter output signal to the package output, a BGA package, a Printed Circuit Board (PCB) and a cable (10 cm long). At the receiver end, the impedance is matched at 100 $\Omega$  differential and the differential output is measured via voltage probes. The Leadframe System is similar to the BGA one, but instead of a BGA package it uses a leadframe one. Figs. 2.9 and 2.10 show the  $S_{21}$  of both systems obtained via quasi-3D electromagnetic simulations with Ansys SIWave [45]: Fig. 2.11 shows how a BGA package looks like when analyzed with Ansys SIWave. As stated in the previous chapter, looking at  $S_{21}$  is a good way to understand which interference mechanism is the dominant one in the transmitting medium.

Figure 2.9:  $S_{21}$  of the Leadframe system.

Once the optimal weights have been found with Eq. 2.13, another verification about the correctness of the  $w_i$  is performed by simulating a structure equivalent to the system composed by transmitter, package, board and channel and evaluating the improvements obtained in the eye diagram. The software used to this end is again Ansys Electronic Desktop [44]. Fig. 2.12 illustrates a typical simulation setup: the only difference with respect to the structure presented in Fig. 2.7 is the use of a PRBS (Pseudo Random Bit Sequence) generator instead of a pulse generator. The PRBS generator offers the possibility to adapt its output based on equalization weights inserted by the user: in this case the vector  $w_{ZFE}$  obtained with Eq. 2.13. The low and the high voltage levels have been set to -450mV and 450 mV respectively, in order to analyze a mimic a possible scenario with a  $V_{DD}$  power domain of 900mV that directly supplies the driver slices. Thermal noise typical of MOSFETs in the transmitter has not been modeled and the channel is terminated with a 50 Ohm resistance.

One can evaluate how close the overall transmitter+channel response fits the wanted  $z_{DES}$  by checking it against the product  $H_{CH} \cdot w_{ZFE}$  (i.e. the overall response of the FFE+channel). This is shown in Fig. 2.13, which compares the

Figure 2.10:  $S_{21}$  of the BGA system.

Figure 2.11: Overview of a BGA516 package as imported in Ansys SIWave [45].

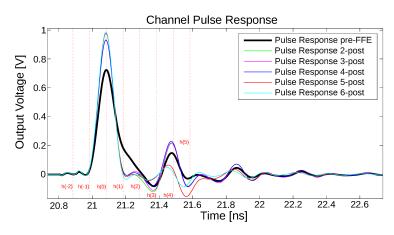

effect that equalizations with different number of taps has on the overall pulse response of the channel of Fig. 2.10. The weights used to obtain the curves in Fig. 2.13 are reported in tab. 2.1 In this particular case (consistent with the description above), only post-cursor taps were used, therefore the desired impulse channel response would be a 1 followed by a number of zeros equal to the post-cursor taps used. So, for a 4-taps equalization (main and three post-cursors) the desired channel pulse response would be  $z_{DES} = [1,0,0,0]$ . As said before, if pre-cursor taps are used, then the  $z_{DES}$  elements are shifted to the right by a number of places equal to the number of pre-cursor taps.

Figure 2.12: Setup implemented in Ansys Electronic Desktop in order to extract the obtain the eye diagram of the system. The only difference with respect to the structure presented in Fig. 2.7 is the use of a PRBS (Pseudo Random Bit Sequence) generator instead of a pulse generator.

Figure 2.13: Response of channel of Fig. 2.9 operating at 10Gbps along with responses after equalization for various numbers of taps, obtained with the simulation setup of Fig. 2.7.

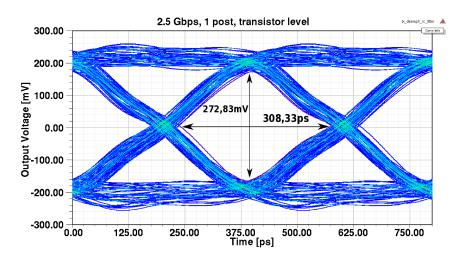

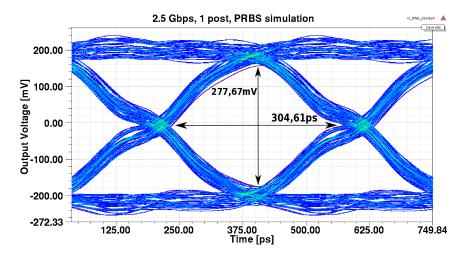

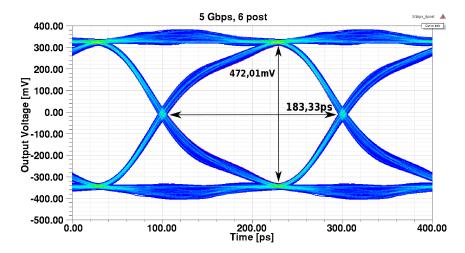

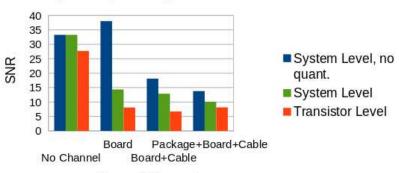

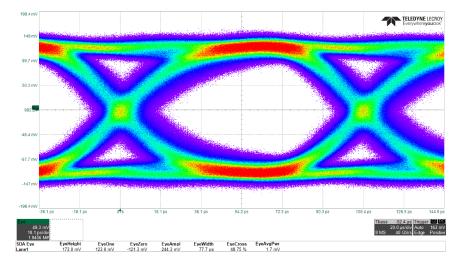

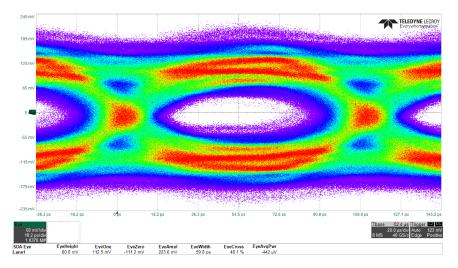

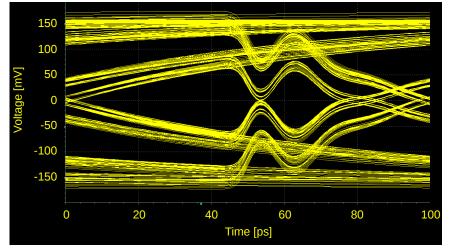

In order to confirm the validity of our simplified approach, in Figs. 2.14 and 2.15 two eye diagrams of the same system (at 2.5 Gbps) are shown. One is obtained with a PRBS generator and the other one with a transistor level model of the transmitter presented in [46], and their eye diagram parameters, eye width, eye height and Signal-to-Noise Ratio, are very similar, provided

|      | 2-post  | 3-post  | 4-post  | 5-post  | 6-post  |

|------|---------|---------|---------|---------|---------|

| w(0) | 0.8158  | 0.7885  | 0.7714  | 0.6374  | 0.577   |

| w(1) | -0.1842 | -0.1849 | -0.1795 | -0.1545 | -0.1526 |

| w(2) |         | 0.0266  | 0.0176  | 0.0101  | 0.0148  |

| w(3) |         |         | 0.0314  | 0.0622  | 0.0579  |

| w(4) |         |         |         | -0.1359 | -0.1392 |

| w(5) |         |         |         |         | 0.0585  |

Table 2.1: Tap weights for FFE for the curves reported in Fig. 2.13.

Figure 2.14: Eye diagram at 2.5 Gbps for the BGA System obtained with a transistor level simulation and one tap de-emphasis. The transmitter is described in [46].

Figure 2.15: Eye diagram at 2.5 Gbps for the BGA System obtained with a PRBS generator and one tap de-emphasis.

Figure 2.16: Eye diagram at 5 Gbps for the Leadframe System without Feed-Forward Equalization.

Figure 2.17: Eye diagram at 5 Gbps for the Leadframe System with six postcursor taps (main tap plus five post-cursors). The weights that generate this eye are  $w_0=0.8009$ ,  $w_1=0.0403$ ,  $w_2=-0.1018$ ,  $w_3=0.0395$ ,  $w_4=-0.0045$ ,  $w_5=-0.013$ .

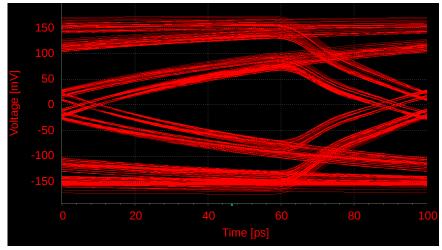

Figure 2.18: 15 Eye diagram at 10 Gbps for the Leadframe System without Feed-Forward Equalization.

Figure 2.19: Eye diagram at 10 Gbps for the Leadframe System with six postcursor taps (main tap plus five post-cursors). The weights that generate this eye are  $w_0=0.577$ ,  $w_1=-0.1526$ ,  $w_2=0.0148$ ,  $w_3=0.0579$ ,  $w_4=-0.1392$  and  $w_5=0.0585$ .

that the PRBS high and low levels are set to match the ones of the transistor level implementation. The eye width is the width of the horizontal histogram across the eye-crossing point, the eye height is the difference between high and low levels at the sampling time in which this difference is maximum and the Signal-to-Noise-Ratio is defined as difference between the average '1' and '0' levels divided by the sum of the standard deviations of the two levels at the center of the eye [44].

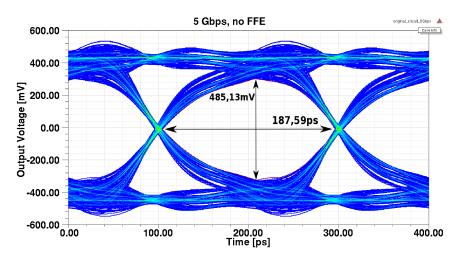

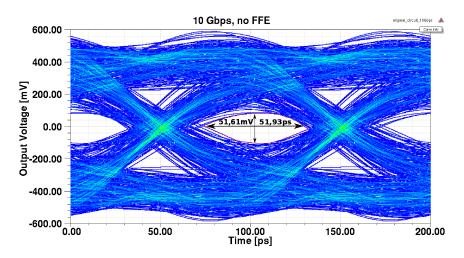

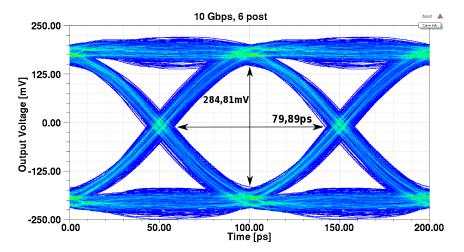

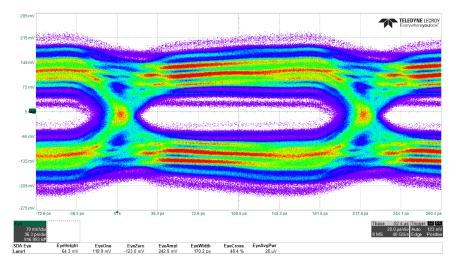

Since the system level design is performed before actually designing the transmitter at transistor level, in the following, for the 5 Gbps and the 10 Gbps cases only the PRBS source is used: we can follow this procedure since we have already proven the correctness of such a simulation approach In Figs. 2.14-2.15. Figs. 2.16, 2.17, 2.18 and 2.19 report the eye diagrams in such cases with and without equalization. For the 5 Gbps case, the improvement due to FFE is marginal, whereas to work at 10 Gbps with the Leadframe System, FFE is mandatory. Note that, at given  $V_{DD}$ , the inclusion of FFE lowers the high and low levels of the eye (e.g. 400mV vs. 300mV in Figs. 2.14 and 2.15): this is because when FFE is implemented, some slices will be driven by bits having opposite sign with respect to the main one, and this implies that the driver is not working at full strength. More precisely, the high and low levels are now shifted at  $\pm \frac{V_{DD}}{2} \sum_i w_i$

#### 2.5 Effect of Tap Quantization

Eq. 2.13 provides optimum tap weights, but one must also think at a real world implementation, which obviously implies quantizing these weights since each bit will be connected to a finite number of slices. This problem is peculiar to the voltage-mode transmitter divided in slices. In fact previous works already introduced equalization implemented with sliced drivers, but mainly in current mode logic [47]- [48], which makes equalization easier to implement with high granularity. In fact, as shown also in Fig. 2.20, the granularity of the weights is solely determined by the number of bits of the DAC controlling the current sources  $I_i$  of the taps.

Figure 2.20: Architecture of a current mode transmitter with 2-taps FFE (one pre-cursor and one post-cursor) as implemented in [49].

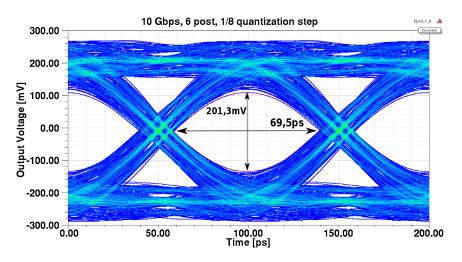

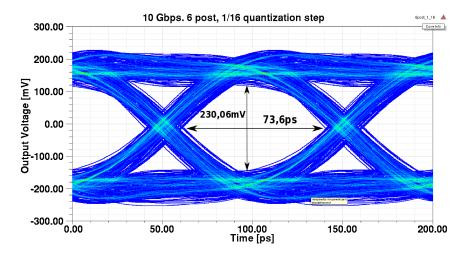

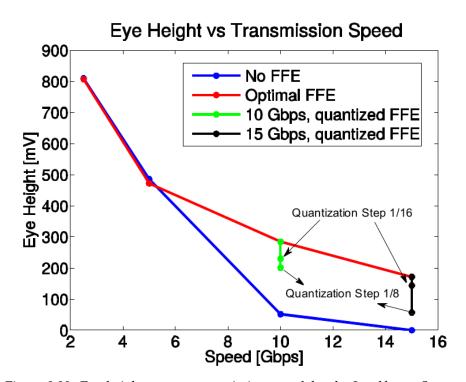

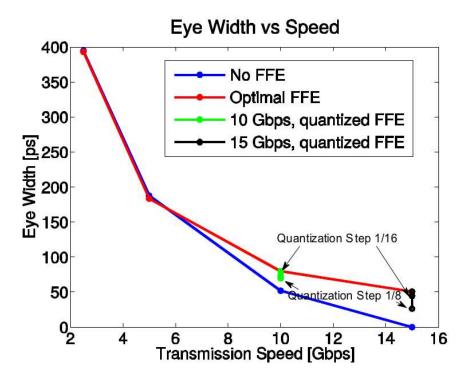

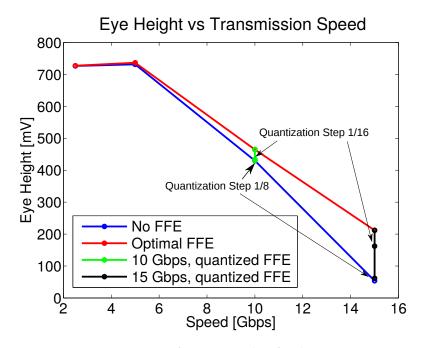

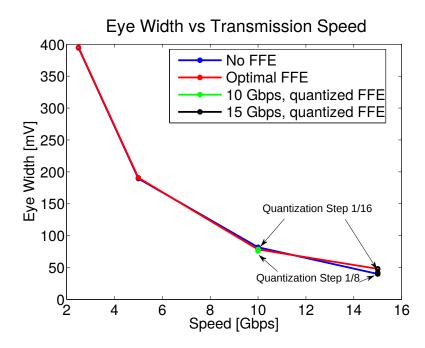

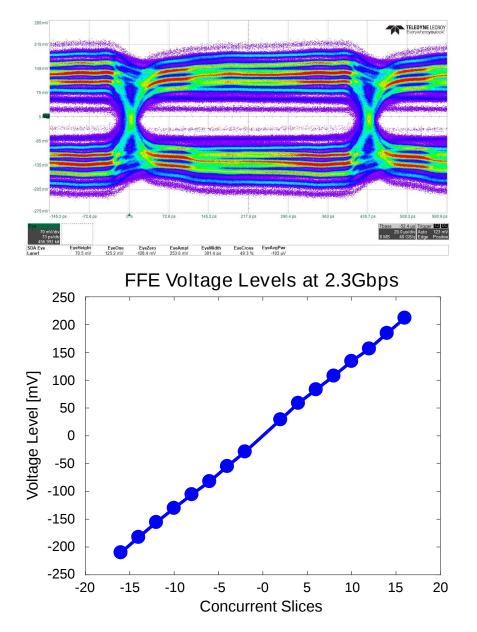

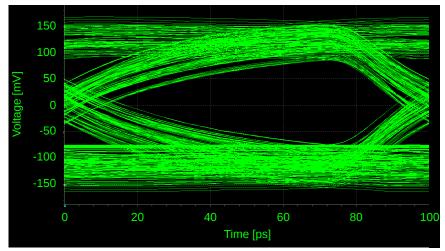

Here we analyze the effect of quantization with two different granularities, 8 and 16 levels (i.e. M=8 or M=16 as in Figure 2.4). These two different granularities offer quantization steps of 0.125 and 0.0625 respectively. Figs. 2.21 and 2.22 show the effect of quantization on the operation at 10 Gbps of Leadframe System when equalized with 6 post-cursor, which without quantization has already been shown in Figure 2.19. With 16 slices we obtain eye parameters very close to what is obtained from Eq. 2.13, whereas with 8 slices there is a degradation of the eye.

If the transmission speed gets even higher, then a higher number of taps is needed and the effect of quantization becomes more and more relevant. The eye parameters with and without FFE and including different granularity in the tap quantization are summarized in Figs. 2.23-2.26. We include in these figures also a hypothetical 15 Gbps situation that requires 9 taps for equalization when considering the Leadframe System (7 for the BGA System). Obviously, at this high speed, the main wall to climb would be the transistor level design of some critical blocks in se, as we will see in the next chapter. In Figs. 2.23-2.26 we see that FFE improves the eye height and width, although part of the improvement is lost if a too coarse granularity is used for the  $w_i$ .

Figure 2.21: Eye diagram at 10 Gbps for the Leadframe System with 6-post cursor taps and quantization step of  $\frac{1}{8}$ . The weights are  $w_0=0.625$ ,  $w_1=-0.125$ ,  $w_2=0$ ,  $w_3=0$ ,  $w_4=-0.125$  and  $w_5=0.125$ , which correspond to 5 slices connected to  $b_0$  while  $b_1$ ,  $b_4$  and  $b_5$  require one slice each.

Figure 2.22: Eye diagram at 10 Gbps for the Leadframe System with 6-post cursor taps and quantization step of  $\frac{1}{16}$ . The weights are  $w_0=0.5625$ ,  $w_1=-0.1875$ ,  $w_2=0$ ,  $w_3=0.0625$ ,  $w_4=-0.125$  and  $w_5=0.0625$ , which correspond to 9 slices connected to  $b_0$ , three connected to  $b_1$ , one slice connected to  $b_3$ , one to  $b_5$  and two to  $b_4$ .

Figure 2.23: Eye height versus transmission speed for the Leadframe System when not equalized, optimally equalized (Eq. 2.13) and when quantization (8 or 16 steps) is applied to  $w_i$ .

Figure 2.24: Same as for Fig. 2.23, but for the eye width.

Figure 2.25: Same as for Fig. 2.23, but for the BGA system.

Figure 2.26: Same as for Fig. 2.25, but for the eye width.

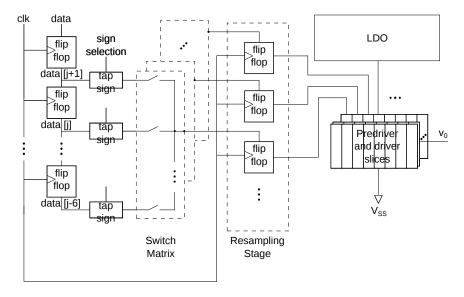

Figure 2.27: General architecture of the transmitter. Despite the fact that single data and clock line are shown in this picture, the architecture is fully differential and requires positive and negative versions of the clock and data signals. data[j+1] to data[j-6] are made available by the shift-register on the left side; the switch matrix is composed by 8x8 switches. We do not show explicitly the 8 slices of the driver that are hard-wired to the main tap but only the 8 that are connected to the switch matrix. The vector of 16 differential slices is duplicated K times to allow impedance tuning.

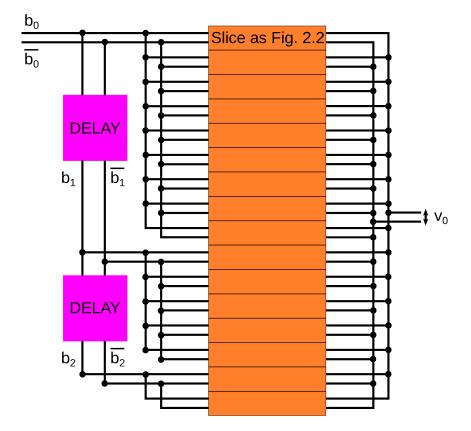

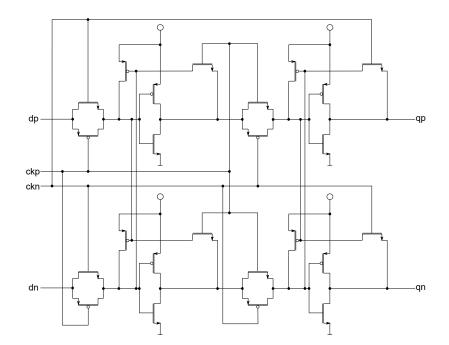

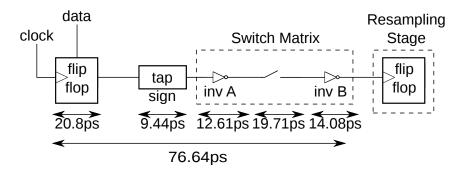

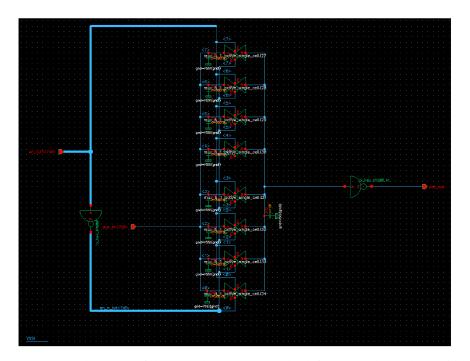

# 2.6 Architecture of the Transmitter

After the system level analysis performed in the previous sections, we can finally draw the architecture of the transmitter. The single blocks will be analyzed in detail in Chapter 3. The structure of the transmitter is sketched in Fig. 2.27. On the left, we see the shift-register that makes available to the driver (right side of the picture) the delayed version of the serial data (data) to be transmitted. We decided to have one pre-cursor tap because such a correction will not be possible with DFE at the receiver and one more post-cursor tap with respect to the analysis carried out in the previous chapter to prevent possible effects deriving from PVT corners not foreseen by such analysis. The main driver is composed by M=16 slices (whose structure is sketched in Fig. 2.28) and the switch matrix sketched at the center of Fig. 2.27 determines how many slices  $n_i$  are connected to the i-th delayed version of *data*. A "sign" (sgn<sub>i</sub>) is associated with each tap. Although not shown in Fig. 2.27, 8 slices over 16 are hard-wired to the main tap (i=0) with positive sign. Since the driver (Fig. 2.28) and all signals are differential, the selection of the sign is implemented by just swapping the two lines composing the signal. The re-sampling stage in Fig. 2.27 realigns the various signals at the output of the switch matrix reducing deterministic jitter.

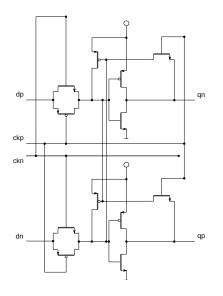

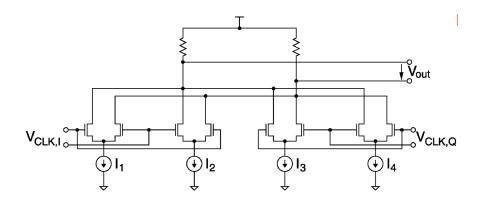

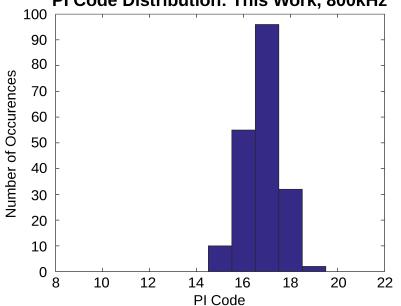

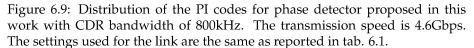

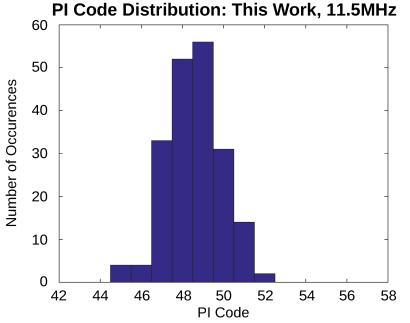

All the slices are connected in parallel to the output signal. The block of 16 slices is replicated K times in order to allow impedance matching, by activating