# Università degli studi di Udine

# Universal analytic model for tunnel FET circuit simulation

| Original                                                                                                                                                                                  |                            |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|

|                                                                                                                                                                                           |                            |  |

| <i>Availability:</i><br>This version is available http://hdl.handle.net/11390/1084219                                                                                                     | since 2021-03-23T12:02:32Z |  |

| Publisher:                                                                                                                                                                                |                            |  |

| Published<br>DOI:10.1016/j.sse.2014.12.002                                                                                                                                                |                            |  |

| <i>Terms of use:</i><br>The institutional repository of the University of Udine (http://air.uniud.it) is provided by ARIC services. The<br>aim is to enable open access to all the world. |                            |  |

Publisher copyright

(Article begins on next page)

# Universal analytic model for tunnel FET circuit simulation

Hao Lu<sup>a</sup>, David Esseni<sup>b</sup>, and Alan Seabaugh<sup>a</sup>

<sup>a</sup>Department of Electrical Engineering, University of Notre Dame, Notre Dame, IN 46556, United States. Email: {hlu1, seabaugh.1@nd.edu}. <sup>b</sup>Dipartimento di Ingegneria Elettrica Gestionale e Meccanica, University of Udine, Udine 33100, Italy. Email: <u>esseni@uniud.it</u>.

# Abstract

A simple analytic model based on the Kane-Sze formula is used to describe the current-voltage characteristics of tunnel field-effect transistors (TFETs). This model captures the unique features of the TFET including the decrease in subthreshold swing with drain current and the superlinear onset of the output characteristic. The model also captures the ambipolar current characteristic at negative gate-source bias and the negative differential resistance for negative drain-source biases. A simple empirical capacitance model is also included to enable circuit simulation. The model has fairly general validity and is not specific to a particular TFET geometry. Good agreement is shown with published atomistic simulations of an InAs double-gate TFET with gate perpendicular to the tunnel junction and with numerical simulations of a broken-gap AlGaSb/InAs TFET with gate in parallel with the tunnel junction.

Key words: Analytic model, band-to-band tunneling, compact model, SPICE model, steep-slope switch, tunnel field-effect transistor (TFET), tunneling.

#### I. INTRODUCTION

Tunnel field-effect transistors (TFETs) are candidates to compete with complementary metal-oxidesemiconductor (CMOS) FETs at low voltages because of their capability to achieve a subthreshold swing of less than 60 mV/decade at room temperature [1-3]. To build TFET circuits and make performance projections, it is of interest to develop simple, closed-form expressions for the drain current that contain the basic physics of the tunneling process and can be implemented in circuit simulators, e.g. SPICE.

Quite a few compact analytic models for the TFET have been developed [4-14]. References [4-9] employ a semianalytical solution of Poisson's equation in the channel region to model the channel charge [4] or to obtain the current-voltage characteristics [5-9]. These reports focus on particular TFET gate configurations, single-gate [5-7], double-gate [4, 8, 9, 11], or gate-all-around [10], or on specific aspects of the transport, such as the output characteristic at small drain biases [12, 13]. In most cases, the resulting expressions for the drain current are complex because the aim is to be predictive. The closest approach to our paper is that of Hong *et al.* [14] where the motivation is to develop an analytic model for use in circuit modeling. The resulting model gives good representation of the TFET characteristics, but is discontinuous and lacks an intuitive connection to the device physics.

Our intent has been to provide a simple and continuous equation set to describe the TFET currentvoltage (*I-V*) characteristics [15]. In this paper our model is extended into all operating regions and a capacitance model is added. The resulting model produces the *I-V* characteristics of the TFET at the level of an elementary MOSFET SPICE model. This model is shown to capture the essential features of the TFET predicted by more comprehensive numerical simulators. The generalized formulation does not rely on a specific TFET embodiment, e.g. lateral, vertical, single-gate, double-gate, gate-all-around, inversion-mode, enhancement-mode, gate-field aligned to the tunnel junction, or gate-field perpendicular to the tunnel junction, hence the model is widely configurable. The purpose is to provide a model which has the core physics, like in the level 1 MOSFET SPICE model, which can be easily implemented and fitted to experimental data, and allow elementary circuit design.

The paper is organized as follows. Section II describes the development of the model in the normal operating region, including the physics of the subthreshold and above threshold regions and how these regions are connected. In this section, the model is applied to the representation of a homojunction InAs double gate *p-i-n* TFET and a broken-gap AlGaSb/InAs vertical TFET. Section III extends the model into other operating regions by incorporating the ambipolar current and negative differential resistance (NDR). Section IV introduces a simple empirical capacitance model that is shown to capture the behavior of capacitances in TFETs. Section V demonstrates the use of the model in HSPICE and provides a simple charge pump circuit example.

# II. MODEL DEVELOPMENT

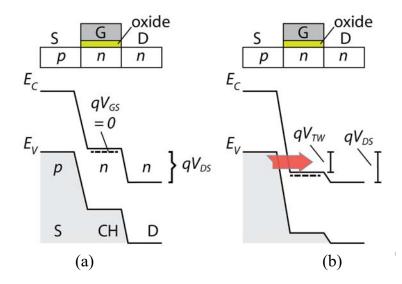

Tunnel FETs utilize an MOS-gate to control the band-to-band tunneling across a degenerate p-n junction. The schematic cross-section and energy band diagrams of an n-channel TFET in OFF and ON states are shown in Fig. 1. The device is normally off. When zero bias is applied to the gate, the conduction band minimum of the channel is located above the valence band maximum of the source, so band-to-band tunneling is suppressed. A tunneling window,  $qV_{TW}$ , opens up as the conduction band of the channel is shifted below the valence band of the source. Electrons in the valence band with energy in this tunneling window tunnel into empty states in the channel and the transistor is ON.

The central expression in the TFET model is an experimentally well-established equation for band-toband, Zener tunneling in p-n junctions [16, 17], the primary transport mechanism in tunnel transistors [1, 18]. The two-terminal Zener tunneling behavior is then generalized to three terminals by introducing physics-based expressions for the bias-dependent tunneling window and a dimensionless factor which accounts for the superlinear current onset in the output characteristic.

Fig. 1. Schematic cross-section and energy band diagram of an *n*-channel TFET when the device is biased in (a) OFF and (b) ON-state where the symbols are defined as follows:  $E_C$ , conduction band,  $E_V$ , valence band,  $V_{GS}$ , gate-source voltage,  $V_{DS}$ , drain-source voltage, and  $V_{TW}$ , tunneling window.

The signature feature of the TFET is the decrease in subthreshold swing with decreasing drain current, which is well established in both simulations [17, 19] and experiments [20, 21]. The model assumes that this behavior is caused by the exponential band tails that arise from imperfections and lattice disorder due to impurities, dopants, and phonons [22, 23] and extends into the band gap. This band tail, also known as the Urbach tail, represents a fundamental limit to the steepness that can be practically achieved [24] and thus becomes an adjustable element in the model. The subthreshold swing can be degraded by interface states and defects [25, 26]. While the physics of these effects are not included in the model, they presumably could be added as experiments reveal the generic aspects of these mechanisms.

# A. Kane-Sze Model

The TFET model is built on the expression for the current in a p+n+ tunnel junction described by the Kane-Sze tunneling formula, which is evaluated by integrating the product of charge flux and the

tunneling probability in the tunneling window, where the tunneling probability is calculated by applying the Wentzel-Kramers-Brillouin (WKB) approximation [27]

$$J_{D} = aV_{R}\xi \exp\left(-\frac{b}{\xi}\right),\tag{1}$$

where  $V_R$  is the reverse bias on the tunnel junction and physically accounts for the energy range,  $qV_R$ , over which the tunneling occurs,  $\xi$  is the maximum electric field in the reverse biased junction, and *a* and *b* are coefficients determined by the material properties of the junction, given by [1]:

$$a = \frac{q^{3}}{8\pi^{2}\hbar^{2}} \sqrt{\frac{2m_{R}^{*}}{E_{G}}}$$

$$b = \frac{4\sqrt{2m_{R}^{*}}E_{G}^{3/2}}{3q\hbar}$$

(2)

where  $m_R^* = (1/m_E^* + 1/m_H^*)^{-1}$  is the reduced effective mass, which is the average of the electron,  $m_E^*$ , and hole,  $m_H^*$ , effective masses,  $E_G$  is the semiconductor band gap, and  $\hbar$  is the reduced Planck's constant. The cross-sectional area of the junction, A, is the product of the channel thickness,  $t_{CH}$ , and the width of the channel, W.

The Kane-Sze expression, (1) is adapted to the following form,

$$J_{D} = a f V_{TW} \xi \exp\left(-\frac{b}{\xi}\right), \tag{3}$$

where the term  $V_R$  is split into two bias-dependent terms, f and  $V_{TW}$ . The first term, f, is a dimensionless factor controlling both the current onset and saturation versus  $V_{DS}$ , which is based on the Fermi occupancy probability of filled states in the valence band and unfilled states in the conduction band. The second term,  $V_{TW}$ , is the tunneling window, in volts, related to the crossing and uncrossing of the energy bands. Because of the smearing of the band edge caused by the exponential decay of the band-tails in the band gap as  $\sim e^{-|E-E_{C,F}|/E_{\theta}}$ , with  $E_{\theta}$  being the Urbach parameter [28], the tunneling window is assumed to increase exponentially with gate bias before the bands cross and then linearly after the bands have crossed.

The maximum electric field,  $\xi$ , is assumed to be linearly dependent on the gate-source bias and drainsource bias. In deriving (1), the tunneling process is approximated by a particle tunneling through a triangular barrier, with a slope given by the electron charge times the electric field  $q\xi$ . It has been shown by Hurks [26] that the maximum electric field can be used effectively here without taking the actual electric field distribution near the tunnel junction into account. Mathematically speaking, the detailed dependence of maximum electric field on  $V_{GS}$  and  $V_{DS}$  can always be approximated with a polynomial of certain degree. To make the model widely applicable to devices with different architectures, the maximum electric field is taken to be linearly dependent on  $V_{GS}$  and  $V_{DS}$  by dropping the second and higher order terms.

#### B. Electric Field

The maximum electric field in (3) is taken to be linearly dependent on gate-source bias,  $V_{GS}$ , and drain-source bias,  $V_{DS}$ ,

$$\xi = \xi_{\mathsf{O}} \left( 1 + \gamma_1 V_{\mathsf{DS}} + \gamma_2 V_{\mathsf{GS}} \right). \tag{4}$$

The electric field,  $\zeta_0$ , is the built-in electric field at the source-channel tunnel junction when zero bias is applied to both gate and drain terminals. Parameters,  $\gamma_1$  and  $\gamma_2$ , are linear coefficients with units of inverse volts. Increasing gate bias enhances the electric field at the source-channel junction by both enlarging the voltage drop (compared to the built-in voltage) and narrowing the tunneling barrier region. Increasing the drain bias has the same effect, but to a lesser degree because the drain field is screened by the gate electrode.

It is worth noting that the use of (4) remains physically meaningful even for broken-gap heterojunctions, where the concept of tunneling path and corresponding electric field can still be phenomenologically applied. Consideration of [29] shows that quantization effects along the transport direction produce a forbidden gap in the local density-of-states in the broken gap junction. Also note that there exists an electron energy barrier for tunneling in the AlGaSb/InAs heterojunction that approaches a rectangular barrier with nanometer-scale thickness in the ON-state. As a result, a current relation of the same form of (4) can be expected.

### C. Subthreshold Region

In the subthreshold region, the drain current of a tunnel FET depends exponentially on the gate bias, which is dominated by the exponential decrease of the tunneling window with  $V_{GS}$  below the threshold voltage. Accordingly, the tunneling window in the subthreshold region can be expressed by

$$V_{TW} \approx U \exp\left(\frac{V_{GS} - V_{TH}}{U}\right).$$

(5)

Here, the factor, U, called the Urbach factor, is given by

$$U = \gamma_0 U_0 + (1 - \gamma_0) U_0 \left( \frac{V_{GS} - V_{OFF}}{V_{TH} - V_{OFF}} \right),$$

$$U_0 = n k_B T/q$$

(6)

where  $\gamma_O$  is a parameter that controls how quickly the tunneling window closes with gate bias, *n* is the subthreshold ideality factor,  $V_{OFF}$  is the minimum  $V_{GS}$  voltage for which (6) is valid. The threshold voltage  $V_{TH}$  is defined as the gate-source bias at which the source valence-band-maximum equals the channel conduction-band-minimum (for an *n*-channel TFET). The expression (6) causes the subthreshold swing to decrease linearly with gate bias. When  $V_{GS}$  equals  $V_{OFF}$ , U is  $\gamma_O U_O$  and  $\gamma_O$  is a factor less than or equal to 1. When the gate bias is equal to the threshold voltage then U equals  $U_O$ .

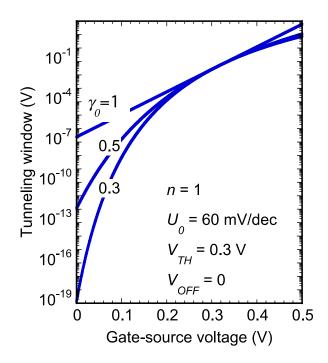

Fig. 2. Tunneling window, *V*<sub>TW</sub>, plotted as a function of gate-source voltage at room temperature in the subthreshold region.

The dependence of the tunneling window on gate-source bias is plotted in Fig. 2 for different  $\gamma_0$  values. When the parameters  $\gamma_0$  and *n* equal one, *U* reduces to  $U_0$  and the tunneling window is represented by a straight line in a semilog plot, corresponding to an exponentially closing tunneling window of 60 mV/decade. If  $\gamma_0$  is reduced below 1, the subthreshold swing decreases as the gate-source voltage decreases as can be observed in Fig. 2.

#### D. Above-Threshold Region

According to (3), the drain current in the above-threshold region should be directly controlled by the tunneling window. Above-threshold the tunneling window should be given by

$$V_{TW} \approx V_{GS} - V_{TH}, \tag{7}$$

which can be called the overdrive voltage.

#### E. Bridging the Subthreshold and Above-Threshold Regions

A function is needed to connect the subthreshold and above-threshold regions smoothly. Borrowing from Khakifirooz [30] and Wright [31] for MOSFETs, the following expression allows a continuous transition between the subthreshold and above-threshold regions,

$$V_{TW} = U \ln \left[ 1 + \exp\left(\frac{V_{GS} - V_{TH}}{U}\right) \right].$$

(8)

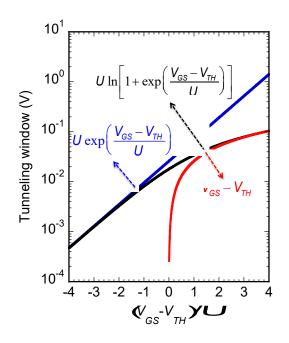

Fig. 3 shows the tunneling window as a function of gate-source voltage. When in the subthreshold region, the tunneling window grows exponentially with gate bias, but in the above-threshold region, it tends to a linear dependence on the gate bias. Whereas the mathematical expression in (8) is able to describe both exponential and linear regions in a single equation, there is no physical basis to justify its accuracy in the transition region,  $\sim 3nkT$ . This is also true in the MOSFET where this function has been effectively utilized to link subthreshold and linear regions [30, 31].

Fig. 3. Tunneling window,  $V_{TW}$ , plotted as a function of  $(V_{GS} - V_{TH})/U$ . When  $(V_{GS} - V_{TH})/U$  is larger than about 3,  $V_{TW}$  reduces to a linear function; when  $(V_{GS} - V_{TH})/U$  is smaller than about -3,  $V_{TW}$  reduces to an exponential function.

#### F. Superlinear Current Onset

The superlinear onset of the output characteristic is another signature behavior of the TFETs. De Michielis [13] showed that this characteristic arises from the Fermi occupancy of filled states in the source and unoccupied states in the channel. However, their expression for the drain current was not devised to account for the saturation of the drain current. This can be readily added as shown below. Initially the following simple function f, was used to describe both the superlinear onset and the saturation of drain current with drain-source bias,

$$f = \frac{1 - \exp\left(-\frac{V_{DS}}{\Gamma}\right)}{1 + \exp\left(\frac{V_{THDS} - V_{DS}}{\Gamma}\right)},\tag{9}$$

where  $\Gamma$  is a constant and  $V_{THDS}$  is the drain threshold voltage which corresponds to the minimum drain voltage needed to initiate the tunneling current [32]. When  $V_{DS}$  equals zero, then (9) and the tunneling current are zero. When  $V_{DS}$  becomes large, the function *f* tends to one.

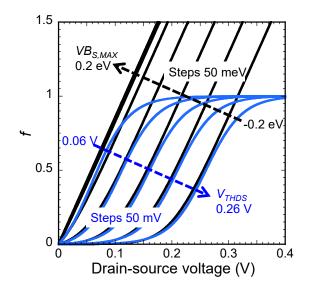

Fig. 4. Output characteristics for different source degeneracies based on occupation probability. The black lines are reproduced from [13]. The blue lines are based on (9), where  $\Gamma$  equals 32 mV.

In Fig. 4, (9) is plotted together with the expression from De Michielis [13]. In the low  $V_{DS}$  region the nonlinear turn-on of the drain current is well captured by (9). The superlinear onset degrades drastically as  $V_{THDS}$  becomes bigger than 0.1 V. At large  $V_{DS}$ , the function f saturates to 1, as desired.

In utilizing (9) to fit TFET simulations, it became apparent that the drain threshold voltage,  $V_{THDS}$ , should be made sensitive to gate bias. The drain threshold voltage has been found to increase linearly with gate voltage and then saturate at large  $V_{GS}$  [32]. To account for this dependence, the drain threshold voltage was modified to

$$V_{THDS} = \lambda \tanh \left( V_{GS} - V_{OFF} \right), \tag{10}$$

where  $\lambda$  is a constant with the unit of volts and the voltage inside the *tanh* function is normalized to 1 V. The hyperbolic tangent function is chosen because when  $V_{GS} - V_{OFF}$  is small,

$$\tanh\left(V_{GS} - V_{OFF}\right) \approx V_{GS} - V_{OFF},\tag{11}$$

and when  $V_{GS} - V_{OFF}$  is large,

$$\tanh\left(V_{\rm GS} - V_{\rm OFF}\right) \approx 1. \tag{12}$$

The function f in (9) then becomes

$$f = \frac{1 - \exp\left(-\frac{V_{DS}}{\Gamma}\right)}{1 + \exp\left(\frac{\lambda \tanh\left(V_{GS} - V_{OFF}\right) - V_{DS}}{\Gamma}\right)}$$

(13)

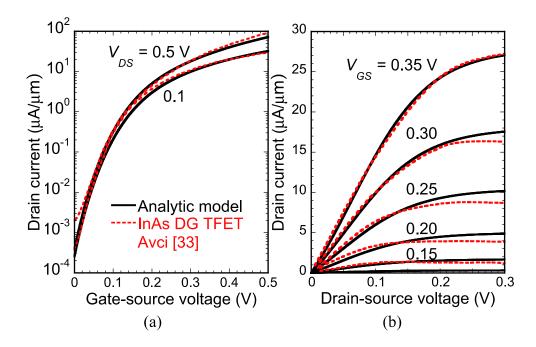

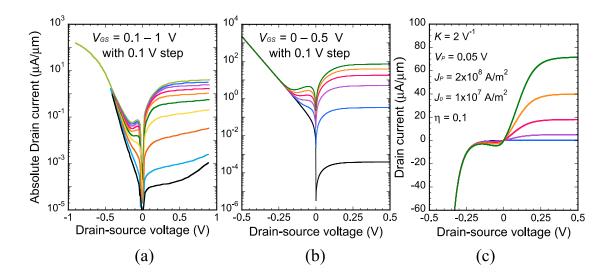

Fig. 5. Modeled and simulated transfer and output characteristics of a 20 nm InAs double-gate TFET. Atomistic simulation data are from [33].

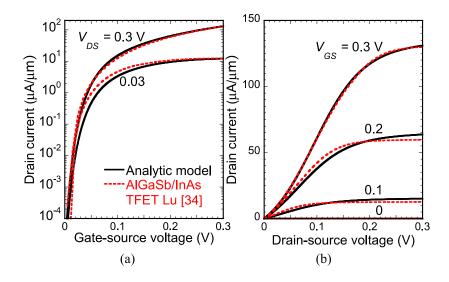

In order to test the ability of the model to represent TFET physics, we have fitted the model to two very different TFET embodiments. The first is a double-gate (DG) *p-i-n* InAs TFET [33] with characteristics predicted by an atomistic quantum-mechanical device simulator, and the second is an inline broken-gap AlGaSb/InAs TFET [34] as predicted by Synopsis technology computer-aided design (TCAD). The results are shown in Figs. 5 and 6. The channel length and width are 20 nm and 1  $\mu$ m, respectively. The device model parameters for both devices are shown in Table I. The model shows good agreement to the simulations. Excellent representation of the superlinear current onset is shown in Figs. 5(b) and 6(b). Close inspection of the bias dependence of the transconductances and conductances obtained by the model shows that the terminal dependences are not matched precisely owing to the generic nature of the tunneling description.

Fig. 6. Modeled and simulated transfer and output characteristics of a 20 nm broken-gap AlGaSb/InAs TFET. Numerical simulation data are from [34].

# TABLE I

|                                 | Range        | InAs DG TFET | AlGaSb/InAs TFET |

|---------------------------------|--------------|--------------|------------------|

| $E_{G}(eV)$                     | _            | 0.35         | 0.35             |

| m <sub>R</sub> *                | _            | 0.012        | 0.012            |

| $t_{CH}$ (nm)                   | _            | 5            | 5                |

| $\Gamma(V)$                     | 0 - 1        | 0.06         | 0.046            |

| Yo                              | 0 - 1        | 0.5          | 0.2              |

| $\gamma_1 (m^{-1})$             | 0 - 1        | 0.01         | 0.1              |

| $\gamma_2 (m^{-1})$             | 0 - 2        | 1.3          | 0.9              |

| $\xi_0$ (MV/cm)                 | 0.5 - 5      | 0.527        | 1                |

| $\lambda$ (V)                   | 0 - 1        | 0.19         | 0.32             |

| n                               | > 1          | 1.8          | 1.2              |

| $V_{OFF}\left(\mathrm{V} ight)$ | $0 - V_{DD}$ | 0.01         | 0                |

| $V_{TH}(\mathrm{V})$            | $0 - V_{DD}$ | 0.17         | 0.08             |

SUMMARY AND RANGE OF PARAMETERS IN THE MODEL

#### III. COMPLETE DC MODEL OF TFETS

The model discussed thus far is valid for positive  $V_{DS}$  and  $V_{GS}$ . Often in RF or transient simulations all four quadrants of the  $I_D$ - $V_{GS}$  characteristic may be needed. A tunnel FET is essentially a gated *p-i-n* tunnel diode. The asymmetrical source/drain junction causes tunnel FETs to have asymmetrical characteristics when the drain-source bias is reversed. When forwardly biased ( $V_{DS} < 0$ ), the band-toband tunneling current gradually gives way to the diffusion current as  $V_{DS}$  is decreased, resulting in NDR in the  $I_D$ - $V_{DS}$ . Also due to the asymmetrical doping, the tunnel junction shifts from the sourcechannel junction to drain-channel junction when the gate bias reverses, resulting in ambipolar conduction.

To fully make use of these features in circuit design, our model is extended into all four quadrants of operation: (1)  $I_D$  [ $V_{GS} > V_{OFF}$ ,  $V_{DS} > 0$ ], (2)  $I_D$  [ $V_{GS} < V_{OFF}$ ,  $V_{DS} > 0$ ], (3)  $I_D$  [ $V_{GS} < V_{OFF}$ ,  $V_{DS} < 0$ ], and (4)  $I_D$  [ $V_{GS} > V_{OFF}$ ,  $V_{DS} < 0$ ]. The equation set outlined in section II describes a model that operates in the first quadrant only. In this section, currents in the other three quadrants are defined.

# A. Second quadrant – the ambipolar current: $I_D [V_{GS} < V_{OFF}, V_{DS} > 0]$

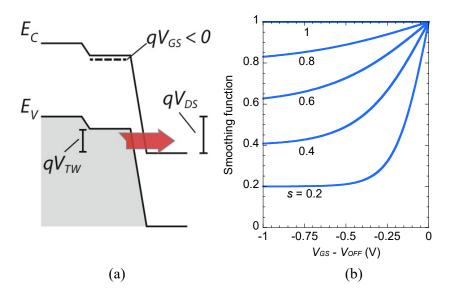

In the conventional mode of operation, the TFET tunnel current is suppressed when  $V_{GS}$  is low and then the tunnel window at the source junction is opened with positive  $V_{GS}$ . However the TFET can also turn on when gate bias is sufficiently negative. As shown in Fig. 7(a), when the gate bias is negative, the valence band maximum of the channel can be shifted above the conduction band minimum of the drain. Meanwhile, the drain-channel junction narrows as a result of the large voltage drop on the junction, leading to electrons tunneling from the channel into the empty states in the drain. Therefore, the tunneling window opens up gain, with the tunnel junction shifted from the source-channel junction to the drain-channel junction. When this happens the channel conduction changes from one carry type to another and the current is said to be ambipolar.

The ambipolar current is added to the model by copying the current for  $V_{GS} > V_{OFF}$  to  $V_{GS} < V_{OFF}$  and multiplying the current by a smoothing function,  $f_S$ . The term  $V_{GS}$  is replaced with  $V_{GS} - V_{OFF}$  in (4). To preserve the current continuity at  $V_{GS} = V_{OFF}$ ,  $f_S$  decreases from 1 when  $V_{GS} = V_{OFF}$  to an attenuation factor *s* when  $V_{GS} << V_{OFF}$ . As  $V_{GS} - V_{OFF}$  decreases from 0, as shown in Fig. 7b. The ambipolar drain current is given by

$$I_{D}(V_{GS} < V_{OFF}) = I_{D}(V_{GS} > V_{OFF}) f_{S}$$

$$f_{S} = \left(1 - (1 - s) \tanh\left(-\frac{V_{GS} - V_{OFF}}{s}\right)\right)$$

(14)

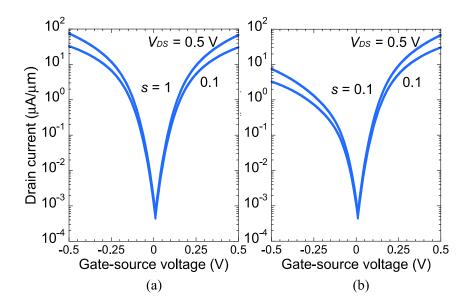

where *s* is an attenuation factor that sets the ratio of  $I_D$  ( $V_{GS} < V_{OFF}$ ) to  $I_D$  ( $V_{GS} > V_{OFF}$ ). In cases where the ambipolar current is suppressed, *s* can be set to a small number. The scaling factor, *s*, is taken to be dimensionless, because  $V_{GS} - V_{OFF}$  in the argument of the *tanh* function is considered to be normalized to 1 V. Fig. 8 shows the drain current plotted as a function of gate-source bias from -0.5 V to 0.5 V with *s* set to 1 and 0.1, respectively.

Fig. 7. (a) Band diagram showing ambipolar conduction of tunnel FETs. (b) Smoothing function plotted as a function of  $V_{GS} - V_{OFF}$  with *s* increasing from 0.2 to 1 in steps of 0.2.

Fig. 8. Transfer characteristics of 20 nm InAs DG TFET showing ambipolar current for s = 1 (a) and s = 0.1 (b).

# **B**. Third quadrant: $I_D [V_{GS} < V_{OFF}, V_{DS} < 0]$

The third quadrant is the least used region. In this region, the current is defined using the universal diode current equation.

$$J_{D} = -J_{0} \left( \exp\left(-\frac{V_{DS}}{nkT/q}\right) - 1 \right).$$

(15)

# C. Fourth quadrant – the negative differential resistance region: $I_D [V_{GS} > V_{OFF}, V_{DS} < 0]$

When the drain-source bias,  $V_{DS}$ , is negative, the source-channel junction is forward biased and behaves like a forward-biased tunnel diode. The NDR is included by modifying a model for the tunnel diode from Sze and Ng [35]

$$\boldsymbol{J} = \boldsymbol{J}_{\boldsymbol{P}} \frac{\boldsymbol{V}}{\boldsymbol{V}_{\boldsymbol{P}}} \boldsymbol{e}^{1-\frac{\boldsymbol{V}}{\boldsymbol{V}_{\boldsymbol{P}}}} + \boldsymbol{J}_{0} \left( \boldsymbol{e}^{\frac{\boldsymbol{V}}{\boldsymbol{n}\boldsymbol{k}\boldsymbol{T}/\boldsymbol{q}}} - 1 \right).$$

(16)

Adapted to the notation of our model, this formula becomes

$$J_{D} = -\left(-J_{P}\frac{V_{DS}}{V_{P}}K\left(V_{GS}-V_{OFF}\right)\exp\left(1+\frac{V_{DS}+\eta V_{GS}}{V_{P}}\right)+J_{0}\left(\exp\left(-\frac{V_{DS}}{nkT/q}\right)-1\right)\right).$$

(17)

16

Fig. 9. (a) Experimental forward and reverse bias drain current vs. drain-source voltage for InGaAs heterojunction TFET after Dewey [21], (b) logarithmic and (c) linear-scale, modeled forward and reverse-bias drain current vs. drain-source voltage for the 20 nm InAs DG TFET.

The five parameters  $J_P$ ,  $J_0$ ,  $V_P$ , K, and  $\eta$ , are fitting parameters. Parameter K has unit of V<sup>-1</sup>. The last parameter  $\eta$  is dimensionless. Parameter n shares the same value as n in (6). As shown in Fig. 9, the experimental NDR behavior is well captured by this semi-empirical equation. Series drain and source resistance can always be added as subcircuit parameters to account for parasitic resistances.

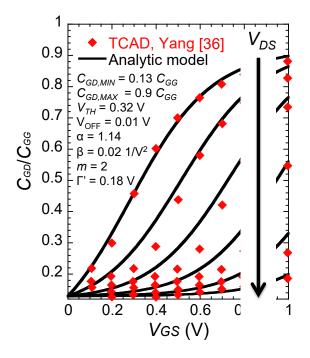

#### IV. CAPACITANCE MODEL

The partitioning of gate capacitances between the source and drain in TFETs is significantly different from CMOS, primarily due to the difference in the distribution of inversion charge [36]. Because  $C_{GS}$  is much smaller compared to  $C_{GD}$ , it is set as a constant. Noticing the similarity between the *f* function (Fig. 4) and the behavior of  $C_{GD}$  with increasing  $V_{GS}$  and  $V_{DS}$  (Fig. 10), the *f* function is modified to model the behavior of  $C_{GD}$

$$C_{GD} = C_{GD,MIN} + \left(C_{GD,MAX} - C_{GD,MIN}\right) \frac{\left(1 + \beta V_{GS}^{m}\right) - \exp\left(-\frac{V_{GS} - V_{OFF}}{\Gamma'}\right)}{1 + \exp\left(\frac{\left(V_{TH} + \alpha V_{DS}\right) - \left(V_{GS} - V_{OFF}\right)}{\Gamma'}\right)},$$

(18)

where  $C_{GD,MIN}$  and  $C_{GD,MAX}$  are the approximate minimum and maximum of  $C_{GD}$ . Parameters  $\alpha$ ,  $\beta$ ,  $\Gamma$ ', and *m* are fitting parameters, in which  $\alpha$  and *m* are dimensionless,  $\beta$  has unit of  $1/V^m$ , and  $\Gamma$ ' has unit of V.  $C_{GD}$  is set to  $C_{GD,MIN}$  in the other three quadrants.

Fig. 10. Modeled gate drain capacitance,  $C_{GD}/C_{GG}$ , vs.  $V_{GS}$  plotted against TCAD simulation data from [36] with  $V_{DS}$  increasing from 0 to 1 V in steps of 0.2 V.

#### V. CIRCUIT APPLICATION

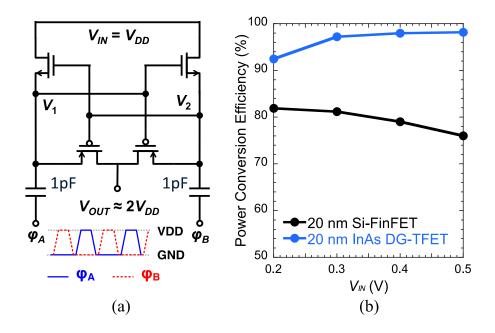

Fig. 11. (a) TFET charge pump circuit and (b) power conversion efficiency vs. input voltage for 20 nm HP Si FinFET [37] and InAs DG TFET.

The complete model is implemented as a subcircuit model in HSPICE 2013 and applied to a simple 4T charge pump circuit to demonstrate its use [38]. As shown in fig. 11(a), a charge pump circuit converts an input DC voltage to a higher output DC voltage. In this case, the output voltage is  $2V_{IN}$ . The circuit is simulated using modeled 20 nm InAs DG TFET as shown in Fig. 5 and Table I [33] and 20 nm HP Si FinFET PTM-MG model [37]. The power conversion efficiency, the ratio of output power to input power, for both devices is shown in Fig. 11(b). TFETs can achieve efficiency higher than 90% when  $V_{IN}$  is in the range of 0.2-0.5 V, whereas CMOS can only achieve efficiency higher than 70% when  $V_{IN}$  is 0.5 V.

## VI. CONCLUSION

An analytic n-channel TFET model for circuit simulation is shown to capture the current-voltage characteristics of the TFET in all operation regions. The model can be readily adapted to describe the p-channel TFET. The model accounts for bias dependent subthreshold swing, saturation, the superlinear

current onset, ambipolar conduction, and negative differential resistance. A simple behavioral capacitance model is also included. To justify the versatility of the model, the model is applied to two TFETs with distinctly different geometries, a planar double-gate InAs TFET and a vertical broken-gap AlGaSb/InAs TFET, and good agreement is demonstrated between the model and both simulations. The model is implemented in HSPICE and a simple charge pump circuit is simulated to prove the functionality of the model. The equation set enables the implementation of an entry-level TFET model for exploration of steep transistor circuits.

### Acknowledgement

This work was supported in part by the Center for Low Energy Systems Technology (LEAST), one of six SRC STARnet Centers, sponsored by MARCO and DARPA, and by a Fulbright Fellowship for D. Esseni.

#### REFERENCES

- [1] A. C. Seabaugh, and Q. Zhang, "Low-voltage tunnel transistors for beyond CMOS logic," *Proc. IEEE*, vol. 98, no. 12, pp. 2095-2110, Dec. 2010.

- [2] A. M. Ionescu, and H. Riel, "Tunnel field-effect transistors as energy-efficient electronic switches," *Nature*, vol. 479, no. 7373, pp. 329-337, Nov. 2011.

- [3] H. Lu and A. Seabaugh, "Tunnel field-effect transistors: State-of-the-art," *IEEE J. Electron Devices Soc.*, vol. 2, no. 4, pp. 44-49, Jul. 2014.

- [4] L. Zhang, X. Lin, J. He, and M. Chan, "An analytical charge model for double-gate tunnel FETs," *IEEE Trans. Electron Devices*, vol. 59, no. 12, pp. 3217-3223, Dec. 2012.

- [5] B. Bhushan, K. Nayak, and V. R. Rao, "DC compact model for SOI tunnel field-effect transistors," *IEEE Trans. Electron Devices*, vol. 59, no. 10, pp. 2635-2642, Oct. 2012.

- [6] N. Cui, L. Liu, Q. Xie, Z. Tan, R. Liang, J. Wang, and J. Xu, "A two-dimensional analytical model for tunnel field effect transistor and its applications," *Jpn. J. Appl. Phys.*, vol. 52, no. 4, pp. 044303-1–044303-6, Apr. 2013.

- [7] J. Wan, C. Le Royer, A. Zaslavsky, and S. Cristoloveanu, "A tunneling field effect transistor model combining interband tunneling with channel transport," *J. Appl. Phys.*, vol. 110, no. 10, pp. 104503-1–104503-10, Nov. 2011.

- [8] M. G. Bardon, H. P. Neves, R. Puers, and C. Van Hoof, "Pseudo-two-dimensional model for double-gate tunnel FETs considering the junctions depletion regions," *IEEE Trans. Electron Devices*, vol. 57, no. 4, pp. 827-834, Apr. 2010.

- [9] A. Pan, and C. O. Chui, "A quasi-analytical model for double-gate tunneling field-effect transistors," *IEEE Electron Device Lett.*, vol. 33, no. 10, pp. 1468-1470, Oct. 2012.

- [10] P. M. Solomon, D. J. Frank, and S. O. Koswatta, "Compact model and performance estimation for tunneling nanowire FET," in *Proc. 69th Dev. Res. Conf.*, 2011, pp. 197-198.

- [11] L. Liu, D. Mohata, and S. Datta, "Scaling length theory of double-gate interband tunnel field-effect transistors," *IEEE Trans. Electron Devices*, vol. 59, no. 4, pp. 902-908, Apr. 2012.

- [12] A. S. Verhulst, D. Leonelli, R. Rooyackers, and G. Groeseneken, "Drain voltage dependent analytical model of tunnel field-effect transistors," J. Appl. Phys., vol. 110, no. 2, pp. 024510-1– 024510-10, Jul. 2011.

- [13] L. De Michielis, L. Lattanzio, and A. M. Ionescu, "Understanding the superlinear onset of tunnel-FET output characteristic," *IEEE Electron Device Lett.*, vol. 33, no. 11, pp. 1523-1525, Nov. 2012.

- [14] Y. Hong, Y. Yang, L. Yang, G. Samudra, C.-H. Heng, and Y.-C. Yeo, "SPICE behavioral model of the tunneling field-effect transistor for circuit simulation," *IEEE Trans. Circuits Syst. II*, vol. 56, no. 12, pp. 946-950, Dec. 2009.

- [15] H. Lu, J. W. Kim, D. Esseni, and A. Seabaugh, "Continuous semiempirical model for the currentvoltage characteristics of tunnel FETs," in *Proc. 15th Int. Conf. ULIS*, 2014, pp. 25-28.

- [16] Y. Taur, C. H. Wann, and D. J. Frank, "25 nm CMOS design considerations," in *IEDM Tech. Dig.*, 1998, pp. 789-792.

- [17] Q. Zhang, W. Zhao, and A. Seabaugh, "Low-subthreshold-swing tunnel transistors," *IEEE Electron Device Lett.*, vol. 27, no. 4, pp. 297-300, Apr. 2006.

- [18] C. Zener, "A theory of the electrical breakdown of solid dielectrics," *Proc. R. Soc.*, vol. A145, no. 855, pp. 523-529, Jul. 1934.

- [19] U. E. Avci, S. Hasan, D. E. Nikonov, R. Rios, K. Kuhn, and I. A. Young, "Understanding the feasibility of scaled III-V TFET for logic by bridging atomistic simulations and experimental results," in *VLSI Symp. Tech. Dig.*, 2012, pp. 183-184.

- [20] S. H. Kim, H. Kam, C. Hu, and T.-J. K. Liu, "Germanium-source tunnel field effect transistors with record high Ion/IoFF," in VLSI Symp. Tech. Dig, 2009, pp. 178-179.

- [21] G. Dewey, B. Chu-Kung, J. Boardman, J. M. Fastenau, J. Kavalieros, R. Kotlyar, W. K. Liu, D. Lubyshey, M. Metz, N. Mukherjee, P. Oakey, R. Pillarisetty, M. Radosavljevic, H. W. Then, and R. Chau, "Fabrication, characterization, and physics of III-V heterojunction tunneling field effect transistors (H-TFET) for steep sub-threshold swing," in *IEDM Tech. Dig.*, 2011, pp. 33.6.1-33.6.4.

- [22] S. Agarwal and E. Yablonovitch, "Band-edge steepness obtained from esaki/backward diode current-voltage characteristics," *IEEE Tran. Electron Devices*, vol. 61, no. 5, pp. 1488-1493, May 2014.

- [23] M. H. Cohen, M. Y. Chou, E. N. Economou, S. John, and C. M. Soukoulis, "Band tails, path integrals, instantons, polarons, and all that," *IBM J. Res. Develop.*, vol. 32, no. 1, pp. 82-92, Jan. 1988.

- [24] M. A. Khayer and R. K. Lake, "Effects of band-tails on the subthreshold characteristics of nanowire band-to-band tunneling transistors," J. Appl. Phys., vol. 110, no. 7, pp. 074508-1-074508-6, Oct. 2011.

- [25] M. G. Pala, and D. Esseni, "Interface traps in InAs nanowire tunnel-FETs and MOSFETs-Part I: Model description and single trap analysis in tunnel-FETs," *IEEE Trans. Electron Devices*, vol. 60, no. 9, pp. 2795-2801, Sep. 2013.

- [26] D. Esseni, and M. G. Pala, "Interface traps in InAs nanowire tunnel-FETs and MOSFETs–Part II: Comparative analysis and trap-induced variability," *IEEE Trans. Electron Devices*, vol. 60, no. 9, pp. 2802-2807, Sep. 2013.

- [27] S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3rd ed. New York: Wiley-Interscience, 2007, p. 103.

- [28] G. A. M. Hurks, "On the modelling of tunnelling currents in reverse-biased p-n junctions," Solid State Electron., vol. 32, no. 8, pp. 665–668, May 1989.

- [29] S. O. Koswatta, S. J. Koester, and W. Haensch, "On the possibility of obtaining MOSFET-like performance and sub-60-mV/dec swing in 1-D broken-gap tunnel transistors," *IEEE Trans. Electron Devices*, vol. 57, no. 12, pp. 3222-3230, Dec. 2010.

- [30] A. Khakifirooz, O. M. Nayfeh, and D. Antoniadis, "A simple semiempirical short-channel MOSFET current-voltage model continuous across all regions of operation and employing only physical parameters," *IEEE Trans. Electron Devices*, vol. 56, no. 8, pp. 1674-1680, Aug. 2009.

- [31] G. T. Wright, "Threshold modelling of MOSFETs for CAD of CMOS-VLSI," *Electron Lett.*, vol. 21, no. 6, pp. 223-224, Mar. 1985.

- [32] K. Boucart, and A. M. Ionescu, "A new definition of threshold voltage in tunnel FETs," Solid State Electronics, vol. 52, no. 9, pp. 1318-1323, Sep. 2008.

- [33] U. E. Avci, R. Rios, K. Kuhn, and I. A. Young, "Comparison of performance, switching energy and process variations for the TFET and MOSFET in logic," in *VLSI Symp. Tech. Dig.*, pp. 124-125, 2011.

- [34] Y. Lu, G. Zhou, R. Li, Q. Liu, Q. Zhang, T. Vasen, S. D. Chae, T. Kosel, M. Wistey, H. Xing, A. Seabaugh, and P. Fay, "Performance of AlGaSb/InAs TFETs with gate electric field and tunneling direction aligned," *IEEE Electron Device Lett.*, vol. 33, no. 5, pp. 655-657, May 2012.

- [35] S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3re ed. New York: Wiley-Interscience, 2007, p. 430.

- [36] Y. Yang, X. Tong, L.-T. Yang, P.-F. Guo, L. Fan, and Y.-C. Yeo, "Tunneling field-effect transistor: Capacitance components and modeling," *IEEE Electron Dev. Lett.*, vol. 31, no. 7, pp. 752-754, Jul. 2010.

- [37] "PTM-MG model," [online], June 2012, Available: http://ptm.asu.edu.

- [38] X. Li, H. Liu, U. D. Heo, K. Ma, V. Narayanan, and S. Datta, "RF-powered systems using steepslope devices," presented at the NewCAS, Trois-Rivieres, Canada, 2014.